Inhalte

- Highlights

- 100G-Ethernet-PCB: Definition und Umfang

- 100G-Ethernet-PCB Regeln und Spezifikationen

- 100G-Ethernet-PCB Umsetzungsschritte

- 100G-Ethernet-PCB Fehlerbehebung

- Checkliste zur Lieferantenqualifizierung: So pruefen Sie Ihren Leiterplattenhersteller

- Glossar

- 6 zentrale Regeln fuer 100G-Ethernet-PCBs (Kurzuebersicht)

- FAQ

- Angebot / DFM-Review fuer 100G-Ethernet-PCBs anfordern

- Fazit

In der Welt des High-Speed-Networking ist ein 100G-Ethernet-PCB nicht einfach nur eine Standardleiterplatte mit engeren Toleranzen. Es ist ein praezise entwickeltes Bauteil, bei dem jeder Mikrometer Kupfer und jede Glasfaserlage die Signalintegritaet beeinflusst. Solche Boards sind fuer Datenraten von 100 Gigabit pro Sekunde ausgelegt, meist ueber vier Lanes mit 25 Gbit/s (NRZ) oder zwei Lanes mit 50 Gbit/s (PAM4). Bei diesen Frequenzen verhaelt sich eine Leiterbahn nicht mehr wie ein einfacher Draht, sondern wie eine Uebertragungsleitung, bei der dielektrische Verluste, Skin-Effekt und Via-Stubs das Augendiagramm bereits vor dem Empfaenger zerstoeren koennen.

Als Senior CAM Engineer bei APTPCB pruefe ich jedes Jahr Hunderte High-Speed-Designs. Der Unterschied zwischen einem funktionierenden 100G-Prototypen und einem ausgefallenen Board liegt oft in der Materialauswahl, also im Weg weg von Standard-FR4, und im physikalischen Management der Signaluebergaenge ueber Vias. Dieser Leitfaden erklaert die kritischen Design- und Fertigungsregeln, die fuer Erfolg im ersten Durchlauf notwendig sind.

Kurzantwort

Fuer ein funktionierendes 100G-Ethernet-PCB muessen Sie Insertion Loss und Return Loss ueber die Nyquist-Frequenz hinweg strikt kontrollieren, typischerweise 12,89 GHz bei 25G NRZ.

- Materialregel: Verwenden Sie kein Standard-FR4 (Tg170). Stattdessen brauchen Sie "Low Loss" oder "Ultra Low Loss"-Laminate, etwa Panasonic Megtron 6/7, Isola Tachyon oder Rogers RO4000, mit einem Dissipation Factor (Df) < 0,005.

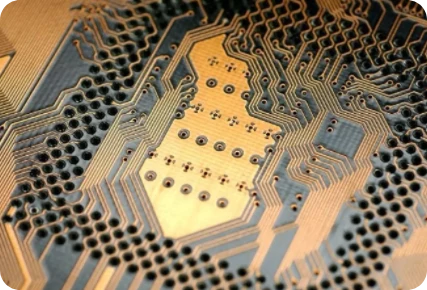

- Kritische Falle: Via-Stubs. Jeder ungenutzte Teil eines durchkontaktierten Vias wirkt wie eine Antenne und erzeugt Resonanzen, die das Signal zerstoeren. Sie muessen Backdrilling oder Blind-/Buried-Vias einsetzen, um Stubs auf < 10 mil (0,25 mm) zu reduzieren.

- Verifikation: Impedanzkontrolle allein reicht nicht aus. Sie brauchen Insertion-Loss-Messungen mit einem VNA (Vector Network Analyzer), um die reale Uebertragungsqualitaet zu bestaetigen.

- Kupferprofil: Spezifizieren Sie VLP- oder HVLP-Kupferfolie, um Verluste durch Skin-Effekt zu minimieren.

- Stackup: Verwenden Sie immer einen symmetrischen Lagenaufbau mit eng gekoppelten differentiellen Paaren ueber durchgehenden Ground-Planes.

Highlights

- Material ist entscheidend: Der Wechsel von Standard-FR4 auf Megtron 6 kann den Insertion Loss bei 12 GHz um mehr als 50 % verbessern.

- Backdrilling ist Pflicht: Bei Through-Hole-Steckverbindern auf dicken Backplanes ist Backdrilling die wirtschaftlichste Methode, um signalzerstoerende Stubs zu entfernen.

- Fiber-Weave-Effekt: Ab 25 Gbit/s pro Lane spielt das Glasgewebe eine Rolle. Nutzen Sie "Spread Glass" wie 1067 oder 1078 oder routen Sie mit leichtem Winkel, etwa 10 Grad, um Skew zu vermeiden.

- Oberflaechenfinish: ENIG oder Immersion Silver sind wegen ihrer Ebenheit vorzuziehen; HASL sollten Sie wegen der ungleichmaessigen Oberflaeche vermeiden.

- Toleranzen: 100G-Designs benoetigen eine Impedanzkontrolle von ±5 % oder besser, deutlich strenger als das uebliche ±10 %.

100G-Ethernet-PCB: Definition und Umfang

Ein 100G-Ethernet-PCB ist durch seine Faehigkeit definiert, IEEE 802.3bj (100GBASE-KR4) oder 802.3bm zu unterstuetzen. Obwohl sich "100G" auf den Gesamtdurchsatz bezieht, liegt die eigentliche Herausforderung in der Lane-Geschwindigkeit. Die meisten 100G-Implementierungen arbeiten mit 4 Lanes zu 25 Gbit/s im NRZ-Verfahren. Neuere Umsetzungen koennen 2 Lanes zu 50 Gbit/s mit PAM4 verwenden.

Die Physik von Signalen mit 25+ Gbit/s bedeutet, dass das Basismaterial selbst Signalenergie aufnimmt, also dielektrische Verluste verursacht, waehrend die Rauheit der Kupferoberflaeche den Widerstand bei hohen Frequenzen durch den Skin-Effekt erhoeht. Gleichzeitig schrumpft das Timing-Fenster auf Pikosekunden. Wenn die positiven und negativen Leiter eines differentiellen Paares nicht exakt laengengleich sind, oder wenn eine Leitung ueber Glasbuendel und die andere ueber Harz verlaeuft, treffen die Signale phasenverschoben ein. Das schliesst das Augendiagramm und fuehrt zu Datenfehlern.

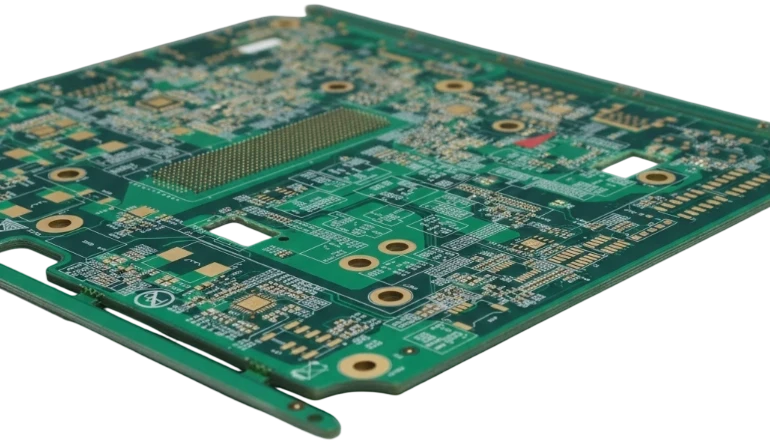

Bei APTPCB klassifizieren wir 100G-Boards als "Ultra High-Speed". Dadurch sind spezielle Laminationszyklen und Bohrprotokolle noetig, damit das physische Board mit den Simulationsdaten uebereinstimmt.

Technik-/Entscheidungshebel → Praktische Auswirkung

| Entscheidungshebel / Spezifikation | Praktische Auswirkung (Yield/Kosten/Zuverlaessigkeit) |

|---|---|

| Laminat-Df (Dissipation Factor) | Bestimmt direkt die maximal moegliche Leiterbahllaenge. Ein niedriger Df (<0,004) erlaubt laengere Traces, erhoeht aber die Materialkosten auf das Zwei- bis Dreifache gegenueber FR4. |

| Kupferfolien-Rauheit (VLP/HVLP) | Glaetteres Kupfer reduziert Insertion Loss bei hohen Frequenzen. Unverzichtbar fuer Strecken ueber 10 Inch bei 25 GHz. |

| Backdrilling (Stub-Entfernung) | Entfernt resonante Stubs. Fuer die Signalintegritaet zwingend, fuegt aber einen weiteren Bohrschritt hinzu und verlangt definierte Designabstaende. |

| Glasgewebe-Stil (1067/1078) | "Spread Glass" minimiert den Fiber-Weave-Effekt und damit Skew, ohne dass komplexes Zig-Zag-Routing erforderlich wird. |

100G-Ethernet-PCB Regeln und Spezifikationen

Ein 100G-Design verlangt strikte Regeln fuer Leiterbahngeometrie und Materialauswahl. Unten finden Sie die Standardspezifikationen, die wir bei APTPCB fuer die Fertigung empfehlen.

| Regel / Parameter | Empfohlener Wert | Warum das wichtig ist | Wie man es prueft |

|---|---|---|---|

| Differentielle Impedanz | 85Ω oder 100Ω ±5 % | Abweichungen verursachen Reflexionen (Return Loss) und senken die Signalleistung am Empfaenger. | TDR auf Coupons |

| Leiterbahnbreite / Abstand | 4 mil / 5 mil (min.) | Engere Kopplung reduziert Uebersprechen, die Breite beeinflusst den Skin-Effekt. | AOI und Mikroschliff |

| Via-Stub-Laenge | < 10 mil (0,25 mm) | Lange Stubs wirken wie Kerbfilter und zerstoeren bestimmte Frequenzen. | Roentgeninspektion und Backdrill-Tiefenprotokolle |

| Intra-Pair-Skew | < 5 mil (ca. 0,7 ps) | Phasenfehler schliessen das Augendiagramm. | CAD-Pruefung und VNA-Messung |

| Material Dk / Df | Dk ca. 3,0-3,6 / Df < 0,004 | Niedriges Dk senkt die Laufzeit, niedriges Df reduziert Daempfung. | Materialdatenblatt nach IPC-4101 |

| Referenzebene | Massives Kupfer (GND) | Unterbrechungen der Referenzebene erzeugen grosse Induktionsschleifen und EMI. | Sichtkontrolle der Gerberdaten |

Bei komplexen Stackups helfen unsere PCB-Stack-up-Services frueh im Designprozess dabei, zu bestaetigen, dass die Impedanzziele mit standardisierten Dielektrikdicken erreichbar sind.

100G-Ethernet-PCB Umsetzungsschritte

Die Umsetzung eines 100G-Designs ist ein linearer Prozess. Wer einen Schritt ueberspringt, produziert fast immer einen weiteren Board-Spin.

Umsetzungsprozess

Schritt-fuer-Schritt-Leitfaden

Waehlen Sie ein Low-Loss-Laminat wie Megtron 6. Definieren Sie die Layerzahl so, dass jede High-Speed-Signalebene eine benachbarte, durchgehende Ground-Referenz besitzt. Berechnen Sie die Leiterbahnbreiten fuer 100Ω.

Routen Sie 100G-Differentialpaare zuerst. Minimieren Sie Vias. Nutzen Sie Teardrops an Pads. Stellen Sie sicher, dass BGA-Breakout-Zonen Impedanz und Ground-Referenz erhalten. Vermeiden Sie 90-Grad-Winkel, verwenden Sie 45 Grad oder Boegen.

Fuehren Sie Post-Layout-Simulationen aus. Pruefen Sie NEXT/FEXT und Return Loss. Identifizieren Sie Via-Stubs ueber 10 mil und kennzeichnen Sie diese fuer Backdrilling in den Fertigungsunterlagen.

Senden Sie Gerberdaten mit spezifischen Drill-Charts fuer Backdrilling. Fordern Sie TDR-Reports und moeglichst SET2DIL- oder SPP-Tests an, um den Insertion Loss auf Coupons zu bestaetigen.

100G-Ethernet-PCB Fehlerbehebung

Auch bei gutem Design koennen im Test Probleme auftreten. Hier sind typische Fehlerbilder bei 100G-Links und geeignete Gegenmassnahmen.

1. Hohe Bitfehlerrate (BER)

Wenn der Link aufgebaut wird, aber Pakete verliert, liegt das Problem oft an Jitter oder Uebersprechen.

- Ursache: Leiterbahnen verlaufen zu nah an aggressiven Stoersignalen wie DC-DC-Wandlern oder anderen High-Speed-Takten.

- Fix: Erhoehen Sie den Abstand zwischen differentiellen Paaren. Die 3W-Regel reicht oft nicht, zielen Sie besser auf 4W oder 5W. Pruefen Sie die Referenzebene auf Luecken.

2. Signaldaempfung (Insertion-Loss-Fehler)

Das Signal ist am Empfaenger zu schwach.

- Ursache: Die Leiterbahn ist fuer das gewaehlte Material zu lang oder das Kupfer zu rau.

- Fix: Wenn die Trace nicht kuerzer werden kann, wechseln Sie auf ein Material mit niedrigerem Df, zum Beispiel von Megtron 4 auf Megtron 7. Spezifizieren Sie HVLP-Kupferfolie.

3. Resonanz / Kerbfiltereffekt

Das Signal sieht bei niedrigen Frequenzen gut aus, verschwindet aber bei einer bestimmten hohen Frequenz, etwa 12 GHz.

- Ursache: Via-Stubs. Der ungenutzte Teil des Vias schwingt bei einer Viertelwellenlaenge der Signalfrequenz.

- Fix: Implementieren Sie Backdrilling, um den Stub zu entfernen. Stellen Sie sicher, dass die Backdrill-Toleranz eng gehalten wird, typischerweise ±0,05 mm.

Checkliste zur Lieferantenqualifizierung: So pruefen Sie Ihren Leiterplattenhersteller

Nicht jeder PCB-Hersteller kann 100G-Anforderungen sicher beherrschen. Nutzen Sie diese Checkliste, um Ihren Lieferanten vor der Bestellung zu bewerten.

- Verfuegt der Hersteller ueber interne VNA-Testfaehigkeiten? Das ist essenziell, um Insertion Loss und nicht nur Impedanz zu verifizieren.

- Wie hoch ist die Standardtoleranz fuer die Backdrill-Tiefe? Sie sollte ±0,1 mm oder besser sein, idealerweise ±0,05 mm.

- Werden High-Speed-Laminate auf Lager gehalten? Fragen Sie gezielt nach Megtron 6/7, Rogers 4350 oder gleichwertigen Materialien. Muss erst bestellt werden, verlaengert sich die Lieferzeit.

- Kann der Hersteller eine Leiterbahnbreiten-Toleranz von +2/-2 mil einhalten? Standard ist oft ±20 %, High-Speed benoetigt haeufig ±10 % oder ±0,5 mil.

- Wird auf jeder Charge eine Mikroschliffanalyse durchgefuehrt? Damit lassen sich Plattierungsdicke und Dielektrik-Konstanz bestaetigen.

- Wird fuer die Backdrill-Pruefung Roentgeninspektion eingesetzt? So sehen Sie, ob zu tief gebohrt oder zu viel Stub stehen gelassen wurde.

Glossar

- Insertion Loss: Verlust an Signalleistung entlang der Leiterbahn, gemessen in dB. Hoehere Frequenzen verlieren mehr Leistung.

- Return Loss: Anteil des Signals, der durch Impedanzabweichungen zur Quelle reflektiert wird. Hoher Return Loss bedeutet schlechte Signalintegritaet.

- Backdrilling: Fertigungsverfahren, bei dem ein etwas groesserer Bohrer den ungenutzten Barrel-Anteil eines Through-Hole-Vias entfernt und so Reflexionen reduziert.

- PAM4 (Pulse Amplitude Modulation 4-level): Modulationsverfahren mit zwei Bits pro Symbol. Es verdoppelt die Datenrate gegenueber NRZ bei gleicher Bandbreite, verlangt aber ein besseres Signal-Rausch-Verhaeltnis.

- Skew: Zeitdifferenz zwischen positivem und negativem Signal eines differentiellen Paares. Hoher Skew wandelt das differentielle Signal in Common-Mode-Rauschen um.

6 zentrale Regeln fuer 100G-Ethernet-PCBs (Kurzuebersicht)

| Regel / Richtlinie | Warum das wichtig ist (Physik/Kosten) | Zielwert / Aktion |

|---|---|---|

| Via-Stubs entfernen | Stubs wirken wie Antennen und erzeugen starke Resonanzen mit Signalverlust bei 25 GHz und mehr. | Backdrill auf < 10 mil Reststub. |

| Low-Loss-Material einsetzen | Standard-FR4 absorbiert bei hohen Frequenzen zu viel Signalenergie. | Df < 0,005 (z. B. Megtron 6) |

| Durchgehende Referenzebene | Rueckstrom muss direkt unter dem Signal fliessen. Luecken erzeugen Induktionsspitzen. | Massives Kupfer ohne Splits unter Traces. |

| Ground-Vias nahe Signal-Vias | Bietet dem Rueckstrom einen Pfad, wenn das Signal die Lage wechselt. | GND-Via innerhalb von 30 mil zum Signal-Via platzieren. |

| Enge Impedanzkontrolle | Abweichungen erzeugen Reflexionen. 100G verzeiht deutlich weniger als 10G. | ±5 % Toleranz statt Standard ±10 %. |

| Fiber Weave minimieren | Periodische Glasbuendel erzeugen Skew, wenn eine Leitung ueber Glas und die andere ueber Harz verlaeuft. | Spread Glass oder Zig-Zag-Routing verwenden. |

FAQ

Q: Kann ich Standard-FR4 fuer 100G-Ethernet-PCBs verwenden?

A: Im Regelfall nein. Fuer extrem kurze Traces unter 1 Inch kann es eventuell funktionieren, aber Standard-FR4 hat einen zu hohen Dissipation Factor von etwa 0,02 und verursacht bei 12 bis 14 GHz zu starke Daempfung. Nutzen Sie Mid-Loss- oder Low-Loss-Materialien wie Isola FR408HR oder Panasonic Megtron 6.

Q: Wie gross ist der Kostenunterschied zwischen Standard-FR4 und High-Speed-Materialien?

A: High-Speed-Laminate wie Megtron 6 kosten typischerweise das Zwei- bis Dreifache von Standard-FR4. Der Materialpreis ist jedoch oft nur ein kleiner Teil des gesamten Boardwerts, waehrend die Kosten eines fehlgeschlagenen Prototyps deutlich hoeher sind.

Q: Brauche ich Blind- und Buried-Vias fuer 100G?

A: Nicht zwingend. Blind- und Buried-Vias reduzieren Stubs sehr gut, erhoehen aber Laminationszyklen und Kosten. Backdrilling ist bei Through-Hole-Vias eine guenstigere Alternative und erreicht fuer 100G-Anwendungen oft aehnlich gute Ergebnisse.

Q: Wie berechne ich die korrekte Impedanz fuer 100G?

A: Sie koennen einen Impedanzrechner verwenden, aber fuer 100G empfehlen wir die Abstimmung mit Ihrem Fertiger. Wir arbeiten mit Field-Solver-Software wie Polar SI9000, die Harzgehalt, Kupferrauheit und Etchback beruecksichtigt und daraus die exakte Leiterbahnbreite ableitet.

Q: Welches Oberflaechenfinish ist fuer 100G-PCBs am besten?

A: ENIG oder Immersion Silver sind die bevorzugten Optionen. Sie bieten eine sehr ebene Oberflaeche fuer die Bauteilmontage und fuegen den Leiterbahnen keine ungleichmaessige Dicke hinzu wie HASL, das die Impedanz stoeren kann.

Q: Wie lang darf eine 100G-Leiterbahn auf einem PCB maximal sein?

A: Das haengt vom Material ab. Auf Standard-FR4 liegen Sie moeglicherweise nur bei 2 bis 3 Inch. Mit Megtron 6 sind oft 10 bis 15 Inch oder mehr erreichbar, abhaengig von Retimer- oder Treiberfaehigkeiten. Die exakte Reichweite muss simuliert werden.

Angebot / DFM-Review fuer 100G-Ethernet-PCBs anfordern

Sind Sie bereit, Ihr High-Speed-Design in die Fertigung zu bringen? Bei APTPCB sind wir auf Advanced PCB Manufacturing fuer Data-Center- und Networking-Anwendungen spezialisiert.

Fuer ein praezises Angebot und ein DFM-Review senden Sie uns bitte:

- Gerber-Dateien (bevorzugt RS-274X)

- Fabrication Drawing mit Drill-Chart und Backdrill-Lagen

- Stackup-Details wie Layerzahl, gewuenschtes Material und Impedanzanforderungen

- Netlist (IPC-356) fuer die elektrische Verifikation

Fazit

Bei einem 100G-Ethernet-PCB muessen Sie das Denken vom "Verbinden von Punkten" auf das "Beherrschen von Uebertragungsleitungen" umstellen. Wenn Sie die richtigen Low-Loss-Materialien waehlen, Via-Stubs konsequent per Backdrilling kontrollieren und enge Impedanztoleranzen einhalten, laeuft Ihr Board auch bei 25 Gbit/s pro Lane und darueber hinaus zuverlaessig.

Behandeln Sie die Signalintegritaet nicht als Nebenthema. Binden Sie Ihren Fertiger frueh ein, um Stackup und Designregeln gemeinsam zu validieren.

Unterzeichnet, das Engineering-Team von APTPCB