Inhalte

- Highlights

- 48V-VRM-Leitfaden: Definition und Umfang

- 48V-VRM-Leitfaden Regeln und Spezifikationen

- 48V-VRM-Leitfaden Umsetzungsschritte

- 48V-VRM-Leitfaden Fehlerbehebung

- Checkliste zur Lieferantenqualifizierung: So pruefen Sie Ihren Leiterplattenhersteller

- Glossar

- 6 zentrale Regeln fuer 48V-VRM-Boards (Kurzuebersicht)

- FAQ

- Angebot / DFM-Review fuer 48V-VRM-Boards anfordern

- Fazit

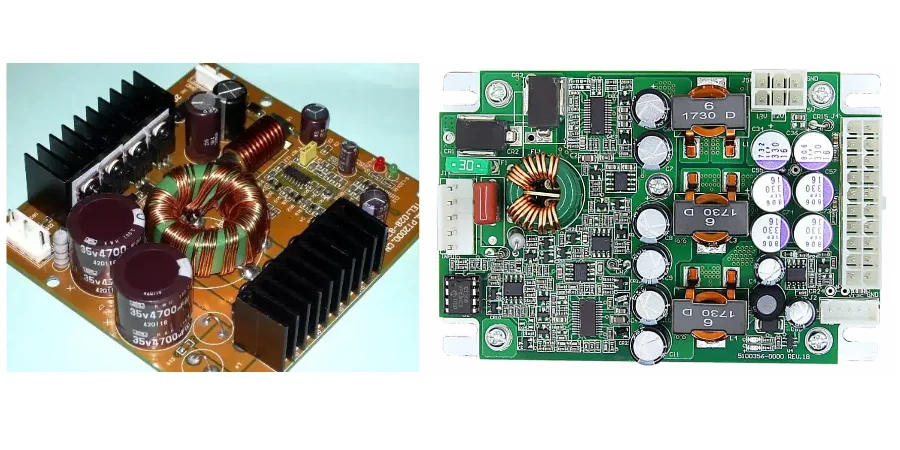

Ein 48V-VRM-Leitfaden ist fuer Entwickler unverzichtbar, die hocheffiziente Power-Delivery-Networks (PDN) fuer Rechenzentren, EV-Systeme im Automotive-Bereich und Telekom-Infrastruktur auslegen. Da der Leistungsbedarf von KI-Beschleunigern und High-Performance-Computing stark steigt, wechselt die Branche von 12V auf 48V, um die Verteilverluste nach $I^2R$ deutlich zu senken. Ein 48V-Voltage-Regulator-Module-(VRM)-Board wandelt diese Busspannung auf die sehr niedrigen Spannungen der Prozessoren herunter, oft unter 1V. Dadurch muss das PCB extreme Stromdichten und thermische Belastungen sicher beherrschen.

Kurzantwort

Die Entwicklung und Fertigung eines 48V-VRM-Boards erfordert strikte thermische und elektrische Regeln, damit es nicht zu katastrophalen Ausfaellen kommt. Hier die Management-Zusammenfassung fuer die direkte Anwendung:

- Kupfergewichts-Regel: Standardmaessiges 1oz-Kupfer reicht selten aus. Verwenden Sie auf Innenlagen 2oz bis 4oz Heavy Copper, um hohe Stroeme bei minimalem Spannungsabfall zu fuehren.

- Thermische Hauptfalle: Zu geringe Dichte an Thermal-Vias unter MOSFETs und Induktivitaeten ist die haeufigste Ursache fuer Ausfaelle im Feld. Sie brauchen einen direkten thermischen Pfad zu Chassis oder Kuehlkoerper.

- Layout-Kritikalitaet: Minimieren Sie die Schleifenflaeche des Switching Node (SW), um EMI und Spannungsspitzen zu reduzieren.

- Materialauswahl: Nutzen Sie High-Tg-FR-4 (>=170°C) oder spezielle thermische Laminate, wenn die Baugruppe dauerhaft ueber 100°C arbeitet.

- Verifikationsmethode: Fuehren Sie vor der Fertigung eine DC-Drop-Analyse (IR-Drop) durch, damit der Spannungsabfall ueber den Power Planes unter 1% bleibt.

- Fertigungskontrolle: Stimmen Sie die Etch-Factor-Kompensation mit Ihrem CAM-Ingenieur ab. Dickes Kupfer braucht angepasste Artwork-Korrekturen, damit die Leiterbahnbreite erhalten bleibt.

- Bestueckungshinweis: Das Stencil-Design muss die benoetigte Lotpastenmenge fuer grosse Leistungskomponenten beruecksichtigen. Oft sind 100% Aperturoeffnung oder Step-Stencils notwendig.

Highlights

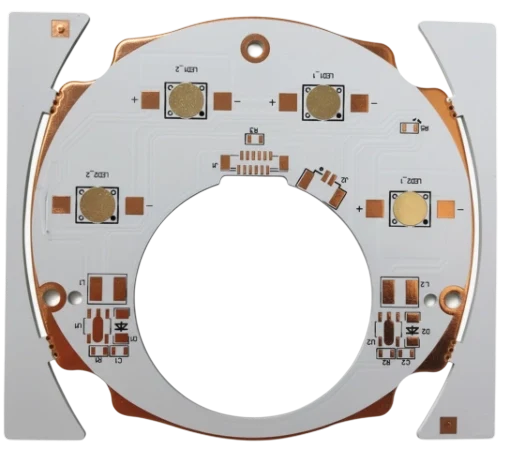

- Thermisches Management ist entscheidend: In 48V-Systemen fungiert das PCB selbst als wesentlicher Waermepfad. Der Lagenaufbau muss auf maximalen vertikalen Waermetransport optimiert werden.

- Heavy-Copper-Fertigung: Die Verarbeitung von 3oz+ Kupfer erfordert spezielle Aetz- und Laminationsverfahren, um Hohlraeume und Delamination zu vermeiden.

- Impedanzkontrolle: Auch wenn es primaer ein Power-Board ist, muessen Gate-Drive-Signale und Rueckkopplungsschleifen impedanzkontrolliert ausgelegt werden, damit kein Fehltriggern auftritt.

- Creepage und Clearance: 48V gilt als SELV, aber hohe Bauteildichte erhoeht das Risiko von Ueberschlaegen. Daher gelten die Abstandsregeln nach IPC-2221 konsequent.

- Symmetrie ist wichtig: Unsymmetrische Heavy-Copper-Stackups fuehren im Reflow zu deutlichem Verzug und spaeter zu Bestueckungsfehlern.

48V-VRM-Leitfaden: Definition und Umfang

Der Wechsel auf 48V wird durch die Physik getrieben: Wenn die Spannung von 12V auf 48V vervierfacht wird, sinkt der erforderliche Strom fuer dieselbe Leistung auf ein Viertel, und die ohmschen Verluste sinken auf ein Sechzehntel. Damit verlagert sich die Last jedoch auf das VRM-Board, das jetzt hoehere Eingangsspannungen und dichter gepackte Leistungsstufen verarbeiten muss.

Ein vollstaendiger 48V-VRM-Leitfaden deckt den gesamten Weg von der Stackup-Auswahl bis zur finalen Bestueckung ab. Dazu gehoeren Materialien, die thermischer Alterung widerstehen, Layouts mit geringer parasitaerer Induktivitaet und Fertigungsprozesse, die dicke Kupferschichten verarbeiten koennen, ohne die feinen Steuersignale zu beeintraechtigen.

Bei APTPCB sehen wir oft, dass Designs nicht am Schaltplan scheitern, sondern daran, dass das physische PCB die thermischen und mechanischen Belastungen nicht tragen kann. Die folgende Matrix zeigt, wie einzelne Fertigungsentscheidungen die Endleistung des VRM beeinflussen.

Technik-/Entscheidungshebel → Praktische Auswirkung

| Entscheidungshebel / Spezifikation | Praktische Auswirkung (Yield/Kosten/Zuverlaessigkeit) |

|---|---|

| Kupfergewicht (2oz vs. 4oz+) | Mehr Kupfer senkt Widerstand und Waerme, erhoeht aber Kosten sowie Mindestwerte fuer Leiterbahn/Abstand und erschwert damit das Routing. |

| Material-Tg (150°C vs. 180°C) | Hohes Tg (180°C) ist fuer VRMs wichtig, um Z-Achs-Ausdehnung und Barrel Cracking bei Temperaturzyklen zu vermeiden. |

| Via-Technologie (mechanisch vs. Laser) | Laser-Microvias erhoehen die Dichte um Controller-ICs, treiben aber die Kosten. Mechanische Vias sind robust fuer Thermal-Pfade, benoetigen jedoch mehr Flaeche. |

| Oberflaechenfinish (ENIG vs. Immersion Silver) | ENIG bietet plane Pads fuer Fine-Pitch-Controller. Immersion Silver ist elektrisch sehr gut fuer schnelles Schalten, verlangt aber sorgfaeltige Handhabung. |

48V-VRM-Leitfaden Regeln und Spezifikationen

Beim 48V-VRM-Design reichen einfache Faustregeln nicht aus. Sie brauchen konkrete Werte, die aus IPC-Normen und Thermosimulationen abgeleitet sind. Unten stehen die wichtigsten Spezifikationen, die wir fuer robuste Heavy-Copper-PCB-Fertigung empfehlen.

| Regel | Empfohlener Wert | Warum das wichtig ist | Wie man es prueft |

|---|---|---|---|

| Min. Leiterbahnbreite (Power) | Berechnung fuer $\Delta T < 10^\circ C$ | Verhindert, dass Leiterbahnen wie Sicherungen wirken. Auch bei 48V koennen Stroeme sehr hoch sein (z. B. 50A+). | IPC-2152-Rechner / Saturn PCB Toolkit |

| Abstand (48V) | Min. 0,25 mm (10 mil) | Verhindert Ueberschlaege und Leckstroeme, auch bei Schwankungen der Loetstoppmaske. | DRC im CAD |

| Thermal-Via-Raster | 1,0 bis 1,2 mm Grid | Optimiert die Waermeverteilung, ohne die mechanische Stabilitaet des PCBs zu schwaechen. | Sichtkontrolle der Gerber-Bohrdaten |

| Loetstoppsteg | Min. 4 mil (0,1 mm) | Verhindert Loetbruecken an Fine-Pitch-MOSFETs und Gate-Treibern. | CAM-Engineering-Review (DFM) |

| Dielektrikdicke | Min. 3 mil (Prepreg) | Sichert die Durchschlagfestigkeit zwischen den Lagen. | Stackup-Report des Fertigers |

| Plattierungsdicke | Class 3 (durchschnittlich 25µm) | Sichert die Via-Zuverlaessigkeit unter thermischer Ausdehnung. | Mikroschliffanalyse |

48V-VRM-Leitfaden Umsetzungsschritte

Der Weg vom Schaltplan zum realen Board braucht einen disziplinierten Ablauf. Die hohen Stroeme bedeuten, dass ein Layoutfehler nicht nur ein Signalintegritaetsproblem ist, sondern ein reales Sicherheitsrisiko.

Umsetzungsprozess

Schritt-fuer-Schritt-Leitfaden

Waehlen Sie einen symmetrischen Stackup mit Heavy Copper, z. B. 2oz/2oz/2oz/2oz. Setzen Sie ein High-Tg-Material wie Isola 370HR oder gleichwertig ein. Stimmen Sie Impedanzprofile frueh mit dem Fertiger ab.

Setzen Sie die Eingangskondensatoren so nah wie moeglich an die MOSFETs, um die Schleifeninduktivitaet zu minimieren. Nutzen Sie breite Polygone fuer Hochstrompfade. Halten Sie den Switching Node kompakt, um abgestrahlte EMI zu verringern.

Vernaehen Sie Ground-Planes und Power-Pads mit Thermal Vias. Nutzen Sie bei Hochstrom-Vias keine Thermal-Relief-Speichen, sondern solide Anbindung fuer maximalen Waermetransport und passen Sie dafuer das Loetprofil an.

Fuehren Sie eine DC-Drop-Simulation durch, um die Spannungsstabilitaet zu bestaetigen. Reichen Sie Gerber fuer ein DFM-Review ein, damit Heavy-Copper-Abstandsregeln geprueft werden, meist 8 bis 10 mil Mindestabstand bei 3oz Kupfer.

48V-VRM-Leitfaden Fehlerbehebung

Auch bei gutem Design koennen im Test oder in der Anlaufphase Probleme auftreten. Hier sind typische Fehlerbilder bei 48V-VRM-Boards und passende Gegenmassnahmen.

1. MOSFET-Ueberhitzung

- Symptom: Die Leistungsstufe faellt aus oder das System schaltet thermisch ab.

- Root Cause: Zu wenig Kupferflaeche oder fehlende Thermal Vias unter dem Exposed Pad.

- Fix: Vergrössern Sie die Kupferflaechen auf allen angebundenen Lagen. Nutzen Sie bei Bedarf High Thermal Conductivity PCB-Materialien oder Metal-Core-Designs.

2. Uebermaessiges Voltage Ringing (EMI)

- Symptom: Hochfrequentes Rauschen am Ausgang oder nicht bestandener EMI-Test.

- Root Cause: Hohe parasitaere Induktivitaet in der Eingangsschleife oder am Switching Node.

- Fix: Ruecken Sie keramische Eingangskondensatoren naeher an die FETs. Stellen Sie sicher, dass direkt unter den High-dI/dt-Schleifen eine durchgehende, ununterbrochene Ground-Plane liegt.

3. Risse in Loetstellen

- Symptom: Intermittierende Ausfaelle nach Temperaturzyklen.

- Root Cause: CTE-Mismatch zwischen Bauteil und PCB, oft verstaerkt durch Materialien mit niedrigem Tg.

- Fix: Wechseln Sie auf High-Tg-Materialien (Tg > 170°C) und stellen Sie sicher, dass die Via-Plattierung IPC-Class-3-Anforderungen erfuellt.

Checkliste zur Lieferantenqualifizierung: So pruefen Sie Ihren Leiterplattenhersteller

Nicht jeder Hersteller kann die Heavy-Copper- und Thermik-Anforderungen eines 48V-VRM-Boards sicher abdecken. Nutzen Sie diese Checkliste bei der Auswahl eines Partners wie APTPCB.

- Heavy-Copper-Faehigkeit: Kann der Hersteller 3oz, 4oz oder 6oz Kupfer mit praeziser Leiterbahngeometrie aetzen?

- Thermisches Management: Werden MCPCB oder Embedded-Coin-Technologien angeboten, wenn das Projekt sie braucht?

- Lagenregistrierung: Welche Layer-to-Layer-Toleranz wird erreicht? Das ist fuer hochlagige Power-Boards entscheidend.

- Mikroschliffanalyse: Werden Mikroschliffe jeder Charge erstellt, um Plattierungsdicke und Wandqualitaet zu bestaetigen?

- Hi-Pot-Test: Kann der Hersteller Hochspannungspruefungen zur Verifikation der Dielektrik-Festigkeit durchfuehren?

- Impedanzkontrolle: Werden TDR-Reports fuer Gate-Drive- und Kommunikationsleitungen bereitgestellt?

Glossar

- VRM (Voltage Regulator Module): Ein Buck-Wandler, der Spannung, z. B. von 48V auf 1V, fuer Prozessoren heruntersetzt.

- PDN (Power Delivery Network): Der gesamte Leistungspfad von der Quelle zur Last, einschliesslich Leiterbahnen, Planes und Kondensatoren.

- Tg (Glass Transition Temperature): Die Temperatur, bei der das Substrat von steif zu weich uebergeht. Hohes Tg ist fuer Power-Boards essenziell.

- DCR (DC Resistance): Der Gleichstromwiderstand eines Bauteils oder einer Leiterbahn, der zu Verlusten nach $I^2R$ fuehrt.

- Creepage: Der kuerzeste Weg zwischen zwei leitfaehigen Teilen entlang der Oberflaeche des Isolationsmaterials.

6 zentrale Regeln fuer 48V-VRM-Boards (Kurzuebersicht)

| Regel / Richtlinie | Warum das wichtig ist (Physik/Kosten) | Zielwert / Aktion |

|---|---|---|

| Eingangsschleife minimieren | Hohes dI/dt erzeugt Spannungsspitzen ($V = L \cdot di/dt$). Grosse Schleifen zerstoeren FETs. | < 2 mm Abstand (Caps zu FETs) |

| Kupfergewicht maximieren | Senkt ohmsche Erwaermung und Spannungsabfall. | 2oz - 4oz (Innenlagen) |

| Durchgehende Ground-Plane | Liefert Rueckstrompfad und Abschirmung. Schnitte in der Plane erhoehen die Induktivitaet. | Keine Splits unter der Leistungsstufe |

| Thermal-Via-Dichte | Leitet Waerme von Top-Layer-Bauteilen in Innen- und Bottom-Lagen ab. | 1,0 mm Pitch (unter Pads) |

| Gate-Drive-Isolation | Verhindert, dass Power-Rauschen Fehltriggern verursacht. | 20 mil Abstand zum SW-Node |

| Symmetrischer Stackup | Verhindert Verzug im Reflow bei Heavy Copper. | Gespiegelte Kupfergewichte |

FAQ

Q: Warum ist 48V fuer moderne Rechenzentren gegenueber 12V bevorzugt?

A: 48V senkt den Strom gegenueber 12V bei gleicher Leistung auf ein Viertel. Da die Verlustleistung proportional zu $I^2R$ ist, sinken die Verteilverluste um den Faktor 16. Dadurch sind duennere Stromschienen und hoehere Effizienz moeglich.

Q: Kann ich Standard-FR-4 fuer ein 48V-VRM-Board verwenden?

A: Bei Anwendungen mit niedriger Leistung ja. Bei hochdichten VRMs kann Standard-FR-4 mit Tg 130 bis 140°C jedoch altern oder delaminieren. Wir empfehlen klar High-Tg-FR-4 (Tg >= 170°C) oder spezielle thermische Materialien.

Q: Was ist die minimale Leiterbahnbreite fuer 48V-Power-Traces?

A: Es gibt keinen pauschalen Mindestwert. Er haengt von Strom und erlaubter Temperaturerhoehung ab. Verwenden Sie IPC-2152-Diagramme. Fuer 20A bei 10°C Temperaturanstieg auf 2oz Kupfer koennen zum Beispiel etwa 300 bis 400 mil Leiterbahnbreite oder Flaechen notwendig sein.

Q: Brauche ich Blind oder Buried Vias fuer VRM-Boards?

A: Nicht immer, aber sie helfen bei hochdichten Designs. Blind Vias erlauben Gate-Drive-Routing auf Aussenlagen, ohne die inneren Power-Planes zu perforieren, und erhalten dadurch die Stromtragfaehigkeit der Innenlagen.

Q: Wie spezifiziere ich Heavy Copper in meinen Fertigungsunterlagen?

A: Geben Sie das fertige Kupfergewicht jeder Lage in der Stackup-Tabelle klar an, z. B. "Layer 2: 3oz Cu". Ergaenzen Sie ausserdem "UL approved heavy copper process", damit der Fertiger die passende Aetzkompensation einsetzt.

Q: Welches Oberflaechenfinish ist fuer 48V-VRM-Boards am besten?

A: ENIG ist sehr gut fuer Planaritaet und Fine-Pitch-Bauteile. Immersion Silver ist elektrisch ebenfalls stark, verlangt aber kontrollierte Handhabung. HASL wird auf Fine-Pitch-Pads meist vermieden, weil die Oberflaeche ungleichmaessig ist.

Angebot / DFM-Review fuer 48V-VRM-Boards anfordern

Sind Sie bereit, Ihr Hochleistungs-VRM in die Fertigung zu bringen? Das Engineering-Team von APTPCB ist auf Heavy Copper und thermische Management-Loesungen spezialisiert.

Senden Sie uns fuer ein umfassendes DFM-Review bitte Folgendes:

- Gerber-Dateien (bevorzugt RS-274X)

- Stackup-Diagramm mit Kupfergewichten, z. B. 2oz, 3oz oder 4oz

- Bohrdaten (NC Drill)

- Fabrication Drawing mit Tg-Anforderungen und Farbe der Loetstoppmaske

- Netlist (IPC-356) fuer die elektrische Verifikation

Fazit

Ein erfolgreiches 48V-VRM-Board ist immer ein Kompromiss aus elektrischer Effizienz, Waermeabfuhr und Herstellbarkeit. Wenn Sie Heavy-Copper-Regeln einhalten, die Thermal-Via-Strategie optimieren und die richtigen Materialien waehlen, erhalten Sie effiziente und zugleich zuverlaessige Leistungsmodule. Das Layout darf in Ihrem Power-Delivery-Network nicht zum Engpass werden.

Unterzeichnet, das Engineering-Team von APTPCB