Inhalte

- Highlights

- 5G-DU-PCB: Definition und Anwendungsbereich

- Regeln und Spezifikationen fuer 5G-DU-PCBs

- Implementierungsschritte fuer 5G-DU-PCBs

- Troubleshooting bei 5G-DU-PCBs

- Checkliste zur Lieferantenqualifizierung: So pruefen Sie Ihren Leiterplattenhersteller

- Glossar

- 6 zentrale Regeln fuer 5G-DU-PCBs (Spickzettel)

- FAQ

- Angebot / DFM-Review fuer 5G-DU-PCBs anfragen

- Fazit

In der Architektur von 5G-Netzen fungiert die 5G-DU-PCB (Distributed Unit) als Rechenplattform, die den zentralisierten Kern mit dem Funk-Edge verbindet. Im Unterschied zur AAU (Active Antenna Unit), die sich um die HF-Uebertragung kuemmert, ist die DU fuer die Echtzeit-Basisbandverarbeitung und den Hochgeschwindigkeits-Datentransport ueber eCPRI-Schnittstellen zustaendig. Fuer PCB-Designer und CAM-Ingenieure steht eine 5G-DU-Platine fuer das Zusammentreffen von High-Speed-Digitaldesign, Thermomanagement und strengen Anforderungen an die Signalintegritaet.

Diese Boards funktionieren im Kern wie Hochleistungsserver, die in Telekommunikationsumgebungen eingesetzt werden. Sie muessen enorme Datenraten verarbeiten, oft 25 Gbps bis 56 Gbps pro Lane, und zugleich Bedingungen in Outdoor-Schraenken standhalten. Dieser Leitfaden zerlegt die fertigungstechnischen Realitaeten beim Bau zuverlaessiger 5G-DU-PCBs.

Quick Answer

Um eine funktionsfaehige 5G-DU-PCB zu fertigen, muessen Sie der Signalintegritaet hoehere Prioritaet geben als typischen Kosteneinsparungen mit Standard-FR4.

- Kritische Regel: Nutzen Sie Ultra-Low-Loss-Materialien (Df < 0,004 @ 10 GHz) wie Panasonic Megtron 6/7 oder Isola Tachyon. Standard-FR4 reicht fuer die Signalgeschwindigkeiten einer DU nicht aus.

- Hauefiger Fehler: Backdrilling wird vernachlaessigt. Ab 25 Gbps wirken Via-Stubs wie Antennen und verursachen starke Reflexionen sowie Datenverluste.

- Verifizierung: Verpflichtende TDR-Tests (Time Domain Reflectometry) fuer die Impedanzkontrolle (±5 % oder ±8 %) sowie VNA-Messungen fuer die Einfuegedaempfung.

Highlights

- Materialauswahl: Erfordert High-Speed-Laminate mit niedriger Dielektrizitaetskonstante (Dk) und niedrigem Verlustfaktor (Df), um die Signaldaempfung zu minimieren.

- Backdrilling: Unerlaesslich, um ungenutzte Via-Stubs an hochschnellen differentiellen Paaren zu entfernen, zum Beispiel bei PCIe Gen 4/5 und eCPRI.

- Lagenzahl: Liegt typischerweise zwischen 14 und 26 Lagen und erfordert haeufig mehrere Laminationszyklen.

- Kupferprofil: Einsatz von HVLP-Kupferfolie (Hyper Very Low Profile), um Skin-Effect-Verluste bei hohen Frequenzen zu reduzieren.

- Thermisches Design: Starker Einsatz von Thermal Vias und gegebenenfalls eingebetteten Kupfermuenzen, um leistungsstarke FPGAs und ASICs zu kuehlen.

5G-DU-PCB: Definition und Anwendungsbereich

Das 5G-RAN (Radio Access Network) ist in drei Teile gegliedert: CU (Centralized Unit), DU (Distributed Unit) und RU (Radio Unit). Die 5G-DU-PCB ist die Hardwareplattform fuer die Distributed Unit. Sie verarbeitet Layer-1- (Physical) und Layer-2-Protokolle (MAC/RLC) in Echtzeit.

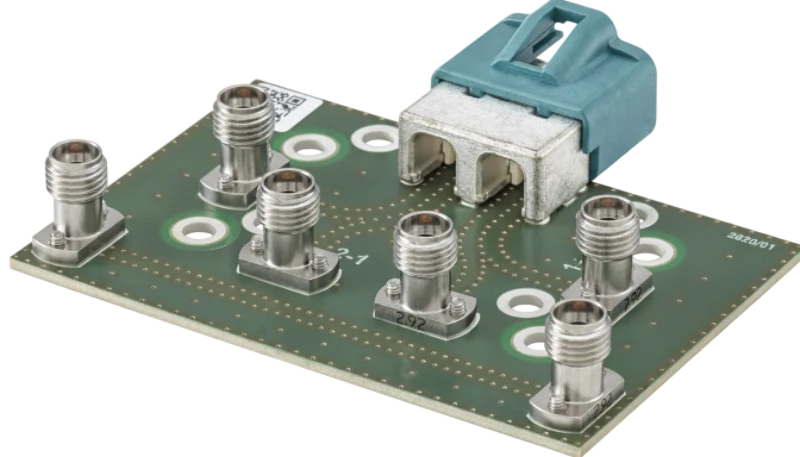

Physisch aehnelt eine DU-PCB einer komplexen High-Speed-PCB oder einer Telekommunikations-Backplane. Sie ist dicht mit BGA-Komponenten wie FPGAs und DSPs, optischen Kaefigen wie SFP28/QSFP28 sowie Hochgeschwindigkeitssteckverbindern bestueckt. Die Fertigungsherausforderung besteht darin, ueber lange Leiterbahnen hinweg die Signalintegritaet zu erhalten und gleichzeitig die bei intensiver Verarbeitung entstehende Waerme zu beherrschen.

Im Unterschied zur AAU, die stark HF-analog gepraegt ist, ist die DU digital-lastig. Allerdings sind diese "digitalen" Signale so schnell, dass sie analoges Verhalten zeigen und deshalb eine praezise, fast HF-aehnliche Fertigung verlangen.

Technik / Entscheidungshebel → Praktische Auswirkung

| Entscheidungshebel / Spezifikation | Praktische Auswirkung (Yield/Kosten/Zuverlaessigkeit) |

|---|---|

| Material: Megtron 7 vs. FR4 | Megtron 7 reduziert die Einfuegedaempfung bei 25 GHz um >50 %. Kosteneffekt: 3-4x hoehere Rohmaterialkosten, fuer die Funktion aber wesentlich. |

| Backdrilling (Stub-Entfernung) | Reduziert deterministischen Jitter. Yield-Effekt: Fuegt einen Bohrprozess hinzu und verlangt eine praezise Tiefenkontrolle (±0,05 mm), damit Innenlagen nicht beschaedigt werden. |

| HVLP-Kupferfolie | Glaetteres Kupfer verringert Skin-Effect-Verluste. Zuverlaessigkeitseffekt: Verbessert die Oeffnung des Eye-Diagramms, erfordert aber eine sorgfaeltige Bonding-Behandlung gegen Delamination. |

| Impedanztoleranz ±5 % | Engere Kontrolle als beim Standardwert ±10 %. Yield-Effekt: Verlangt strikte Aetzkompensation und konstante Prepreg-/Dielektrikumsdicken beim Pressen. |

Regeln und Spezifikationen fuer 5G-DU-PCBs

Die Konstruktion und Fertigung einer DU-PCB verlangt die Einhaltung strenger Spezifikationen, damit die Platine die Bandbreitenanforderungen von 5G tragen kann.

| Regel / Spezifikation | Empfohlener Wert | Warum das wichtig ist | So wird verifiziert |

|---|---|---|---|

| Material-Df (Verlustfaktor) | < 0,005 @ 10 GHz | Ein hoher Df fuehrt dazu, dass Signalenergie im Dielektrikum als Waerme verloren geht und Reichweite sowie Datenintegritaet zerstoert. | IPC-4101-Datenblatt pruefen; Laminatmarke verifizieren, z. B. Megtron-PCB. |

| Backdrill-Stub-Laenge | < 10 mil (0,25 mm) | Lange Stubs erzeugen Reflexionen und Resonanzen, die Hochgeschwindigkeitssignale zerstoeren. | Querschliffanalyse (Microsection) nach dem Bohren. |

| Impedanzkontrolle | 85Ω / 100Ω ±8% | Fehlangepasste Impedanz verursacht Signalreflexionen (Return Loss). | TDR-Coupons auf Produktionsnutzen. |

| Kupferrauheit | Rz < 2,0µm (HVLP) | Raues Kupfer erhoeht durch den Skin Effect den Widerstand bei hohen Frequenzen. | REM (Scanning Electron Microscope) oder Lieferantenzertifikate. |

| Via-Aspect-Ratio | 10:1 bis 12:1 | Stellt zuverlaessige Galvanik in dicken Boards von 2,0 mm bis 3,0 mm sicher. | Querschliff zur Messung der Kupferschicht in der Bohrungsmitte. |

| Glasgewebestil | Spread Glass (1067/1078) | Verhindert den Fiber-Weave-Effekt (Skew), wenn differentielle Paare ueber Luecken in Glasbuendeln laufen. | Sichtpruefung des Laminattyps; Spread-Glass-Gewebe verwenden. |

Implementierungsschritte fuer 5G-DU-PCBs

Der Weg vom Design zum fertigen Produkt umfasst spezielle Prozessschritte, die auf hochschnelle Digitalboards zugeschnitten sind.

Implementierungsprozess

Schritt-fuer-Schritt-Anleitung zur Umsetzung

Waehlen Sie verlustarme Materialien wie Megtron 6. Entwerfen Sie einen symmetrischen Stackup mit 14-24 Lagen, um Kupferdichte auszugleichen und Verzug zu vermeiden. Definieren Sie Impedanzmodelle fuer Single-Ended- und differentielle Paare mit einem Impedanzrechner.

Fuehren Sie die Laminierung mit Vakuumpressen aus, um Lunker zu vermeiden. Danach folgen Bohrungen mit hohem Aspect Ratio und Controlled Depth Drilling (Backdrilling), um Via-Stubs mit einer Toleranz von 0,2 mm zu entfernen. Fuer feine Leiterbahnen sollte LDI (Laser Direct Imaging) eingesetzt werden.

Tragen Sie Kupfer mit sehr gutem Throwing Power auf, um die Integritaet der Bohrlochwaende sicherzustellen. Nutzen Sie plane Oberflaechen wie ENIG oder Immersion Silver, damit Fine-Pitch-BGAs und Hochgeschwindigkeitssteckverbinder ausreichend plan aufliegen.

Fuehren Sie 100 % elektrische Tests durch. Nutzen Sie TDR zur Impedanzpruefung auf Testcoupons. Zusaetzlich sollte Interconnect Stress Testing (IST) die Via-Zuverlaessigkeit unter thermischen Zyklen absichern, was fuer Outdoor-Telekomtechnik entscheidend ist.

Troubleshooting bei 5G-DU-PCBs

Selbst bei sorgfaeltigem Design koennen waehrend der NPI-Phase (New Product Introduction) Probleme auftreten. Hier sind typische Fehlermodi bei 5G-DU-PCBs und die passenden Gegenmassnahmen.

1. Hohe Einfuegedaempfung (Signalattenuation)

- Symptom: Signale verschlechtern sich ueber lange Leiterbahnen; Eye-Diagramme schliessen sich.

- Grundursache: Falsche Materialauswahl, zum Beispiel Standard-FR4, oder hohe Kupferrauheit.

- Loesung: Wechseln Sie zu "Low Loss"- oder "Ultra Low Loss"-Laminaten wie Isola Tachyon oder Panasonic M7. Spezifizieren Sie HVLP- oder VLP-2-Kupferfolie.

2. Spikes bei der Bitfehlerrate (BER)

- Symptom: Datenuebertragungsfehler bei bestimmten Frequenzen.

- Grundursache: Via-Stubs wirken wie resonante Antennen.

- Loesung: Setzen Sie konsequent Backdrilling ein. Stellen Sie sicher, dass die "Must Cut"-Tiefe korrekt berechnet wird, damit der ungenutzte Anteil des Via-Barrels entfernt wird, ohne die elektrische Verbindung zu trennen.

3. CAF-Wachstum (Conductive Anodic Filament)

- Symptom: Im Feld entstehen ueber die Zeit Kurzschluesse.

- Grundursache: Hohe Spannungsdifferenzen zwischen eng stehenden Vias in Kombination mit Feuchtigkeit entlang der Glasfasern.

- Loesung: Verwenden Sie "Anti-CAF"- oder "CAF Resistant"-Materialien. Vergroessern Sie nach Moeglichkeit den Via-Abstand. Sorgen Sie fuer hohe Bohrqualitaet, damit keine Mikrorisse im Harz entstehen.

4. Pad-Cratering unter BGAs

- Symptom: Pads loesen sich waehrend der Montage oder bei thermischen Zyklen unter grossen FPGAs.

- Grundursache: Spruedes Laminatmaterial oder eine zu starke CTE-Differenz (Coefficient of Thermal Expansion).

- Loesung: Verwenden Sie Hoch-Tg-Materialien mit niedrigerem Z-Achsen-CTE. Optimieren Sie zudem das Reflow-Profil waehrend der PCBA-Montage.

Checkliste zur Lieferantenqualifizierung: So pruefen Sie Ihren Leiterplattenhersteller

- Backdrill-Faehigkeit: Koennen sie die Backdrill-Tiefe auf ±0,05 mm kontrollieren? Verfuegen sie ueber automatische optische Inspektion fuer Backdrilling?

- Materiallager: Haben sie Megtron 6/7, Isola Tachyon oder Rogers-Materialien regelmaessig am Lager? (Die Lieferzeiten koennen sonst lang sein.)

- Impedanzpruefung: Verfuegen sie ueber TDR-Equipment, das differentielle Impedanzen bei den erforderlichen Anstiegszeiten messen kann?

- Registriergenauigkeit: Beherrschen sie die Lagen-zu-Lagen-Registrierung fuer Boards mit ueber 20 Lagen? (Entscheidend fuer die Backdrill-Genauigkeit.)

- Querschliffanalyse: Fuehren sie auf jedem Panel Microsections durch, um Kupferschichtdicke und Dielektrikumsaufbau zu verifizieren?

- Sauberkeit: Ist die Fertigung fuer Fine-Line-Schaltungen mit 3 mil/3 mil oder kleiner in staubkontrollierter Umgebung ausgelegt?

Glossar

Backdrilling: Ein Fertigungsprozess, bei dem mit einem etwas groesseren Bohrer der ungenutzte Teil eines metallisierten Durchkontaktierungslochs (Stub) entfernt wird, um Signalreflexionen zu reduzieren.

eCPRI (Enhanced Common Public Radio Interface): Eine paketbasierte Schnittstelle in 5G zur Verbindung von DU (Distributed Unit) und RU (Radio Unit). Auf der PCB werden dafuer hochschnelle differentielle Paare benoetigt.

Df (Dissipation Factor): Kennwert dafuer, wie viel Signalenergie im PCB-Material in Form von Waerme verloren geht. Niedrigere Werte wie 0,002 sind fuer 5G besser.

Dk (Dielectric Constant): Kennwert fuer die Faehigkeit eines Materials, elektrische Energie zu speichern. Ein niedrigerer Dk erlaubt schnellere Signalausbreitung und breitere Leiterbahnen bei gegebener Impedanz.

CTE (Coefficient of Thermal Expansion): Gibt an, wie stark sich das PCB-Material bei Erwaermung ausdehnt. CTE-Mismatches zwischen PCB und Bauteilen koennen zu Loetstellenversagen fuehren.

6 zentrale Regeln fuer 5G-DU-PCBs (Spickzettel)

| Regel / Leitlinie | Warum das zaehlt (Physik/Kosten) | Zielwert / Massnahme |

|---|---|---|

| Materialauswahl | Standard-FR4 absorbiert hochfrequente Signale. | Megtron 6/7, IT-968 (Low Loss) |

| Backdrilling | Stubs verursachen Resonanzen und Signalreflexionen. | Stub < 10 mil (Pflicht bei >10 Gbps) |

| Kupferprofil | Raues Kupfer erhoeht Skin-Effect-Verluste. | HVLP oder VLP-2 Folie |

| Impedanztoleranz | Sichert die Signalintegritaet ueber den gesamten Kanal. | ±8 % oder ±5 % (strenge Kontrolle) |

| Anti-Pad-Groesse | Reduziert parasitaere Kapazitaeten an Via-Uebergaengen. | Per Via-Simulation optimieren (nicht raten) |

| Glasgewebe | Verhindert Fiber-Weave-Skew in differentiellen Paaren. | Spread Glass (1067/1078/3313) |

FAQ

F: Was ist der Hauptunterschied zwischen 5G-DU-PCB und 5G-AAU-PCB?

A: Die PCB der AAU konzentriert sich auf HF-Uebertragung, Leistungsverstaerkung und Antennenarrays und nutzt haeufig Keramik- oder PTFE-Materialien. Die PCB der DU konzentriert sich dagegen auf hochschnelle digitale Basisbandverarbeitung und aehnelt eher einer High-End-Serverplatine mit verlustarmen FR4-aehnlichen Materialien wie Megtron.

F: Warum ist Backdrilling fuer 5G-DU-Boards so kritisch?

A: 5G-DU-Boards arbeiten mit Datenraten von 25 Gbps und mehr. Bei diesen Geschwindigkeiten wirkt der ungenutzte Teil einer metallisierten Durchkontaktierung wie ein Leitungsstub und erzeugt Reflexionen, die den gesamten Datenstrom verfaelschen koennen. Backdrilling entfernt diesen Stub.

F: Kann ich fuer einen 5G-DU-Prototyp aus Kostengruenden Standard-FR4 verwenden?

A: In der Regel nein. Standard-FR4 weist fuer die in einer DU genutzten High-Speed-Schnittstellen wie eCPRI oder PCIe Gen 4 zu hohe Signalverluste auf. Das Board mag einschalten, aber die Datenlinks werden mit hoher Wahrscheinlichkeit ausfallen oder stark erhoehte Fehlerraten zeigen.

F: Wie hoch ist die typische Lagenzahl einer 5G-DU-PCB?

A: Die meisten 5G-DU-PCBs liegen zwischen 14 und 26 Lagen. Diese hohe Lagenzahl ist notwendig, um dichte Hochgeschwindigkeits-Differentialpaare zu routen und gleichzeitig ausreichend Bezugsmasse- sowie Versorgungsflaechen fuer FPGA und ASIC bereitzustellen.

F: Wie wird die Waerme auf einer 5G-DU-PCB beherrscht?

A: Das Thermomanagement erfolgt ueber eine Kombination aus dicken Kupferlagen von 1 oz oder 2 oz in den Innenlagen, dichten Thermal-Via-Arrays unter heissen Bauteilen und teilweise eingebetteten Kupfermuenzen oder Stromschienen. Zusaetzlich wird die Platine fuer den thermischen Kontakt zu einem Gehaeuse-Kuehlkoerper ausgelegt.

F: Welches Oberflaechenfinish eignet sich am besten fuer 5G-DU-PCBs?

A: ENIG oder Immersion Silver werden bevorzugt. Beide bieten eine plane Oberflaeche fuer Fine-Pitch-Bauteile und fuegen im Gegensatz zu HASL keine signifikanten Dickenschwankungen hinzu, die die Impedanz beeintraechtigen koennten.

Angebot / DFM-Review fuer 5G-DU-PCBs anfragen

Sind Ihre 5G-Distributed-Unit-Designs bereit fuer die Fertigung? APTPCB ist auf hochschnelle Telekommunikationsboards mit hoher Lagenzahl spezialisiert.

Bitte bereiten Sie fuer ein praezises Angebot Folgendes vor:

- Gerber-Daten (RS-274X- oder X2-Format).

- Stackup-Zeichnung (Materialtyp klar angeben, zum Beispiel "Megtron 6" oder "aequivalent").

- Bohrtabelle (Backdrill-Lagen und Tiefen klar kennzeichnen).

- Impedanzanforderungen (konkrete Lagen und Leiterbahnbreiten auflisten).

- Stueckzahlen (Prototyp oder Serienfertigung).

Fazit

Eine erfolgreiche 5G-DU-PCB entsteht durch das kontrollierte Beherrschen der Physik hochschneller Datenuebertragung. Dazu braucht es den Wechsel von der Standard-Leiterplattenfertigung hin zu einem praezisionsorientierten Ansatz mit verlustarmen Materialien, Backdrilling und strikter Impedanzkontrolle. Wenn Sie die in diesem Leitfaden beschriebenen Regeln befolgen, insbesondere bei Materialauswahl und Stub-Entfernung, kann Ihre DU-Hardware im anspruchsvollen 5G-Oekosystem zuverlaessig arbeiten.

Gezeichnet, das Engineering-Team von APTPCB