Inhalt

- Highlights

- Umfang und Entscheidungskontext

- Im Voraus zu definierende Spezifikationen

- Hauptrisiken (Ursachen & Prävention)

- Validierung & Abnahmekriterien

- Checkliste zur Lieferantenqualifizierung

- Glossar

- 6 wesentliche Regeln für die Beschaffung von 5G SA PCBs (Spickzettel)

- FAQ

- Fordern Sie ein Angebot / DFM-Review für 5G SA PCBs an

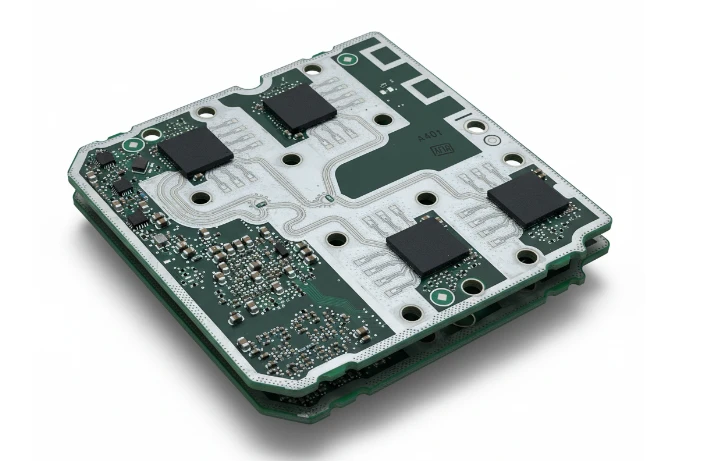

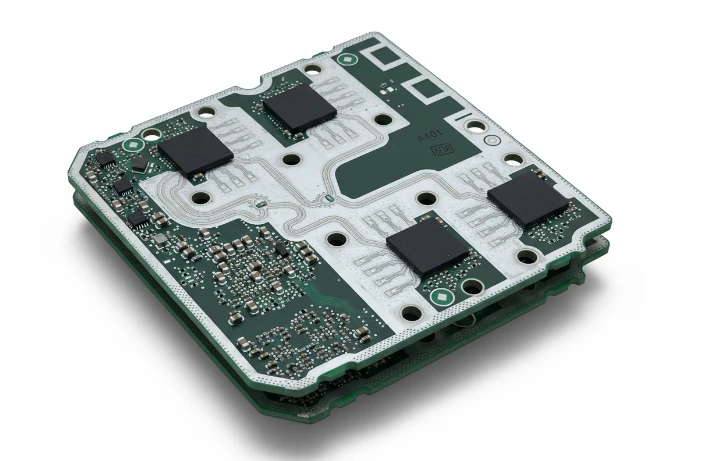

Der Übergang zu 5G Standalone (SA) Architekturen stellt eine erhebliche Eskalation der Hardwareanforderungen im Vergleich zu Non-Standalone (NSA) oder Legacy-4G-Systemen dar. Für Einkaufsmanager, Hardware-Architekten und NPI-Ingenieure (New Product Introduction) ist die Beschaffung einer 5G SA PCB nicht nur der Kauf eines Bauteils; es ist die Beauftragung eines komplexen, verlustarmen RF- und Hochgeschwindigkeits-Digitalsystems, das in rauen Umgebungen fehlerfrei funktionieren muss.

Dieser Leitfaden ist speziell für Käufer und technische Leiter konzipiert. Wir verzichten auf das Marketing-Material und konzentrieren uns auf die kritischen Spezifikationen, die Sie in Ihren RFQs (Request for Quote) definieren müssen, auf die Herstellungsrisiken, die Ihre Erträge beeinträchtigen, und auf die Kriterien, nach denen Sie Ihre Leiterplattenhersteller bewerten sollten.

Highlights

- Die Kosten von Df: Warum die Angabe des falschen Dissipationsfaktors (Df) die Signalintegrität von mmWave zerstört.

- Hybride Stapelungswirtschaftlichkeit: Wie man die Schichtmaterialien ausbalanciert, um die Kosten zu kontrollieren, ohne die SA-Leistung zu opfern.

- Risikominderung: Die drei häufigsten Ursachen für Ausfälle von 5G SA-Leiterplatten (und wie man sie vertraglich verhindert).

- Checkliste für die Lieferantenauswahl: Ein Framework zur Überprüfung der Fähigkeiten Ihres Herstellers im Bereich Hochfrequenz- und Multilayer-Fertigung.

Umfang und Entscheidungskontext

5G SA-Netzwerke operieren unabhängig von der 4G-LTE-Infrastruktur. Dies bedeutet, dass die Hardware (insbesondere Baseband Units (BBUs), Active Antenna Units (AAUs) und Core-Network-Switches) vollen End-to-End-5G-Verkehr verarbeiten muss. Für die Leiterplatte führt dies zu strengeren Anforderungen an zwei Fronten:

- Massive Datenverarbeitung (Digitalschichten): Erfordert PCIe Gen 4/5 und 100G/400G Ethernet-Routing mit extremer Impedanzkontrolle zur Verwaltung enormer Datenmengen mit geringer Latenz.

- Ultra-High Frequency RF (Antennenschichten): Erfordert mmWave-Fähigkeiten (24 GHz und darüber) mit nahezu null Signalverlust und hervorragendem Wärmemanagement für Massive MIMO-Arrays.

Netzwerkarchitektur → Auswirkungen auf die Leiterplatte

| 5G SA Anforderung | PCB-Herstellungsauswirkung |

|---|---|

| Extrem niedrige Latenz (URLLC) | Erfordert Ultra-Low-Loss-Materialien (z. B. Megtron 6/7) und präzises Backdrilling, um Signalreflexionen an Vias zu beseitigen. |

| Massive MIMO (Sub-6GHz & mmWave) | Zwingt zur Verwendung von [High Frequency PCB](/de/pcb/high-frequency-pcb) Laminaten (z. B. Rogers, Taconic) und strikter Impedanzkontrolle (±5%). |

| Edge Computing Verarbeitung | Hohe Lagenzahlen (16-30 Lagen) [Multilayer PCB](/de/pcb/multilayer-pcb) Designs mit Hochdichte-Verbindungen (HDI). |

| Hohe Energieeffizienz | Erfordert fortschrittliches Wärmemanagement wie schwere Kupferschichten (2 oz+) und eingebettete Kupfer-Münzen (Embedded Copper Coins). |

Im Voraus zu definierende Spezifikationen

Vage Ausschreibungen führen zu fehlerhaften Boards oder unerwarteten Kostensprüngen während der Prototypenphase. Verlangen Sie bei der Beschaffung einer 5G SA-Leiterplatte, dass Ihr Designteam diese Spezifikationen klar definiert:

1. Die Materialstruktur (Stackup)

Dies ist der größte Kostentreiber. Die Angabe eines "Voll-Teflon"-Boards ist unnötig teuer.

- Kaufregel: Spezifizieren Sie einen Hybriden Stackup. Verwenden Sie teure PTFE-/Kohlenwasserstoff-Laminate (z. B. Rogers 4350B, RO4835) nur für die 1-2 Lagen, die die HF-Signale führen. Verwenden Sie Standard-FR4 mit hohem Tg (z. B. IT-180, S1000-2) für die Energie- und Niederfrequenz-Steuerungslagen.

2. Kupferprofil (Rauigkeit)

Der Skin-Effekt bedeutet, dass hochfrequente Signale auf der Oberfläche des Kupfers wandern. Raue Oberflächen verlängern den Signalweg und verursachen Einfügedämpfung.

- Kaufregel: Fordern Sie HVLP (Hyper Very Low Profile) Kupferfolie für die HF-Lagen an. Rz (Rauigkeit) sollte < 2.0 µm sein. Akzeptieren Sie niemals Standard-RTF (Reverse Treated Foil) für mmWave-Pfade.

3. Impedanztoleranz

Standardboards erlauben eine Impedanzabweichung von ±10%. Bei 5G SA führt dies zu Datenverfälschungen.

- Kaufregel: Definieren Sie strengere Toleranzen. Spezifizieren Sie ±5% oder maximal ±7% auf allen hochgeschwindigkeitsdifferentiellen Paaren und HF-Antennenpfaden.

4. Backdrilling (Via-Stub-Entfernung)

Vias hinterlassen Stummel ("Stubs"), die wie winzige Antennen wirken, Signale reflektieren und die Latenz ruinieren.

- Kaufregel: Geben Sie klar an, welche hochgeschwindigkeitsnetze Backdrilling erfordern. Der verbleibende Stub darf nicht länger als 10 mil (idealerweise <8 mil) sein.

Hauptrisiken (Ursachen & Prävention)

Die Herstellung dieser Platinen ist komplex. Hier sind die Risiken, die Sie überwachen müssen, und wie Sie verhindern, dass sie Ihre Lieferkette stören.

Risiko 1: Delamination im hybriden Stackup

Die Ursache: HF-Materialien und FR4 haben unterschiedliche Wärmeausdehnungskoeffizienten (CTE). Beim Bleifrei-Löten dehnen sie sich unterschiedlich schnell aus, was zu Blasenbildung oder Trennung der Lagen führt. Die Vorbeugung: Beauftragen Sie Hersteller mit nachgewiesener Erfahrung im Bereich Hybrid-Lamination. Sie müssen spezielle "Low-Flow"-Prepregs verwenden und das Design des Stackups auf strukturelle Symmetrie überprüfen, bevor der Werkzeugbau beginnt.

Risiko 2: Hohe Passive Intermodulation (PIM)

Die Ursache: PIM ist die unerwünschte Vermischung von HF-Signalen. Dies wird oft durch magnetische Materialien im Signalweg oder ungleichmäßiges Kupferätzen verursacht. Eine häufige Ursache ist die Verwendung von ENIG (Electroless Nickel Immersion Gold) Oberflächenveredelungen, da Nickel magnetisch ist. Die Vorbeugung: Verbieten Sie ENIG auf HF-Traces. Spezifizieren Sie stattdessen Immersion Silver (Chemisch Silber) oder Bare Copper (OSP). Fordern Sie Ätztoleranzen von ±1 mil an, um gezackte Kupferkanten zu vermeiden.

Risiko 3: Thermische Drosselung (Thermal Throttling)

Die Ursache: 5G-Leistungsverstärker (PAs) werden extrem heiß. Wenn das PCB die Wärme nicht ableiten kann, drosselt das System die Leistung und die Lebensdauer der Komponenten verkürzt sich drastisch. Die Vorbeugung: Arbeiten Sie nicht nur mit Standard-Vias. Verlangen Sie von Ihrem Hersteller Kapazitäten für VIPPO (Via-in-Pad Plated Over) mit leitfähiger Pastenfüllung oder Embedded Copper Coins für punktuelle extreme Kühlung.

Validierung & Abnahmekriterien

Wie beweisen Sie, dass der Hersteller das geliefert hat, was Sie spezifiziert haben? Fügen Sie diese Testanforderungen in Ihren Lieferantenvertrag ein:

- TDR-Berichte (Time Domain Reflectometry): Der Lieferant muss TDR-Berichte an Testcoupons für jede Produktionscharge vorlegen, die belegen, dass die Impedanz innerhalb des Toleranzbereichs von ±5 % liegt.

- Mikroschliff-Analyse (Cross-Section): Verlangen Sie Querschliff-Fotos, um sicherzustellen, dass die Microvias korrekt mit Kupfer gefüllt sind und dass das Backdrilling keine internen Lagen durchtrennt hat.

- Zertifikate für Hochfrequenzmaterialien: Fordern Sie ein CoC (Certificate of Compliance) vom Laminathersteller (z. B. Rogers Corporation), um zu überprüfen, ob kein billigeres Material ersetzt wurde.

- PIM-Testzertifizierung: Für Antennenplatinen sollte der Hersteller PIM-Testergebnisse vorlegen (typischerweise ist das Ziel < -160 dBc).

Checkliste zur Lieferantenqualifizierung

Nicht jede Leiterplattenfabrik ist für 5G SA gerüstet. Verwenden Sie diese Checkliste zur Bewertung potenzieller Lieferanten (wie APTPCB):

- Laminatbestand: Haben sie Hochfrequenzmaterialien (Rogers, Taconic, Megtron) auf Lager, um Lieferzeiten zu verkürzen?

- Fähigkeit zur Hybrid-Lamination: Können sie Nachweise für vergangene erfolgreiche Hybrid-Builds erbringen und den Backprozess (Baking Process) zur Vermeidung von Feuchtigkeitsaufnahme erklären?

- Backdrilling-Präzision: Was ist ihre Z-Achsen-Tiefen-Toleranz beim Backdrilling? (Muss ±0,1 mm oder besser sein).

- Kupferfolien-Optionen: Bieten sie standardmäßig HVLP- oder RTF-Kupfer für Hochgeschwindigkeitsschichten an?

- Inspektionswerkzeuge: Verfügen sie über TDR-Maschinen, Röntgengeräte für VIPPO-Inspektion und automatisierte optische Inspektion (AOI), die feine Strukturen auflösen kann?

- Oberflächenveredelungen: Bieten sie chemisch Silber, ENEPIG oder OSP in großem Maßstab als Alternativen zu ENIG an?

Glossar

5G SA (Standalone): Eine 5G-Netzwerkarchitektur, die nicht auf eine vorhandene 4G-LTE-Infrastruktur angewiesen ist und im Vergleich zu NSA (Non-Standalone) höhere Geschwindigkeiten und geringere Latenzen bietet. Hybrid Stackup (Hybrider Lagenaufbau): Ein PCB-Design, das teure Hochfrequenzmaterialien nur auf bestimmten kritischen Schichten verwendet, während Standard-FR4 auf anderen Schichten eingesetzt wird, um die Kosten zu optimieren. Backdrilling: Ein Herstellungsverfahren, bei dem der nicht benötigte Teil eines plattierten Durchgangslochs entfernt wird, um Signalreflexionen in Hochgeschwindigkeitsnetzen zu minimieren. Df (Dissipation Factor / Verlustfaktor): Ein Maß für den Energieverlust eines dielektrischen Materials. Ein niedrigerer Df ist für 5G-Signale entscheidend, um Signalverluste zu minimieren. PIM (Passive Intermodulation): Signalverzerrungen, die durch Nichtlinearitäten in passiven Komponenten verursacht werden und bei 5G-HF-Pfaden streng kontrolliert werden müssen.

6 wesentliche Regeln für die Beschaffung von 5G SA PCBs (Spickzettel)

| Kaufregel | Warum es wichtig ist | Beschaffungsaktion |

|---|---|---|

| Verwenden Sie immer Hybrid-Stackups | Senkt die Kosten im Vergleich zu Voll-HF-Boards drastisch. | Verlangen Sie eine Rogers + FR4 Mischung |

| Strikte Df-Spezifikation | Verhindert Signalverluste bei mmWave-Frequenzen. | Spezifizieren Sie Df < 0.003 für HF-Lagen |

| Kupfer-Rauheit kontrollieren | Standardkupfer zerstört die Signalintegrität durch den Skin-Effekt. | Fordern Sie HVLP-Kupfer (Rz < 2µm) |

| Kein ENIG auf HF-Antennen | Der magnetische Nickel-Anteil verursacht PIM und Verluste. | Spezifizieren Sie Chemisch Silber oder OSP |

| Fordern Sie Backdrilling an | Löst Latenz- und Reflexionsprobleme in URLLC-Pfaden. | Stub-Toleranz < 10 mil vorgeben |

| Fordern Sie TDR-Testberichte | Garantiert, dass die kritische ±5% Impedanz eingehalten wurde. | Machen Sie TDR-Berichte zu einer Po-Bedingung |

FAQ

F: Warum sind 5G SA PCBs teurer als 4G-Boards?

A: Die Kostensteigerung wird durch den Bedarf an verlustarmen, hochfrequenten Laminaten (wie Rogers oder PTFE-basierten Materialien), hochpräziser Impedanzkontrolle, strengeren Ätztoleranzen für HVLP-Kupfer und zusätzlichen Prozessschritten wie Backdrilling und Hybridschicht-Lamination angetrieben.

F: Können wir die Kosten senken, indem wir auf Standard-FR4-Materialien zurückgreifen?

A: Nein, nicht für die HF- und Hochgeschwindigkeitsschichten. Die Verwendung von Standard-FR4 für die gesamte Platine in einem 5G SA-Gerät führt aufgrund seines hohen Verlustfaktors (Df) zu katastrophalen Signalverlusten und einer drastischen Verringerung der Abdeckung und der Datenraten. Sie können die Kosten jedoch durch die Verwendung von hybriden Lagenaufbauten (Hybrid Stackups) optimieren.

F: Wie lange ist die Vorlaufzeit (Lead Time) für Prototypen von 5G SA PCBs?

A: Aufgrund der Komplexität hybrider Laminierungen, Backdrilling-Anforderungen und präziser Impedanztests liegen die Standardvorlaufzeiten für Prototypen bei seriösen Herstellern wie APTPCB normalerweise zwischen 10 und 15 Werktagen. Bei Expedited-Services kann dies verkürzt werden, hängt jedoch von der Materialverfügbarkeit ab.

F: Welches Oberflächenfinish ist am besten für 5G-Antennen-PCBs?

A: Immersion Silver (Chemisch Silber) ist das bevorzugte Oberflächenfinish. Es bietet eine hervorragende Leitfähigkeit, hat minimale Auswirkungen auf hochfrequente Signale (Skin-Effekt) und ist im Gegensatz zu ENIG nicht-magnetisch, was das Risiko passiver Intermodulation (PIM) stark reduziert.

F: Was ist PIM und warum ist es in 5G so kritisch?

A: PIM (Passive Intermodulation) ist eine Form der Signalverzerrung, die auftritt, wenn zwei oder mehr Signale in einer nichtlinearen passiven Komponente oder Struktur gemischt werden. Bei Massive MIMO und höheren Leistungssendern in 5G SA kann PIM starkes Rauschen erzeugen, das den Empfänger blockiert. Strenge Ätzkontrolle und die Vermeidung ferromagnetischer Materialien (wie Nickel in ENIG) auf dem PCB sind zur Vermeidung unerlässlich.

Fordern Sie ein Angebot / DFM-Review für 5G SA PCBs an

Wenn Sie eine 5G SA-Leiterplatte beschaffen, erfordert der Übergang vom Design zur Produktion einen Partner, der die Physik von Hochfrequenzmaterialien versteht und über die Ausrüstung verfügt, um diese zu verarbeiten.

Bei APTPCB sind wir spezialisiert auf Hybrid-Lamination, Backdrilling und strenge Impedanzkontrolle für den Telekommunikations- und Unternehmenssektor. Um ein genaues Angebot und ein umfassendes Design for Manufacturing (DFM) Review zu erhalten, übermitteln Sie bitte:

- Gerber-Dateien: (RS-274X oder ODB++ Format)

- Stackup-Anforderungen: (Geben Sie die bevorzugten HF-Materialien und die Lagenreihenfolge an)

- Impedanz-Datenblatt: (Zielwerte, Toleranzanforderungen z. B. ±5 %)

- Spezielle Anforderungen: (Notieren Sie jegliches Backdrilling, PIM-Tests oder Anforderungen an chemisch Silber)

Kontaktieren Sie unser Engineering-Team noch heute, um sicherzustellen, dass Ihr 5G SA-Projekt pünktlich, innerhalb des Budgets und spezifikationsgerecht auf den Markt kommt.