Inhalt

- Highlights

- Kostengünstige Leiterplattenfertigung: Definition und Umfang

- Regeln und Spezifikationen für die kostengünstige Leiterplattenfertigung

- Schritte zur Implementierung der kostengünstigen Leiterplattenfertigung

- Fehlerbehebung bei der kostengünstigen Leiterplattenfertigung

- 6 Wesentliche Regeln für die kostengünstige Leiterplattenfertigung (Spickzettel)

- FAQ

- Angebot anfordern / DFM-Überprüfung für kostengünstige Leiterplattenfertigung

- Fazit In der Welt der Elektronik-Hardware bedeutet "kostengünstig" nicht "minderwertig". Echte kostengünstige Leiterplattenfertigung ist das Ergebnis eines rigorosen Design for Manufacturing (DFM)-Engineerings – der Optimierung Ihres Platinenlayouts, um in die "Standardfähigkeiten" des Fertigungsbetriebs zu passen, um die Ausbeute zu maximieren und die manuelle Handhabung zu minimieren. Als leitende CAM-Ingenieure bei APTPCB sehen wir Tausende von Designs, bei denen einfache Anpassungen der Leiterbahnbreite, Lochgröße oder Materialauswahl die Produktionskosten um 30 % oder mehr senken könnten, ohne die Signalintegrität zu beeinträchtigen.

Kurze Antwort

Kostengünstige Leiterplattenfertigung wird durch das Design von Platinen erreicht, die Standard-FR4-Materialien, Standard-Verarbeitungsfenster (z. B. Leiterbahn/Abstand ≥ 5mil) und eine effiziente Panel-Auslastung nutzen. Es vermeidet "Kostentreiber" wie Blind-/Buried-Vias, nicht-standardisierte Lagenaufbauten oder enge Toleranzanforderungen, es sei denn, dies ist absolut notwendig.

- Goldene Regel: Halten Sie sich an das "Standard-Spezifikationsfenster" (z. B. 1,6 mm Dicke, 1 oz Kupfer, grüne Lötstoppmaske), um kundenspezifische Engineering-Gebühren zu vermeiden.

- Häufige Falle: Die Angabe enger mechanischer Toleranzen (z. B. ±0,05 mm Routing) oder fortschrittlicher Via-Strukturen (HDI) bei einfachen Platinen, was den Einsatz teurer Laserbohrungen und spezialisierter Ausrichtungsausrüstung erzwingt.

- Verifizierung: Führen Sie immer eine DFM-Prüfung durch, um sicherzustellen, dass Ihre Panel-Auslastung über 80 % liegt; Abfallmaterial ist ein Haupttreiber der Stückkosten.

Highlights

- Materialstandardisierung: Die Verwendung von weit verbreitetem FR4 (TG150) eliminiert Sonderbestellgebühren und Lieferzeiten.

- Disziplin bei der Lagenanzahl: Die Reduzierung eines Designs von 6 auf 4 Lagen kann den Grundpreis aufgrund geringerer Laminierungszyklen um etwa 30-40% senken.

- Bohreffizienz: Die Minimierung der Anzahl unterschiedlicher Bohrergrößen reduziert die Werkzeugwechselzeit und den Maschinenverschleiß.

- Oberflächenveredelung: HASL (Heißluftverzinnung) bleibt die kostengünstigste Oberfläche für allgemeine Elektronik, während ENIG der Standard für Anforderungen an ebene Oberflächen ist.

- Volumenskalierung: Die Kosten sinken erheblich, wenn man vom Prototyp zur Massenproduktion von Leiterplatten übergeht, aufgrund der Amortisation der Einrichtungsgebühren.

Kostengünstige Leiterplattenfertigung: Definition und Umfang

Um die kostengünstige Leiterplattenfertigung zu verstehen, muss man die Kostenstruktur einer Leiterplattenfabrik kennen. Der Preis einer Leiterplatte wird von drei Hauptfaktoren bestimmt: Materialfläche, Prozesskomplexität und Ausbeute.

- Materialfläche: Sie zahlen für die gesamte Produktionsplatte (z.B. 18"x24"), nicht nur für Ihre einzelne Platine. Wenn Ihr Design eine ungewöhnliche Form hat, die zu 50% Abfall auf der Platte führt, verdoppeln sich Ihre effektiven Kosten.

- Prozesskomplexität: Jeder Schritt, der dem Standardablauf hinzugefügt wird, erhöht die Kosten. Eine Standard-2-Lagen-Platine durchläuft Bohren, Plattieren, Ätzen und Maskieren. Wenn Sie Blindbohrungen hinzufügen, muss die Platine mehrmals gebohrt, plattiert und laminiert werden (sequenzielle Laminierung), was die Maschinenzeit und den Arbeitsaufwand drastisch erhöht.

- Ausbeute: Dies ist der versteckte Kostentreiber. Wenn Sie mit 3mil/3mil Leiterbahn/Abstand entwerfen, könnte die Fabrik eine Ausbeute von 90% haben. Wenn Sie mit 5mil/5mil entwerfen, könnte die Ausbeute 99% betragen. Die Fabrik kalkuliert den Preis der Platine so, dass die erwartete Ausschussrate abgedeckt ist.

Daher geht es bei der kostengünstigen Fertigung darum, für hohe Ausbeute und Standardprozesse zu entwerfen. Es beinhaltet die Auswahl von FR4-Leiterplattenmaterialien, die in großen Mengen vorrätig sind, und das Vermeiden von Merkmalen, die "fortschrittliche" Fertigungslinien auslösen, es sei denn, die Schaltungsphysik erfordert dies.

Technologie / Entscheidungshebel → Praktische Auswirkung

| Entscheidungshebel / Spezifikation | Praktische Auswirkung (Ausbeute/Kosten/Zuverlässigkeit) |

|---|---|

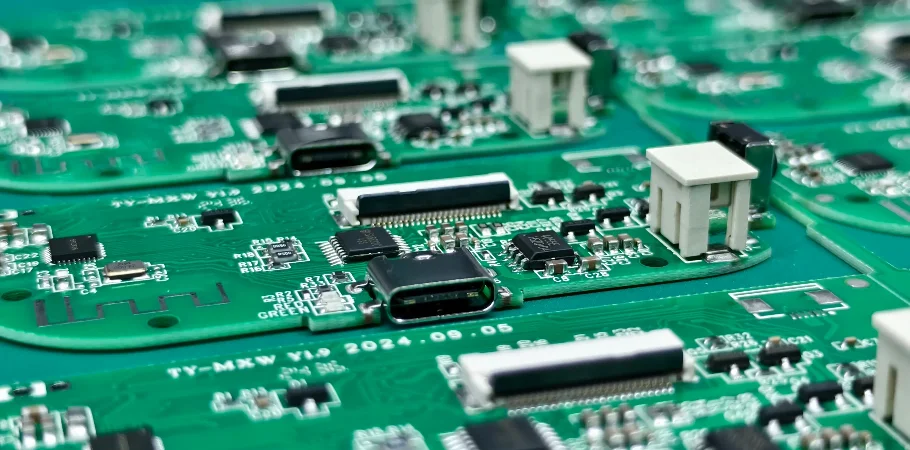

| Leiterbahn-/Abstandsbreite | ≥ 5mil (0,127mm) gewährleistet eine hohe Ausbeute bei Verwendung von Standardätzverfahren. < 4mil erfordert LDI (Laser Direct Imaging) und strengere Qualitätskontrolle, was die Kosten um 15-25% erhöht. |

| Mindestbohrungsgröße | ≥ 0,3mm ermöglicht mechanisches Bohren. < 0,2mm erfordert oft Laserbohren oder fortschrittliches mechanisches Bohren, was die Produktionsgeschwindigkeit erheblich verlangsamt. |

| Lötstopplackfarbe | Grün ist der Industriestandard. Es härtet am schnellsten aus und wird in den höchsten Stückzahlen gedruckt. Andere Farben (Rot, Blau, Schwarz) führen oft zu Batching-Verzögerungen oder Einrichtungsgebühren. |

| Oberflächenveredelung | HASL (verbleit) ist am günstigsten. ENIG verursacht zusätzliche Kosten, gewährleistet aber flache Pads für BGA. Tauchsilber ist eine Mittelklasse-Option für HF, hat aber eine kürzere Haltbarkeit. |

Regeln und Spezifikationen für die kostengünstige Leiterplattenfertigung

Die Einhaltung spezifischer Designregeln ist der effektivste Weg, Kosten zu kontrollieren. Diese Regeln stellen sicher, dass Ihre Platine auf dem "Standard-Förderband" bleibt, anstatt für eine Sonderbehandlung beiseitegelegt zu werden.

| Regelkategorie | Empfohlener Wert (kostengünstig) | Warum es wichtig ist | Wie zu überprüfen |

|---|---|---|---|

| Lagenanzahl | 2, 4 oder 6 Lagen | Standard-Lagenaufbauten werden zusammengefasst. Ungerade Lagenanzahlen (z.B. 3 oder 5) werden als die nächste gerade Zahl (4 oder 6) gefertigt, jedoch mit verschwendeter Kupferätzung. | Überprüfen Sie den Lagenaufbau-Manager im EDA-Tool. |

| Plattendicke | 1,6 mm (0,062") | Dies ist die gängigste Kerndicke. Dünnere (0,8 mm) oder dickere (2,0 mm+) erfordern einen spezifischen Kernbestand. | Messen Sie das Platinenprofil im 3D-Viewer. |

| Kupfergewicht | 1oz (35µm) | Standardmaterial. 2oz+ erfordert Protokolle für schwere Kupferätzung und größere Abstandsregeln. | Überprüfen Sie die Lagenaufbau-Definition. |

| Via-Typ | Nur Durchkontaktierungen | Blind- und Buried-Vias erfordern eine sequentielle Laminierung (mehrere Presszyklen), was die Leiterplattenkosten oft verdoppelt. | Überprüfen Sie die Bohrtabelle auf "Tiefe" oder "Start/Stopp"-Lagen. |

| Schlitze/Ausschnitte | > 1,0 mm Breite | Fräser, die kleiner als 1,0 mm sind, brechen leicht und arbeiten langsamer. | Messen Sie die Schlitzbreite in der mechanischen Lage. |

| Nutzenbildung | V-Nut bevorzugt | V-Nutung ermöglicht keinen Abstand zwischen den Platinen, wodurch die Plattenausnutzung im Vergleich zum Stegfräsen, das Lücken erfordert, maximiert wird. | Anzeigen Richtlinien für den Leiterplattenfertigungsprozess. |

Schritte zur Implementierung einer kostengünstigen Leiterplattenfertigung

Die Implementierung einer kostengünstigen Strategie erfordert Maßnahmen in der Schaltplan- und Layoutphase, nicht nur in der Einkaufsphase.

Implementierungsprozess

Schritt-für-Schritt-Ausführungsanleitung

Prüfen Sie vor dem Routing, ob Sie wirklich 6 Lagen benötigen. Kann eine optimierte Platzierung 4 Lagen ermöglichen? Halten Sie sich an Standard-Dielektrikumsdicken (z.B. Prepreg 7628 oder 2116), um zusätzliche Kosten für kundenspezifische Impedanzen zu vermeiden.

Stellen Sie die DRC (Design Rule Check) Ihres EDA-Tools auf 5mil/5mil Leiterbahn/Abstand und 0,3mm Mindestloch ein. Verstoßen Sie nur in bestimmten dichten Bereichen (z.B. unter einem BGA) dagegen, wenn dies unbedingt erforderlich ist.

Gestalten Sie Ihre Platinenform so, dass sie sich kacheln lässt oder effizient auf eine Standard-Arbeitsplatte (typischerweise 18"x24" oder 21"x24") passt. Verwenden Sie V-Nut (Ritzen) für rechteckige Platinen, um Abfall zwischen den Einheiten zu vermeiden.

Reichen Sie Gerber-Dateien für eine [DFM-Richtlinien](/en/resources/dfm-guidelines)-Überprüfung ein. Wir suchen nach "Säurefallen", Splittern und isoliertem Kupfer, die zu Ertragsverlusten führen könnten, damit Sie diese beheben können, bevor die Preisgestaltung abgeschlossen ist.

Fehlerbehebung bei der kostengünstigen Leiterplattenfertigung

Selbst bei einer kostengünstigen Designabsicht können Probleme auftreten, die den Endpreis in die Höhe treiben oder Verzögerungen verursachen. Hier erfahren Sie, wie Sie häufige Reibungspunkte beheben können.

1. Hohe Ausschussrate (Ertragsverlust)

Wenn Ihr Angebot höher ist als erwartet, überprüfen Sie die Größe Ihres Ringrings. Wenn Sie ein 0,3-mm-Via mit einem 0,4-mm-Pad verwenden, beträgt der Ringring nur 0,05 mm (2 mil). Dies ist extrem eng für die mechanische Bohranmeldung.

- Lösung: Vergrößern Sie die Via-Pads auf mindestens 0,15 mm (6 mil) größer als das Bohrlöcher (z.B. 0,3 mm Bohrung / 0,45 mm Pad).

2. Platinenverzug

Die Verwendung einer dünnen Platine (z.B. 1,0 mm) mit ungleichmäßiger Kupferverteilung (z.B. eine durchgehende Massefläche auf der Unterseite und spärliche Leiterbahnen auf der Oberseite) führt während des Reflow-Lötens zu Verbiegungen. Dies beeinträchtigt die Bestückungsausbeute.

- Lösung: Verwenden Sie "Copper Thieving" (Rasterung) auf offenen Flächen, um die Kupferdichte zwischen der oberen und unteren Lage auszugleichen.

3. Lötstopplack-Stege

Das Design sehr schmaler Lötstopplack-Stege zwischen Pads (z.B. zwischen Fine-Pitch-IC-Pins) führt oft dazu, dass sich der Lack ablöst oder nicht haftet.

- Lösung: Wenn der Abstand zwischen den Pads weniger als 4 mil beträgt, definieren Sie die Maske als "Gruppenöffnung" (eine große Öffnung für eine Reihe von Pins) anstatt als einzelne Öffnungen.

6 Wesentliche Regeln für die kostengünstige Leiterplattenfertigung (Spickzettel)

| Regel / Richtlinie | Warum es wichtig ist (Physik/Kosten) | Zielwert / Aktion |

|---|---|---|

| Standardmaterial (FR4) | Spezialmaterialien (Rogers, Polyimid) haben hohe Mindestbestellmengen und Abfallkosten. | FR4 TG150 |

| Leiterbahn-/Abstandsbreite | Engere Abstände reduzieren die Ätzleistung und erfordern eine langsamere Inspektion. | ≥ 5mil / 5mil |

| Mindestbohrungsgröße | Kleine Bohrer brechen oft und begrenzen die Stapelhöhe (Stapelbohren). | ≥ 0.3mm (12mil) |

| Oberflächenveredelung | Gold (ENIG) erfordert teure Chemie. HASL ist rein mechanisch. | HASL (Bleifrei oder SnPb) |

| Lötstopplackfarbe | Grün wird in kontinuierlichen Chargen gedruckt. Andere Farben erfordern Produktionsunterbrechungen/Reinigung. | Grün |

| Plattenauslastung | Sie zahlen für den Abfall. Schlechte Verschachtelung erhöht die Stückkosten. | > 80% Effizienz |

FAQ

F: Bedeutet "kostengünstig", dass die Leiterplatte schneller ausfällt?

A: Nein. Tatsächlich sind Standard-"kostengünstige" Spezifikationen (breitere Leiterbahnen, größere Vias) oft robuster und zuverlässiger als High-Tech-, hochdichte Designs, da sie weniger empfindlich gegenüber Fertigungsschwankungen sind.

F: Welche Oberflächenveredelung ist die absolut günstigste?

A: HASL (Heißluft-Lötverlötung) mit Blei ist im Allgemeinen am günstigsten, gefolgt von bleifreiem HASL. OSP (Organisches Lötbarkeitskonservierungsmittel) ist ebenfalls sehr günstig, hat aber eine kürzere Haltbarkeit und ist empfindlich gegenüber Handhabung.

F: Wie stark beeinflusst die Farbe des Lötstopplacks den Preis? A: Während der Materialkostenunterschied vernachlässigbar ist, variieren die Prozesskosten. Grün ist Standard. Die Wahl von Mattschwarz oder Lila kann die Lieferzeit oder die Kosten für Kleinserien um 10-20% erhöhen, da die Fabrik die Linie anhalten, die Siebe reinigen und die Tinten wechseln muss.

F: Kann ich kostengünstige Fertigung für impedanzkontrollierte Leiterplatten verwenden?

A: Ja, aber Sie müssen sich an Standard-Stackups halten. Wenn Sie eine spezifische Impedanz benötigen, die die Fabrik zwingt, eine nicht-standardmäßige Prepreg-Dicke oder einen Kern zu verwenden, steigen die Kosten. Verwenden Sie unseren Impedanzrechner, um eine Übereinstimmung mit Standardmaterialien zu finden.

F: Wie erhalte ich am besten ein Angebot?

A: Besuchen Sie unsere Angebotsseite und laden Sie Ihre Gerbers hoch. Stellen Sie sicher, dass Sie, wo immer möglich, "Standard Spezifikation" angeben, um die wettbewerbsfähigsten Preise zu sehen.

Angebot anfordern / DFM-Überprüfung für kostengünstige Leiterplattenfertigung

Bereit, Ihre Produktionskosten zu optimieren? Senden Sie Ihr Design an APTPCB für eine umfassende DFM-Überprüfung. Wir werden Kostentreiber hervorheben und Alternativen vorschlagen.

Bitte geben Sie an:

- Gerber-Dateien: RS-274X-Format bevorzugt.

- Fertigungszeichnung: Angabe von Material (FR4), Dicke (1,6 mm) und Oberfläche.

- Menge: Prototypen (5-100) vs. Massenproduktion (1000+) Preise unterscheiden sich erheblich.

- Nutzenanforderung: Teilen Sie uns mit, ob wir es für Sie nutzen sollen (V-Nut oder Stegfräsung).

Fazit

Kostengünstige Leiterplattenfertigung bedeutet nicht, Abstriche zu machen; es geht um intelligente Ingenieurskunst. Indem Sie Ihr Design auf den optimalen Bereich der Fertigungsmöglichkeiten abstimmen – Standardmaterialien, robuste Geometrien und effiziente Nutzen – können Sie erhebliche Kosteneinsparungen erzielen und gleichzeitig die Zuverlässigkeit Ihres Produkts verbessern.

Bei APTPCB helfen wir Kunden täglich, diese Kompromisse zu bewältigen. Ganz gleich, ob Sie ein IoT-Gerät skalieren oder einen Consumer-Gadget prototypisieren, die Prinzipien des DFM sind Ihr bestes Werkzeug zur Kostenkontrolle.

Gezeichnet, Das Ingenieurteam von APTPCB