Contenido

- Aspectos clave

- PCB Ethernet 100G: definicion y alcance

- PCB Ethernet 100G: reglas y especificaciones

- PCB Ethernet 100G: pasos de implementacion

- PCB Ethernet 100G: solucion de problemas

- Checklist de calificacion de proveedores: como evaluar a su fabricante

- Glosario

- 6 reglas esenciales para PCB Ethernet 100G (chuleta)

- FAQ

- Solicite una cotizacion / revision DFM para un PCB Ethernet 100G

- Conclusion

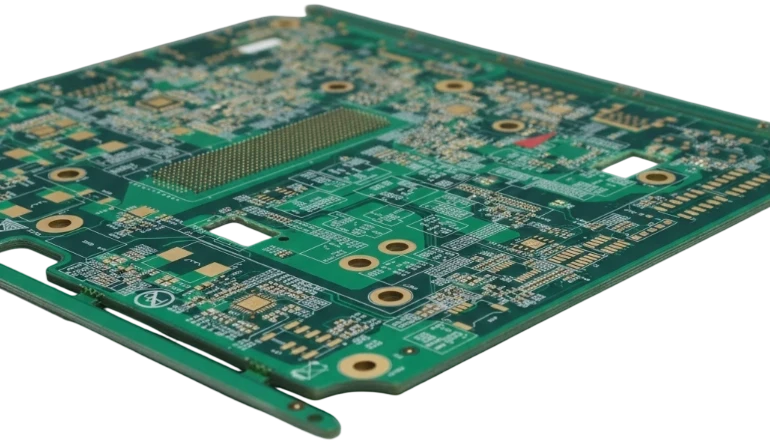

En el mundo del networking de alta velocidad, un PCB Ethernet 100G no es simplemente una tarjeta estandar con tolerancias mas cerradas. Es un componente de precision en el que cada micron de cobre y cada trama de fibra de vidrio afectan la integridad de la senal. Estas placas estan disenadas para soportar tasas de transmision de 100 Gigabits por segundo, normalmente mediante cuatro lanes de 25 Gbps en NRZ o dos lanes de 50 Gbps en PAM4. A estas frecuencias, la pista del PCB se comporta menos como un cable simple y mas como una linea de transmision, donde la perdida dielectrica, el skin effect y los via stubs pueden destruir por completo el eye diagram antes de llegar al receptor.

Como Senior CAM Engineer en APTPCB, reviso cientos de disenos de alta velocidad cada ano. La diferencia entre un prototipo 100G funcional y una placa fallida suele reducirse a la seleccion del material, es decir, alejarse del FR4 estandar, y a la gestion fisica de las transiciones de senal a traves de vias. Esta guia cubre las reglas criticas de diseno y fabricacion necesarias para lograr exito en la primera pasada.

Respuesta rapida

Para que un PCB Ethernet 100G funcione, debe controlar con rigor la insertion loss y la return loss a lo largo de la frecuencia de Nyquist, tipicamente 12.89 GHz para 25G NRZ.

- Regla de material: no use FR4 estandar (Tg170). Debe usar laminados "Low Loss" o "Ultra Low Loss", por ejemplo Panasonic Megtron 6/7, Isola Tachyon o la serie Rogers RO4000, con un Dissipation Factor (Df) < 0.005.

- Riesgo critico: via stubs. Cualquier porcion no usada de un via pasante actua como una antena y genera resonancia que destruye la senal. Debe usar backdrilling o blind/buried vias para reducir los stubs a < 10 mil (0.25 mm).

- Verificacion: el control de impedancia no basta. Necesita ensayos de Insertion Loss con un VNA (Vector Network Analyzer) para verificar la calidad real de la linea de transmision.

- Perfil del cobre: especifique foil de cobre VLP o HVLP para minimizar perdidas por skin effect.

- Stackup: use siempre un stackup simetrico con pares diferenciales estrechamente acoplados y referenciados a planos de tierra solidos.

Aspectos clave

- El material importa mucho: cambiar de FR4 estandar a Megtron 6 puede mejorar la insertion loss en mas del 50 % a 12 GHz.

- El backdrilling es obligatorio: para conectores through-hole en backplanes gruesos, es la forma mas rentable de eliminar stubs que destruyen la senal.

- Efecto del tejido de fibra: a 25 Gbps o mas por lane, el patron del vidrio importa. Use "spread glass" como 1067 o 1078, o enrute con un pequeno angulo de 10° para evitar skew.

- Acabado superficial: ENIG o immersion silver son preferibles por su planitud; evite HASL por su irregularidad, que afecta la impedancia.

- Tolerancias: los disenos 100G requieren control de impedancia de ±5 % o mejor, mas estricto que el ±10 % estandar.

PCB Ethernet 100G: definicion y alcance

Un PCB Ethernet 100G se define por su capacidad para soportar IEEE 802.3bj (100GBASE-KR4) o 802.3bm. Aunque "100G" se refiere al rendimiento agregado, el reto real esta en la velocidad por lane. La mayoria de las implementaciones 100G usan 4 lanes de 25 Gbps con senalizacion NRZ. Las mas nuevas pueden emplear 2 lanes de 50 Gbps con PAM4.

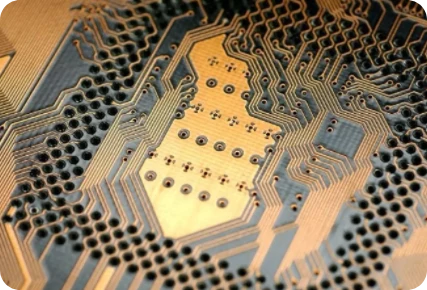

La fisica de senales de 25+ Gbps significa que el propio material de la placa absorbe energia de la senal, es decir, genera perdida dielectrica, y que la rugosidad del cobre incrementa la resistencia a altas frecuencias por skin effect. Ademas, el margen de error temporal cae a picosegundos. Si las ramas positiva y negativa de un par diferencial no estan perfectamente igualadas en longitud, o si una pista cruza fibra de vidrio y la otra resina, la senal llega fuera de fase. El ojo se cierra y aparecen errores de datos.

En APTPCB, clasificamos las placas 100G como "Ultra High-Speed", lo que exige ciclos de laminacion y protocolos de perforado especificos para que la tarjeta fisica coincida con los datos de simulacion.

Palanca tecnica / de decision → impacto practico

| Palanca / especificacion | Impacto practico (yield/costo/confiabilidad) |

|---|---|

| Df del laminado (Dissipation Factor) | Define directamente la longitud maxima de pista. Un Df bajo (<0.004) permite trazas mas largas, pero aumenta el costo del material entre 2 y 3 veces frente a FR4. |

| Rugosidad del foil de cobre (VLP/HVLP) | Un cobre mas liso reduce insertion loss a altas frecuencias. Es esencial para recorridos superiores a 10 pulgadas a 25 GHz. |

| Backdrilling (eliminacion de stubs) | Elimina stubs resonantes. Es obligatorio para la integridad de la senal, pero agrega un paso de perforado y requiere holguras de diseno especificas. |

| Estilo de tejido de vidrio (1067/1078) | Usar "spread glass" minimiza el Fiber Weave Effect y el skew, sin necesidad de routing zig-zag complejo. |

PCB Ethernet 100G: reglas y especificaciones

Disenar para 100G exige reglas estrictas sobre geometria de trazas y materiales. A continuacion se muestra el conjunto de especificaciones que recomendamos en APTPCB para fabricacion.

| Regla / parametro | Valor recomendado | Por que importa | Como verificar |

|---|---|---|---|

| Impedancia diferencial | 85Ω o 100Ω ±5 % | Los desajustes causan reflexiones (Return Loss) y reducen la potencia de la senal en el receptor. | TDR en coupons |

| Ancho / separacion de traza | 4 mil / 5 mil (min.) | Un acoplamiento mas cerrado reduce crosstalk; el ancho afecta la perdida por skin effect. | AOI y microseccion |

| Longitud de via stub | < 10 mil (0.25 mm) | Los stubs largos actuan como notch filters y destruyen frecuencias concretas. | Inspeccion X-Ray y registros de profundidad de backdrill |

| Skew intra-par | < 5 mil (aprox. 0.7 ps) | El desajuste de fase cierra el eye diagram. | Revision en software de diseno y medicion VNA |

| Material Dk / Df | Dk aprox. 3.0-3.6 / Df < 0.004 | Dk bajo reduce retardo de propagacion; Df bajo reduce atenuacion. | Certificacion de hoja de datos IPC-4101 |

| Plano de referencia | Cobre solido (GND) | Los splits en el plano de referencia crean bucles inductivos grandes y EMI. | Inspeccion visual de archivos Gerber |

Para stackups complejos, utilizar pronto nuestros servicios de PCB Stack-up ayuda a validar que los objetivos de impedancia sean alcanzables con espesores dielectricos estandar.

PCB Ethernet 100G: pasos de implementacion

Implementar un diseno 100G es un proceso lineal. Saltarse un paso suele terminar en una nueva iteracion de placa.

Proceso de implementacion

Guia paso a paso

Seleccione un laminado low-loss como Megtron 6. Defina el numero de capas para que cada capa de senal de alta velocidad tenga una referencia de tierra solida adyacente. Calcule anchos de traza para 100Ω.

Rutee primero los pares diferenciales 100G. Minimice vias. Use teardrops en pads. Asegure que las zonas de breakout de BGA mantengan impedancia y referencia a tierra. Evite giros de 90°; use 45° o arcos.

Ejecute simulaciones post-layout. Revise NEXT/FEXT y return loss. Identifique via stubs superiores a 10 mil y marquelos para backdrilling en las notas de fabricacion.

Envie Gerber con drill charts especificos para backdrilling. Solicite reportes TDR y, si es posible, pruebas SET2DIL o SPP para verificar insertion loss sobre cupones.

PCB Ethernet 100G: solucion de problemas

Incluso con un buen diseno, pueden aparecer problemas durante las pruebas. Estos son los modos de falla mas comunes en enlaces 100G y como corregirlos.

1. Alta tasa de error de bit (BER)

Si el enlace establece pero pierde paquetes, el problema suele estar en jitter o crosstalk.

- Causa: trazas demasiado cerca de senales agresoras, como convertidores DC-DC u otros relojes de alta velocidad.

- Correccion: aumente el espaciado entre pares diferenciales. La regla 3W a menudo no basta; apunte a 4W o 5W. Revise tambien si hay huecos en el plano de referencia.

2. Atenuacion de senal (falla de Insertion Loss)

La senal es demasiado debil en el receptor.

- Causa: la traza es demasiado larga para el material elegido o el cobre es demasiado rugoso.

- Correccion: si no puede acortar la traza, cambie a un material con Df mas bajo, por ejemplo de Megtron 4 a Megtron 7. Especifique foil HVLP.

3. Resonancia / notch filtering

La senal se ve bien a baja frecuencia pero desaparece en una frecuencia alta concreta, por ejemplo 12 GHz.

- Causa: via stubs. La porcion no usada del via entra en resonancia a un cuarto de longitud de onda de la frecuencia de la senal.

- Correccion: implemente Backdrilling para eliminar el stub. Asegure una tolerancia ajustada de profundidad, tipicamente ±0.05 mm.

Checklist de calificacion de proveedores: como evaluar a su fabricante

No todos los fabricantes de PCB pueden cumplir requisitos 100G. Use esta lista para evaluar a su proveedor antes de emitir una orden.

- El fabricante tiene capacidad interna de prueba VNA? Es esencial para verificar insertion loss, no solo impedancia.

- Cual es la tolerancia estandar de profundidad de backdrill? Debe ser ±0.1 mm o mejor, idealmente ±0.05 mm.

- Mantienen laminados high-speed en stock? Pregunte de forma explicita por Megtron 6/7, Rogers 4350 o equivalente. Si deben pedirlo, aumentara el lead time.

- Pueden mantener tolerancia de ancho de traza de +2/-2 mil? El estandar suele ser ±20 %; alta velocidad normalmente exige ±10 % o ±0.5 mil.

- Realizan analisis de microseccion en cada lote? Sirve para verificar espesor de metalizado y consistencia dielectrica.

- Usan inspeccion X-Ray para verificar backdrill? Asi se confirma que el taladro no corto demasiado ni dejo stub excesivo.

Glosario

- Insertion Loss: perdida de potencia de la senal a medida que viaja por la traza, medida en dB. Las frecuencias mas altas sufren mas perdida.

- Return Loss: cantidad de senal reflejada hacia la fuente por desajustes de impedancia. Un return loss alto indica mala integridad de senal.

- Backdrilling: proceso de fabricacion en el que una broca ligeramente mayor que el agujero del via elimina el barrel no utilizado de un via pasante, reduciendo la reflexion.

- PAM4 (Pulse Amplitude Modulation 4-level): esquema de modulacion que transmite dos bits por simbolo, duplicando la tasa de datos frente a NRZ con el mismo ancho de banda, aunque requiere mejor relacion senal/ruido.

- Skew: diferencia temporal entre la llegada de las senales positiva y negativa en un par diferencial. Un skew alto convierte la senal diferencial en ruido de modo comun.

6 reglas esenciales para PCB Ethernet 100G (chuleta)

| Regla / guia | Por que importa (fisica/costo) | Valor objetivo / accion |

|---|---|---|

| Eliminar via stubs | Los stubs actuan como antenas y provocan resonancia severa y perdida de senal a 25 GHz o mas. | Backdrill hasta dejar menos de 10 mil. |

| Usar material low-loss | El FR4 estandar absorbe demasiada energia de senal a altas frecuencias. | Df < 0.005 (por ejemplo Megtron 6) |

| Plano de referencia continuo | La corriente de retorno debe fluir justo debajo de la senal. Las discontinuidades generan picos de inductancia. | Cobre solido sin splits bajo las trazas. |

| Vias de tierra cerca de vias de senal | Proporcionan el camino de retorno cuando la senal cambia de capa. | Coloque el via GND a menos de 30 mil del via de senal. |

| Control de impedancia estricto | Los desajustes causan reflexiones. 100G tolera mucho menos que 10G. | Tolerancia ±5 % frente al ±10 % estandar. |

| Mitigar el fiber weave | Los haces periodicos de vidrio causan skew si una traza corre sobre vidrio y la otra sobre resina. | Use Spread Glass o routing zig-zag. |

FAQ

Q: Puedo usar FR4 estandar para PCB Ethernet 100G?

A: En general, no. Para trazas extremadamente cortas, inferiores a 1 pulgada, podria funcionar, pero FR4 estandar tiene un Dissipation Factor demasiado alto, alrededor de 0.02, y produce demasiada perdida de senal entre 12 y 14 GHz. Conviene usar materiales mid-loss o low-loss como Isola FR408HR o Panasonic Megtron 6.

Q: Cual es la diferencia de costo entre FR4 estandar y materiales high-speed?

A: Laminados como Megtron 6 pueden costar entre 2 y 3 veces mas que FR4 estandar. Sin embargo, el costo del material suele ser una fraccion del valor total de la tarjeta, y el costo de un prototipo fallido por problemas de integridad de senal es mucho mayor.

Q: Necesito blind y buried vias para 100G?

A: No necesariamente. Aunque blind/buried vias son excelentes para reducir stubs, aumentan los ciclos de laminacion y el costo. Backdrilling es una alternativa mas economica para vias pasantes y suele ofrecer resultados similares en aplicaciones 100G.

Q: Como calculo la impedancia correcta para 100G?

A: Puede usar una calculadora de impedancia, pero para 100G recomendamos consultar con su fabricante. Nosotros usamos field-solver software como Polar SI9000, que considera contenido de resina, rugosidad de cobre y etchback para entregar el ancho exacto de traza.

Q: Que acabado superficial es mejor para PCB 100G?

A: ENIG o immersion silver son las opciones recomendadas. Aportan una superficie muy plana para montaje de componentes y no anaden espesor irregular a las trazas como HASL, que puede alterar la impedancia.

Q: Cual es la longitud maxima de traza para 100G en un PCB?

A: Depende del material. Sobre FR4 estandar puede lograr 2 a 3 pulgadas. En Megtron 6 a menudo es posible llegar a 10 a 15 pulgadas o mas, dependiendo de las capacidades del retimer o driver. Se requiere simulacion para definir el alcance exacto.

Solicite una cotizacion / revision DFM para un PCB Ethernet 100G

Listo para llevar su diseno de alta velocidad a produccion? En APTPCB nos especializamos en Advanced PCB Manufacturing para aplicaciones de data center y networking.

Para obtener una cotizacion precisa y una revision DFM, envienos:

- Archivos Gerber (formato RS-274X preferido)

- Fabrication Drawing con drill chart y capas de backdrill

- Detalles de stackup como numero de capas, material deseado y requisitos de impedancia

- Netlist (IPC-356) para verificacion electrica

Conclusion

Disenar un PCB Ethernet 100G exige cambiar la mentalidad de "conectar puntos" a "gestionar lineas de transmision". Si selecciona materiales low-loss adecuados, controla estrictamente los via stubs mediante backdrilling y mantiene tolerancias de impedancia cerradas, podra lograr una placa confiable a 25 Gbps por lane y mas alla.

No trate la integridad de la senal como algo secundario. Involucre a su fabricante desde el principio para validar stackup y reglas de diseno.

Firmado, el equipo de ingenieria de APTPCB