يتطلب توسيع لوحة PCB ذات واجهة CXL 3.0 إلى إنتاج كمي انتقالًا صارمًا من أساليب التصنيع التقليدية إلى تصنيع عالي الدقة للغاية. ومع وصول معدلات البيانات إلى 64 GT/s باستخدام إشارات PAM4، يكاد هامش الخطأ في التحكم في المعاوقة، واختيار المواد، وتفاوتات الحفر أن يختفي تمامًا. ويقدّم هذا الدليل الحدود الرقمية الدقيقة، وضوابط العملية، وخطوات التحقق اللازمة لتحقيق إنتاجية مرتفعة وسلامة إشارة مستقرة في الإنتاج الحجمي.

إجابة سريعة (30 ثانية)

- القاعدة الحاسمة: حافظوا على المعاوقة التفاضلية عند 85 Ω ±5%؛ فالتفاوت القياسي البالغ ±10% لا يكفي لإشارات PAM4 في CXL 3.0.

- متطلبات المادة: استخدموا مواد Ultra-Low Loss مثل Megtron 7/8 أو Tachyon 100G مع Df < 0.002 عند 10 جيجاهرتز.

- المشكلة الأساسية: يؤدي الجزء المتبقي من الفتحة إذا تجاوز 6 mil (0.15 مم) إلى رنين قاتل؛ ويصبح الحفر الخلفي إلزاميًا في اللوحات الخلفية السميكة.

- التحقق: نفّذوا اختبار TDR بنسبة 100% على عينات الاختبار مع أخذ عينات عشوائية من اللوحات الفعلية للتحقق من فقدان الإدراج.

- الحالة الحدّية: إذا تجاوز طول المسار 10 بوصات، ففكّروا في استخدام نحاس منخفض الخشونة (HVLP/VLP، Rz < 2 µm) لتقليل خسائر تأثير السطح.

- عنصر DFM: حدّدوا تفاوت عمق الحفر الخلفي عند ±2 mil لضمان إزالة الجزء المتبقي من الفتحة من دون الإضرار بالطبقات الداخلية النشطة.

أبرز النقاط

- حساسية PAM4: يستخدم CXL 3.0 تعديلًا نبضيًا رباعي المستويات، ما يقلل نسبة الإشارة إلى الضوضاء مقارنةً بـ NRZ.

- دقة ترتيب الطبقات: يجب أن يبقى تسجيل الطبقات ضمن 3 mil حتى لا تظهر انقطاعات في المعاوقة.

- تقنية الحفر: تتطلب vias ذات نسبة الارتفاع الكبيرة، حتى 20:1، تقنيات حفر ميكانيكي متقدمة أو حفرًا بالليزر.

- التشطيب السطحي: يُفضّل ENIG أو ENEPIG بسبب تسطح السطح؛ أما HASL فغير مقبول لأن السطح غير المستوي يضعف الإشارات عالية التردد.

- النظافة: يجب ضبط التلوث الأيوني بدقة شديدة لمنع الهجرة الكهروكيميائية في التصميمات عالية الكثافة.

- الاختبارات: غالبًا ما تُطلب قياسات VNA حتى 32 جيجاهرتز لتوصيف القناة.

المحتويات

- التعريف والنطاق (ما هو وما ليس كذلك)

- القواعد والمواصفات (المعاملات الأساسية والحدود)

- خطوات التنفيذ (نقاط ضبط العملية)

- معالجة الأعطال (أنماط الفشل وطرق التصحيح)

- كيفية الاختيار (قرارات التصميم والمفاضلات)

- الأسئلة الشائعة (التكلفة والمهلة والمواد والاختبارات ومعايير القبول)

- المسرد (المصطلحات الأساسية)

- طلب عرض سعر (مراجعة DFM + التسعير)

- الخلاصة (الخطوات التالية)

التعريف والنطاق (ما هو وما ليس كذلك)

ينطبق عندما:

- يجري تصنيع اللوحات الأم للخوادم، أو بطاقات المسرّعات، أو وحدات توسيع الذاكرة التي تدعم معيار Compute Express Link (CXL) 3.0.

- يستخدم التصميم الطبقة الفيزيائية PCIe 6.0 بسرعة 64 GT/s.

- يتضمن ترتيب طبقات اللوحة من 12 إلى 32 طبقة أو أكثر، وغالبًا ما يحتاج إلى HDI أو بنى لوحات خلفية سميكة.

- تفرض متطلبات سلامة الإشارة استخدام رقائق Ultra-Low Loss (ULL) مع تحكم صارم في المعاوقة.

- تمتد أحجام الإنتاج من تشغيلات NPI الصغيرة حتى تصنيع PCB للإنتاج الكمي.

لا ينطبق عندما:

- يكون التصميم مخصصًا لـ CXL 1.0/1.1 أو PCIe 4.0/5.0 عند 32 GT/s بإشارات NRZ، حيث قد تكفي مواد Low Loss القياسية.

- تكون سرعة الواجهة أقل من 16 GT/s، ما يسمح بتفاوتات أوسع مثل ±10% في المعاوقة.

- تُستخدم مواد FR-4 قياسية ذات Tg بين 130 و150 °م مع Df أعلى من 0.015، وهو مرتفع جدًا لهذه الترددات.

- تكون اللوحة مجرد PCB استهلاكية بسيطة من طبقتين إلى ست طبقات من دون متطلبات معاوقة مضبوطة.

القواعد والمواصفات (المعاملات الأساسية والحدود)

يتطلب تحقيق الامتثال لـ CXL 3.0 في الإنتاج الكمي التزامًا صارمًا بالمعايير الفيزيائية والكهربائية. يوضح الجدول التالي القواعد التصنيعية غير القابلة للتفاوض.

| القاعدة | القيمة أو النطاق الموصى به | لماذا هي مهمة | كيفية التحقق | ماذا يحدث إذا أُهملت |

|---|---|---|---|---|

| المعاوقة التفاضلية | 85 Ω ± 5% | تفرض مواصفة CXL 3.0/PCIe 6.0 قيمة 85 Ω لتقليل فقدان الانعكاس. | قياس TDR على عينات الاختبار. | تزيد الانعكاسات من BER وتفشل عملية تدريب الرابط. |

| فقد المادة (Df) | < 0.002 عند 10 جيجاهرتز | يجب تقليل اضمحلال الإشارة عالية التردد إلى الحد الأدنى عند 64 GT/s. | طريقة IPC-TM-650 2.5.5.5 أو شهادة بيانات المادة. | تؤدي خسارة الإدراج المفرطة إلى إغلاق عين الإشارة، ولا يتفاوض الرابط على السرعة الصحيحة. |

| خشونة النحاس | Rz < 2.0 µm (HVLP/VLP) | عند 16-32 جيجاهرتز يدفع تأثير السطح التيار إلى سطح الموصل، والنحاس الخشن يزيد الفقد. | تحليل SEM لرقاقة النحاس. | زيادة خسارة الإدراج وتشوه الطور. |

| طول الجزء المتبقي من الفتحة | < 6 mil (0.15 مم) | يعمل الجزء المتبقي كهوائي أو مرشح ويسبب هبوطًا رنينيًا في الاستجابة الترددية. | تحليل مقطع عرضي أو فحص بالأشعة السينية. | يدمر الرنين عند تردد Nyquist سلامة الإشارة. |

| Skew داخل الزوج | < 5 ps | يجب أن تصل الإشارتان التفاضليتان في الوقت نفسه للحفاظ على رفض الوضع المشترك. | قياس VNA أو محاكاة زمن الانتقال. | يحدث تحويل نمط وتنغلق عين الإشارة. |

| تفاوت عمق الحفر الخلفي | ± 2 mil (0.05 مم) | يضمن إزالة الجزء المتبقي من الفتحة من دون قطع الطبقة الداخلية النشطة. | فحص ثقوب الحفر الخلفي بالأشعة السينية. | إما يبقى الجزء المتبقي أطول من اللازم أو تُقطع الإشارة النشطة. |

| تسجيل الطبقات | ± 3 mil | يؤثر سوء المحاذاة في المعاوقة وقد يسبب قصرًا في مناطق BGA عالية الكثافة. | التحقق بالحفر بالأشعة السينية مع microsection. | انقطاعات في المعاوقة وقصور كهربائي محتمل. |

| جسر قناع اللحام | حد أدنى 3 mil (0.075 مم) | يمنع جسور اللحام على footprint موصلات CXL ذات الخطوة الدقيقة. | AOI. | جسور لحام أثناء التجميع ودوائر قصر. |

| نسبة الارتفاع إلى العرض في الطلاء | حد أقصى 20:1 | تضمن سمكًا كافيًا للنحاس في barrel الخاص بالـ via العميقة. | تحليل microsection. | تشقق barrel أثناء reflow وحدوث دوائر مفتوحة متقطعة. |

خطوات التنفيذ (نقاط ضبط العملية)

يتطلب تحويل تصميم CXL 3.0 إلى إنتاج كمي ضوابط عملية محددة.

1. اختيار المادة والتحقق منها

- الإجراء: اختاروا مواد مثل Panasonic Megtron 7/8 أو Isola Tachyon 100G أو ما يعادلها.

- التحقق: افحصوا نمط زجاج طبقة الـ prepreg، مثل 1035 أو 1067، لضمان أن محتوى الراتنج يقلل تفاوت التأخير الناتج عن تأثير نسيج الألياف.

- معيار القبول: تفاوت Dk ±0.05؛ وDf < 0.002.

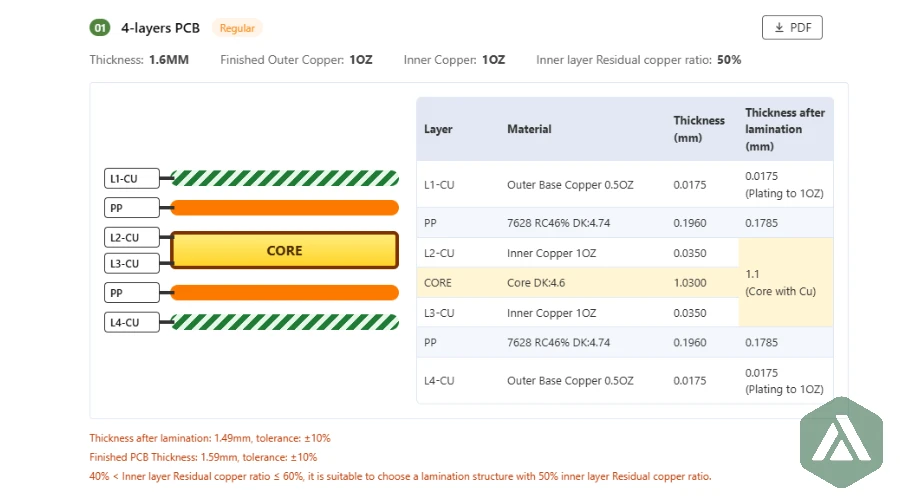

2. Stackup ونمذجة المعاوقة

- الإجراء: استخدموا field solver ثنائي أو ثلاثي الأبعاد مثل Polar SI9000 لحساب عرض المسارات.

- التحقق: خذوا في الاعتبار تدفق الراتنج والسمك النهائي للنحاس بعد الكبس. وفي CXL 3.0 تكون مسارات 85 Ω غالبًا أعرض قليلًا من مسارات 100 Ω القياسية.

- معيار القبول: يجب أن تطابق نتائج المحاكاة هدف 85 Ω ضمن ±1 Ω قبل بدء التصنيع. راجعوا دليل ترتيب طبقات PCB.

3. تصوير الطبقات الداخلية والحفر الكيميائي

- الإجراء: استخدموا Laser Direct Imaging (LDI) لتحقيق دقة عالية.

- التحقق: يجب ضبط معاملات تعويض الحفر الكيميائي بدقة. كما يجب التحكم في تفاوت عرض المسار عند ±0.5 mil أو أفضل.

- معيار القبول: يجب ألا يظهر AOI أي تضيق أو بروز على الخطوط عالية السرعة.

4. التصفيح وتسجيل الطبقات

- الإجراء: استخدموا pin-lam أو أنظمة محاذاة بصرية عندما يتجاوز عدد الطبقات 20 طبقة.

- التحقق: تأكدوا بالأشعة السينية من محاذاة الطبقات بعد التصفيح.

- معيار القبول: يجب أن يبقى التسجيل بين الطبقات ضمن 3 mil حتى تصيب via pad الطبقة المستهدفة في المركز.

5. الحفر والحفر الخلفي

- الإجراء: احفروا الثقوب النافذة ثم نفذوا حفرًا خلفيًا بعمق مضبوط لإزالة الجزء المتبقي من الثقب.

- التحقق: راقبوا عمر لقمة الحفر لمنع خشونة جدران الثقب.

- معيار القبول: يجب أن يبقى عمق الحفر الخلفي ضمن ±2 mil من الطبقة المستهدفة.

6. الطلاء والتشطيب السطحي

- الإجراء: استخدموا طلاء نحاس عالي القدرة على الاختراق لضمان سلامة barrel في vias ذات نسبة الارتفاع الكبيرة.

- التحقق: قيسوا سماكة النحاس في منتصف barrel، على ألا تقل عن 0.8 mil أو 20 µm.

- معيار القبول: يجب أن يكون ENIG أو ENEPIG مستويًا بما يكفي لتجميع الموصلات عالية الكثافة.

7. الاختبارات الكهربائية (TDR وVNA)

- الإجراء: نفذوا اختبار قائمة التوصيلات بنسبة 100% واختبار TDR للمعاوقة على قسائم الاختبار.

- التحقق: في CXL 3.0 يُستخدم اختبار VNA على أساس العينات، مثل SET2DIL، لقياس خسارة الإدراج لكل بوصة.

- معيار القبول: المعاوقة 85 Ω ±5%؛ والخسارة ضمن الميزانية، مثل -0.9 dB/بوصة عند 16 جيجاهرتز.

معالجة الأعطال (أنماط الفشل وطرق التصحيح)

في تجميع لوحة PCB ذات واجهة CXL 3.0، تظهر الأعطال غالبًا على شكل مشكلات في سلامة الإشارة بدلًا من مجرد دوائر مفتوحة أو قصور بسيط.

العرض 1: BER مرتفع أو رابط غير مستقر

- السبب المحتمل: طول الجزء المتبقي من الثقب النافذ كبير أكثر من اللازم، فيسبب رنينًا.

- التحقق: افحصوا الثقوب التي خضعت للحفر الخلفي بالأشعة السينية. هل يتجاوز الجزء المتبقي 6 mil؟

- التصحيح: اضبطوا إعدادات عمق الحفر الخلفي.

- الوقاية: حدّدوا بوضوح الطبقات التي يجب عدم المساس بها في بيانات ODB++ وزيدوا مسافة الأمان الخاصة بالحفر الخلفي.

العرض 2: المعاوقة منخفضة باستمرار، مثل 78 Ω بدلًا من 85 Ω

- السبب المحتمل: المسار أعرض من اللازم أو أن العازل أرق من الحساب.

- التحقق: نفذوا مقطعًا عرضيًا للوحة. وقيسوا عرض المسار الفعلي في الأعلى والأسفل وارتفاع العازل.

- التصحيح: عدّلوا معاملات تعويض الحفر الكيميائي للدفعة التالية.

- الوقاية: أجروا مقطعًا مجهريًا على العينة الأولى قبل إطلاق كامل دفعة الإنتاج.

العرض 3: انغلاق مخطط العين رأسيًا

- السبب المحتمل: خسارة إدراج مرتفعة بسبب المادة أو خشونة النحاس.

- التحقق: راجعوا دفعة المادة، مثل التأكد من أنها فعلًا Megtron 7. وتحققوا أيضًا من خشونة رقائق النحاس، أي ما إذا كانت HVLP.

- التصحيح: انتقلوا إلى رقاقة نحاس أنعم أو إلى مادة أقل فقدًا.

- الوقاية: اشترطوا شهادات المادة (CoC) مع كل شحنة.

العرض 4: jitter ناتج عن skew

- السبب المحتمل: تأثير نسيج الألياف عندما تصطف حزم الألياف الزجاجية مع المسارات.

- التحقق: افحصوا نمط الزجاج المستخدم، مثل 106 أو 1080 أو 1035.

- التصحيح: أداروا التصميم 10° مع توجيه متعرج أو استخدموا زجاجًا ممدودًا.

- الوقاية: حدّدوا FR4 بزجاج ممدود أو ما يعادله من أنواع الزجاج عالية المستوى في ملاحظات التصنيع.

العرض 5: BGA pad cratering أو ارتفاع الوسادات

- السبب المحتمل: مادة رقائق هشة مع إجهاد ميكانيكي.

- التحقق: راجعوا Tg وCTE للمادة.

- التصحيح: استخدموا مواد ذات CTE أقل على المحور Z أو حسّنوا متانة الراتنج.

- الوقاية: حسّنوا ملف reflow الخاص بـ BGA/QFN fine pitch لتقليل الصدمة الحرارية.

كيفية الاختيار (قرارات التصميم والمفاضلات)

يؤدي اتخاذ قرارات صحيحة في بداية التصميم إلى خفض الكلفة ورفع الإنتاجية في تصنيع PCB للإنتاج الكمي.

إذا كان طول المسار أقل من 5 بوصات:

- اختيار: قد تكفي مواد متوسطة الفقد مثل Megtron 6 أو IT-968 إذا سمحت ميزانية الفقد.

- المفاضلة: تقلل كلفة المادة، لكنها تترك هامشًا أقل.

إذا تجاوز طول المسار 10 بوصات:

- اختيار: مواد Ultra-Low Loss مثل Megtron 7/8 أو Tachyon 100G مع نحاس HVLP.

- المفاضلة: تكلفة المادة أعلى، لكنها ضرورية للامتثال لـ CXL 3.0.

إذا تجاوز عدد الطبقات 20 طبقة:

- اختيار: مواد High-Tg أعلى من 180 °م ومواد Low-CTE.

- المفاضلة: تقلل من تشقق barrel وpad cratering أثناء دورات reflow المتعددة.

إذا كانت كثافة التوجيه شديدة جدًا، مثل BGA بخطوة 0.4 مم:

- اختيار: تقنية HDI PCB مع stacked microvia.

- المفاضلة: تكلفتها أعلى من البنية ذات الثقوب النافذة، لكنها تحسن سلامة الإشارة عبر تقليل الجزء المتبقي من الثقب بشكل طبيعي.

إذا استُخدمت موصلات press-fit:

- اختيار: تفاوت ثقب أكثر تشددًا عند +0.05/-0.05 مم، ومعه طلاء ذهب صلب أو immersion tin إذا طُلب ذلك.

- المفاضلة: يحتاج إلى إدارة دقيقة جدًا لقِمم الحفر.

إذا كانت الميزانية ضيقة لكن الأداء ما زال حرجًا:

- اختيار: ترتيب طبقات هجين يستخدم مادة ULL للطبقات عالية السرعة وFR4 القياسي لطبقات القدرة والأرضي والإشارات البطيئة.

- المفاضلة: دورة تصفيح أكثر تعقيدًا مع خطر التواء بسبب عدم تطابق CTE.

الأسئلة الشائعة (التكلفة والمهلة والمواد والاختبارات ومعايير القبول)

س: ما مقدار الزيادة التي يضيفها الحفر الخلفي إلى تكلفة لوحات CXL 3.0؟ ج: يضيف الحفر الخلفي عادةً ما بين 10% و20% إلى تكلفة اللوحة العارية. ويتطلب برنامج NC منفصلًا، وآلات متخصصة للتحكم في العمق، وخطوات فحص إضافية بالأشعة السينية.

س: ما المهلة الزمنية المعتادة لمواد Ultra-Low Loss؟ ج: تكون المهلة غالبًا بين أسبوعين وأربعة أسابيع لمواد مثل Megtron 7 أو Tachyon إذا لم تكن متاحة في المخزون. وعند الحاجة إلى لوحة PCB بتسليم سريع يجب التحقق من توفر المادة فورًا.

س: هل يلزم اختبار VNA بنسبة 100% في الإنتاج الكمي؟ ج: لا. فاختبار VNA بنسبة 100% بطيء ومكلف للغاية. وعادةً يُجرى TDR للمعاوقة بنسبة 100%، مع استخدام عينات إحصائية مثل لوحة واحدة لكل دفعة للتحقق من خسارة الإدراج عبر VNA.

س: هل يمكن استخدام FR4 القياسي في تصميمات CXL 3.0؟ ج: لا. يتمتع FR4 القياسي بقيمة Df تقارب 0.020، ما يسبب فقدًا كبيرًا عند 16 جيجاهرتز، أي Nyquist لـ 32 GT/s، وعند 32 جيجاهرتز، أي Nyquist لـ 64 GT/s. لذلك يجب استخدام مواد ذات Df أقل من 0.005.

س: ما الحد الأدنى لعرض المسار المطلوب للحصول على 85 Ω؟ ج: يعتمد ذلك على ترتيب الطبقات، لكن stripline تكون عادة بين 4 و5 mil، أي 0.10-0.127 مم. وتزيد المسارات الأضيق من خسائر تأثير السطح، بينما تتطلب المسارات الأعرض عوازل أكثر سماكة.

س: كيف تتعاملون مع تأثير نسيج الألياف أثناء الإنتاج؟ ج: نستخدم زجاجًا ممدودًا، أي أليافًا مفروشة ميكانيكيًا، أو نوجّه المسارات بزاوية صغيرة، مثل 10°، نسبةً إلى اتجاه النسيج. وبهذا يجري متوسط تغيرات Dk.

س: ما أفضل تشطيب سطحي لتطبيقات CXL 3.0؟ ج: ENIG أو ENEPIG. فهما يقدمان سطحًا مستويًا للمكوّنات الدقيقة ولا يضيفان فقدًا ملحوظًا مثل HASL.

س: ما معيار القبول الخاص بالمعاوقة في الإنتاج الكمي؟ ج: تستخدم IPC Class 2 أو 3 قيمة ±10% بشكل افتراضي في كثير من الحالات، لكن في CXL 3.0 يجب تحديد ±5% صراحةً في ملاحظات التصنيع وفي الرسم المرجعي الرئيسي.

المسرد (المصطلحات الأساسية)

| المصطلح | المعنى | لماذا يهم عمليًا |

|---|---|---|

| PAM4 | تعديل نبضي رباعي المستويات. | يشفّر بتّين في كل UI، ويتطلب SNR وخطية أعلى من NRZ. |

| UI (Unit Interval) | المدة الزمنية لبت واحد أو رمز واحد. | عند 64 GT/s تكون UI قصيرة جدًا، حوالي 15.6 ps، ولذلك يكون هامش jitter محدودًا للغاية. |

| Insertion Loss (IL) | فقدان قدرة الإشارة أثناء انتقالها عبر المسار. | هذا هو العامل الأساسي الذي يحد طول المسار، لذلك يجب تخطيط الميزانية بعناية، مثل -30 dB للقناة الكلية. |

| Return Loss (RL) | جزء الإشارة الذي ينعكس مرة أخرى إلى المصدر. | يحدث بسبب عدم تطابق المعاوقة ويؤدي إلى تدهور عين الإشارة. |

| Backdrilling | إزالة الجزء غير المستخدم من الثقب المعدني النافذ، أي الجزء المتبقي من الثقب. | وهو ضروري في CXL 3.0 عندما تترك الثقوب النافذة أطوالًا رنانة لا يمكن قبولها. |

الخلاصة

يصبح ضبط الإنتاج الكمي للوحة PCB ذات واجهة CXL 3.0 أسهل عندما تُحدَّد المواصفات وخطة التحقق مبكرًا، ثم تُؤكَّد من خلال مراجعة DFM وتغطية الاختبارات. استخدموا القواعد ونقاط الضبط وأنماط معالجة الأعطال المذكورة أعلاه لتقليل حلقات التكرار وحماية الإنتاجية مع زيادة الأحجام. وإذا بقي أي قيد غير محسوم، فاختبروه على دفعة تجريبية صغيرة قبل تثبيت إصدار الإنتاج.