المحتويات

- Highlights

- تقليل تكلفة PCB من دون التضحية بالـ yield: التعريف والنطاق

- تقليل تكلفة PCB من دون التضحية بالـ yield: القواعد والمواصفات

- تقليل تكلفة PCB من دون التضحية بالـ yield: خطوات التنفيذ

- تقليل تكلفة PCB من دون التضحية بالـ yield: troubleshooting

- 6 قواعد اساسية لتقليل التكلفة من دون خسارة yield

- FAQ

- اطلب عرض سعر / مراجعة DFM لتقليل التكلفة من دون التضحية بالـ yield

- الخلاصة

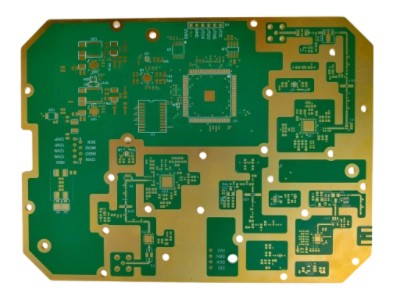

تقليل تكلفة PCB لا يعني خفض الجودة، بل يعني حذف المتطلبات التي ترفع السعر من دون ان تضيف تحسنا حقيقيا في الاداء او الاعتمادية. وفهم كيفية تقليل تكلفة PCB من دون التضحية بالـ yield يتطلب الجمع بين DFM واختيار المواد وحدود العملية الحقيقية في المصنع.

Quick Answer

لكي تقلل تكلفة PCB من دون التضحية بالـ yield، يجب ان يبقى التصميم ضمن قدرات التصنيع القياسية قدر الامكان.

- وحد المواد: استخدم FR4 بدرجة TG150-TG170 ما لم توجد حاجة RF او high-speed حقيقية.

- حسن panelization: استهدف اكثر من 80% من الاستفادة من اللوح.

- قلل ادوات الحفر: كل تغيير اداة يزيد زمن CNC.

- خفف التفاوتات: استخدم +/- 0.10 mm اذا لم تكن بحاجة الى +/- 0.05 mm.

- تجنب HDI: blind و buried vias ترفع التكلفة بشكل واضح.

- افحص DFM: حدد cost drivers قبل طلب التسعير.

Highlights

- استغلال panel: واحد من اهم مصادر التكلفة الخفية.

- عدد الطبقات: تقليل الطبقات لا يفيد اذا اجبرك على استخدام HDI.

- التشطيب السطحي: ENIG موثوق لكنه اغلى من HASL و OSP.

- ادارة via: aspect ratio المناسب يساعد على حماية yield.

تقليل تكلفة PCB من دون التضحية بالـ yield: التعريف والنطاق

يتكون سعر PCB من تكلفة المواد و تكلفة العمليات و خسائر yield. واللوحة الاصغر ليست دائما ارخص اذا كانت تفرض traces بعرض 3 mil او microvias بالليزر او تفاوتات ضيقة جدا.

ويظهر التوفير الحقيقي عندما يبقى التصميم داخل المنطقة الاكثر استقرارا في التصنيع. فلوحة FR4 PCB القياسية مع trace/space عند 5 mil ارخص بكثير من تصميم 3 mil لان عملية etching تكون اكثر ثباتا. كما ان stackup الزوجي افضل من الفردي لانه يقلل خطر warpage.

عامل تقني → اثر عملي

| العامل / المواصفة | الاثر العملي (yield/التكلفة/الاعتمادية) |

|---|---|

| استغلال panel | اثر مرتفع. ضعف الاستغلال يعني دفع ثمن مادة مهدورة. |

| تقنية via | عامل حرج. blind و buried vias تضيف دورات lamination اضافية. |

| Trace / Space | عامل yield. ما دون 3.5 mil يجعل العملية اكثر حساسية بكثير. |

| Surface Finish | تكلفة مقابل assembly. HASL ارخص بينما ENIG اكثر استواء لكنه اغلى. |

| عدد الثقوب وحجمها | زمن الماكينة. كثرة الثقوب او صغر الادوات يرفع زمن CNC. |

تقليل تكلفة PCB من دون التضحية بالـ yield: القواعد والمواصفات

| القاعدة | القيمة الموصى بها | لماذا تهم | كيف تتحقق |

|---|---|---|---|

| Min Trace / Space | ≥ 5 mil / 5 mil | القيم الاقل من 4 mil تجعل etching اكثر صعوبة. | نفذ DRC. |

| Min Mechanical Drill | ≥ 0.25 mm | الادوات الصغيرة تنكسر بسهولة اكبر. | راجع جدول الحفر. |

| Annular Ring | ≥ 5 mil | يقلل خطر breakout. | قارن بين pad و hole size. |

| Layer Count | عدد زوجي | stackup الفردي يزيد احتمالات warpage. | راجع PCB Stackup. |

| Board Thickness | 1.6 mm | السماكات الخاصة اغلى غالبا. | راجع خصائص اللوحة. |

| Copper Weight | 1 oz | النحاس الثقيل يتطلب زمنا اطول في etching. | زد الوزن فقط عند الحاجة. |

تقليل تكلفة PCB من دون التضحية بالـ yield: خطوات التنفيذ

عملية التنفيذ

تسلسل عملي

ابدأ بابسط stackup يحقق المتطلبات الكهربائية.

قلل اطوال traces وعدد crossings و vias.

اضبط الابعاد لزيادة عدد الوحدات على اللوح القياسي.

احذف العمليات الخاصة غير الضرورية.

تقليل تكلفة PCB من دون التضحية بالـ yield: troubleshooting

1. Warpage و bowing

المشكلة: stackup غير متماثل او حذف copper pours.

الحل: حافظ على التماثل وعلى توازن كثافة النحاس.

2. انحراف solder mask

المشكلة: mask dams رفيعة جدا على لوحة قياسية.

الحل: استخدم gang relief او زد spacing بين pads عند الامكان.

3. ضعف plating داخل vias

المشكلة: vias صغيرة على لوحة سميكة ترفع aspect ratio.

الحل: اجعلها اقل من 8:1 في العملية القياسية.

راجع ايضا DFM Guidelines.

6 قواعد اساسية لتقليل التكلفة من دون خسارة yield

| القاعدة / التوجيه | لماذا تهم | القيمة المستهدفة / الاجراء |

|---|---|---|

| وحد laminate | المواد القياسية ارخص واسهل توفرا. | FR4 TG150 |

| ارفع استغلال panel | ضعف الاستغلال يعني دفع ثمن scrap. | >80 % |

| وحد drills | كل تغيير اداة يزيد زمن CNC. | <10 احجام |

| تجنب blind/buried vias | الدورات الاضافية من lamination ترفع التكلفة كثيرا. | Through-hole فقط |

| خفف التفاوتات | التفاوتات الضيقة ترفع كلفة العملية. | +/- 0.10 mm |

| اختر finish بعناية | الذهب مكلف اذا لم تكن الحاجة الى planar pads ضرورية. | HASL او OSP |

FAQ

Q: هل تقليل عدد الطبقات يخفض التكلفة دائما؟

A: لا، اذا كان ذلك يجبرك على استخدام HDI او routing دقيق جدا.

Q: هل OSP ارخص من ENIG؟

A: نعم، لكنه اكثر حساسية في التخزين والمناولة.

Q: كيف تؤثر الكمية؟

A: في Mass Production يتم توزيع setup cost على عدد كبير من الوحدات.

Q: هل الشكل غير المستطيل يوفر المال؟

A: غالبا لا، لانه يضعف كفاءة panelization.

اطلب عرض سعر / مراجعة DFM لتقليل التكلفة من دون التضحية بالـ yield

ارسل:

- Gerber Files: ويفضل RS-274X.

- Drill File: Excellon مع قائمة الادوات.

- Stackup Diagram: ترتيب الطبقات ووزن النحاس.

- Fabrication Drawing: اللون والتشطيب والتفاوتات.

- الكميات: prototype او production.

الخلاصة

تقليل تكلفة PCB من دون التضحية بالـ yield يعني التصميم بذكاء لعمليات قياسية، واستغلالا افضل للمواد، وتقليلا للتعقيد غير الضروري. ومع قواعد واضحة في trace width و drill size و stackup يمكن الوصول الى منتج موثوق بتكلفة تنافسية.