يمثل الاستثمار في Design for Manufacturability (DFM) وDesign for Testability (DFT) قرارًا استراتيجيًا ينقل إدارة الجودة من أسلوب تفاعلي يعتمد على إصلاح العيوب بعد ظهورها إلى أسلوب وقائي يمنع المشكلة قبل أن تبدأ. بالنسبة إلى المشترين ومديري المنتجات، فإن فهم كيفية تقليل عيوب PCBA باستخدام DFM وDFT يعد من أكثر الطرق فاعلية لخفض التكلفة الإجمالية وتسريع الوصول إلى السوق. يشرح هذا الدليل المواصفات الفنية وأطر اتخاذ القرار التي تساعد على مواءمة التصميم الهندسي مع قدرات التصنيع الفعلية.

أهم النقاط

- الوقاية الاستباقية: يكشف DFM مبكرًا مشكلات layout التي تتسبب في جسور اللحام وtombstoning والفراغات قبل بدء الإنتاج.

- تغطية الاختبار: يضمن DFT أن أي عيب قد يظهر سيكون قابلاً للاكتشاف عبر ICT أو الاختبار الوظيفي بدلًا من أن يتسرب إلى الاستخدام الميداني.

- خفض التكلفة: معالجة العيب في مرحلة التصميم أقل كلفة بنحو 10x من معالجته في مرحلة التجميع، وأقل بنحو 100x من معالجته بعد التسليم.

- مواءمة المورد: تعد المتطلبات الواضحة الخاصة بالـ stencil وملفات reflow ضرورية عند التعامل مع مكونات معقدة مثل BGA وQFN.

أهم الخلاصات

قبل الدخول في التفاصيل الفنية، يوضح الجدول التالي كيف يؤثر كل من DFM وDFT مباشرة في التكلفة وموثوقية المنتج.

| Feature | DFM (Design for Manufacturability) | DFT (Design for Testability) |

|---|---|---|

| الهدف الأساسي | ضمان إمكانية تصنيع المنتج بصورة مستقرة وبمعدل مردود مرتفع. | ضمان إمكانية التحقق من المنتج بسرعة ودقة. |

| التركيز على العيوب | يمنع حدوث العيوب من الأصل، مثل جسور اللحام. | يكشف العيوب التي تحدث رغم ذلك، مثل الدوائر المفتوحة. |

| المخرج الرئيسي | أشكال pad محسنة، وthermal relief، وتباعد مناسب بين المكونات. | Test point، وإتاحة JTAG، وscan chain. |

| محرك العائد | ارتفاع First Pass Yield (FPY) وتقليل إعادة العمل. | انخفاض أعطال الميدان وتسريع التشخيص. |

كيفية تقليل عيوب PCBA باستخدام DFM وDFT: النطاق وسياق القرار ومعايير النجاح

لا يبدأ خفض العيوب من خط التجميع، بل من مرحلة المخطط وlayout. وعندما يسأل المشتري عن كيفية تقليل عيوب PCBA باستخدام DFM وDFT، فعليه أن يفهم أنه لا يشتري لوحة عادية فقط، بل يشتري قدرة عملية قابلة للتكرار ويمكن الوثوق بها.

سياق القرار

يجد المشترون أنفسهم غالبًا أمام موازنة بين زيادة الجهد الهندسي في البداية وبين تسريع التنفيذ لاحقًا في الإنتاج. فتجاوز مراجعات DFM من أجل تسريع النموذج الأولي ينتهي كثيرًا إلى لوحات يصعب تجميعها أو إلى معدلات خردة مرتفعة عند الإنتاج الكمي. ويعتمد مستوى التحليل المطلوب على درجة تعقيد PCBA. فقد تحتاج لوحة بسيطة تحتوي على عناصر سلبية كبيرة إلى حد أدنى من DFM، بينما تحتاج لوحة HDI تحتوي على BGA إلى تحليل صارم ومفصل.

معايير النجاح

للتأكد من أن جهود DFM وDFT تحقق النتيجة المطلوبة، يجدر تتبع المؤشرات التالية:

- First Pass Yield (FPY): نسبة اللوحات التي تجتاز جميع الاختبارات من دون إعادة عمل. ويعد مستوى 98%+ هدفًا شائعًا للمنتجات الناضجة.

- تغطية الاختبار: نسبة الـ net والمكونات التي يمكن الوصول إليها عبر الاختبار الآلي. ويستهدف DFT القوي عادة 90%+.

- معدل الرفض الكاذب: عدد المرات التي تُرفض فيها لوحات سليمة بسبب حدود اختبار غير مناسبة أو fixture غير مستقر.

- Engineering Change Orders (ECOs): يشير انخفاض ECOs المرتبطة بالتجميع إلى أن DFM يعمل بشكل صحيح.

المواصفات التي ينبغي تحديدها مسبقًا

| Parameter | Recommended value / option | Why it matters | How to verify |

|---|---|---|---|

| Layer count | 4–8 عادة، وأكثر عند الحاجة | يؤثر في التكلفة والمردود وهامش التوجيه | Stackup + تقرير DFM |

| Min trace/space | 4/4 mil عادة | يؤثر في المردود ومدة التنفيذ | DRC + القدرة التصنيعية |

| Via strategy | Through vias مقابل VIPPO مقابل microvia | يؤثر في موثوقية التجميع | مقطع مجهري + معايير IPC |

| Surface finish | ENIG/OSP/HASL | يؤثر في قابلية اللحام والاستواء | COC + اختبارات قابلية اللحام |

| Solder mask | أخضر مطفي افتراضيًا | يحسن قراءة AOI ويخفض خطر الجسور | تجربة AOI + تسجيل القناع |

| Test | Flying probe / ICT / FCT | موازنة بين التغطية والتكلفة | Coverage report + خطة fixture |

| Acceptance class | IPC Class 2 / 3 | يحدد حدود العيوب المقبولة | ملاحظات الرسم + تقرير الفحص |

| Lead time | Standard مقابل expedited | يؤثر في مخاطر الجدول الزمني | عرض السعر + تأكيد السعة |

لكي يعمل DFM وDFT بفاعلية، لا بد من إدراج متطلبات محددة بوضوح داخل data package. فأي غموض في البيانات يدفع المصنع إلى افتراضات تشغيلية، وهذه الافتراضات من أكثر أسباب العيوب شيوعًا.

1. متطلبات البيانات الخاصة بـ DFM

قدّم إلى contract manufacturer (CM) أكثر من مجرد ملفات Gerber.

- اختيار فئة IPC: حدّد بوضوح ما إذا كانت اللوحة ستُنفذ وفق IPC-A-610 Class 2 أو Class 3. فذلك يحدد معايير حجم اللحام والمحاذاة.

- Footprint المكونات: اطلب التحقق من footprint مقابل Bill of Materials (BOM). ويعد عدم التطابق بين المكون الفعلي وland pattern من أشهر أسباب فشل DFM.

- استراتيجية panelization: حدّد تكوين panel. إذ يمكن أن تؤدي panelization غير الجيدة إلى شقوق إجهاد في المكثفات الخزفية أثناء depaneling.

- جسور solder mask: حدّد حدًا أدنى لعرض solder mask بين pad، وغالبًا يكون 4 mil، لمنع جسور اللحام على الدوائر ذات الخطوة الدقيقة.

2. متطلبات البيانات الخاصة بـ DFT

غالبًا ما يُؤجل DFT إلى مرحلة متأخرة، ما يؤدي إلى fixture من نوع bed of nails مرتفع الكلفة ولا يصل أصلًا إلى الـ net الحرجة.

- إتاحة test point: اشترط وجود test point لكل net حرجة على الجانب السفلي من PCB. فهذا يسمح بإجراء In-Circuit Test (ICT) من جهة واحدة، وهو أقل كلفة بكثير.

- Clearance حول test point: حدّد مسافة أمان دنيا، مثل 50 mil، بين test point والمكونات العالية حتى لا تتضرر المجسات.

- JTAG/Boundary Scan: في اللوحات الرقمية المعقدة، تأكد من أن سلسلة JTAG موزعة وقابلة للوصول. وهذا يتيح اختبار التوصيلات بين الشرائح من دون الحاجة إلى مجسات فعلية في كل نقطة.

- Netlist: احرص دائمًا على تزويد المصنع بملف netlist بصيغة IPC-356. فهذا الملف يسمح بمقارنة التوصيلية المستخرجة من Gerber مع التوصيلية في المخطط.

موارد ذات صلة

المخاطر الرئيسية: الأسباب الجذرية والكشف المبكر والوقاية

يساعد فهم أنواع العيوب المحددة على إعطاء الأولوية الصحيحة لمراجعات DFM. وتظهر أصعب الحالات غالبًا أسفل المكونات ذات الأطراف السفلية مثل QFN (Quad Flat No-lead) وBGA.

1. الفراغات في مكونات QFN وBGA

الفراغات هي جيوب هواء محبوسة داخل وصلة اللحام. وعندما تزيد هذه الفراغات عن الحد المناسب، فإنها تضعف التوصيل الحراري والمتانة الميكانيكية.

- الخطر: ارتفاع حرارة QFN القدرة بسبب سوء نقل الحرارة عبر وصلة لحام مليئة بالفراغات.

- الوقاية (DFM): طبّق qfn reflow best practices to reduce voids. ويعني ذلك تقسيم فتحة معجون اللحام فوق thermal pad إلى نوافذ متعددة. فبدلًا من طباعة كتلة كبيرة من المعجون تحتجز الغازات، تُطبع شبكة من مربعات صغيرة بتغطية تقارب 50-70% لتوفير مسارات لخروج المواد المتطايرة أثناء reflow.

2. عيوب لحام BGA: الجسور والانقطاعات

تُعد مكونات BGA صعبة لأن وصلاتها مخفية.

- الخطر: عيب Head-in-Pillow (HiP)، حيث تستقر كرة اللحام فوق المعجون من دون أن تندمج اندماجًا صحيحًا.

- الوقاية (DFM/العملية): يلزم ضبط صارم وفق bga voiding control: stencil, reflow, and x-ray criteria.

- Stencil: استخدم stencil مصقولًا كهربائيًا مع apertures شبه منحرفة لتحسين انفصال المعجون.

- Reflow: اضبط منطقة soak بعناية. فإذا احترق flux مبكرًا، أعاقت الأكسدة حدوث البلل الصحيح.

- معايير الأشعة السينية: حدّد حدود pass/fail بوضوح. وفي IPC Class 2 يجب أن تبقى الفراغات عادة أقل من 25% من مساحة الكرة.

3. Tombstoning

يحدث هذا العيب عندما يرتفع مكون سلبي صغير من أحد الطرفين أثناء reflow.

- السبب الجذري: عدم توازن قوى البلل، وغالبًا لأن أحد pad متصل بمستوى أرضي كبير يعمل كمشتت حراري، بينما pad الآخر متصل بمسار رفيع فقط.

- الوقاية (DFM): استخدم thermal relief على pad الأرضي حتى يصل padان إلى درجة حرارة reflow في الوقت نفسه.

4. Shadowing

في wave soldering أو selective soldering قد تحجب المكونات الكبيرة وصول سبيكة اللحام إلى المكونات الأصغر الواقعة خلفها.

- الوقاية (DFM): ضع قواعد تباعد واضحة مرتبطة باتجاه مرور اللوحة داخل آلة اللحام.

التحقق والقبول: الاختبارات ومعايير الاجتياز

| Test / Check | Method | Pass criteria (example) | Evidence |

|---|---|---|---|

| الاستمرارية الكهربائية | Flying probe / fixture | اختبار 100% من الـ net من دون opens أو shorts | تقرير E-test |

| الأبعاد الحرجة | قياس | مطابق لتفاوتات الرسم | سجل الفحص |

| سلامة الطلاء / التعبئة | مقطع مجهري | لا توجد فراغات أو شقوق تتجاوز حدود IPC | صور المقطع المجهري |

| قابلية اللحام | اختبار البلل | بلل مقبول ومن دون dewetting | تقرير قابلية اللحام |

| Warpage | قياس الاستواء | ضمن المواصفة، مثل ≤0.75% | سجل warpage |

| التحقق الوظيفي | FCT | جميع الحالات ناجحة مع حفظ السجل | سجلات FCT |

كيف نثبت أن DFM وDFT نجحا؟ لا بد من إعداد خطة تحقق مرتبطة بأهداف NPI assembly.

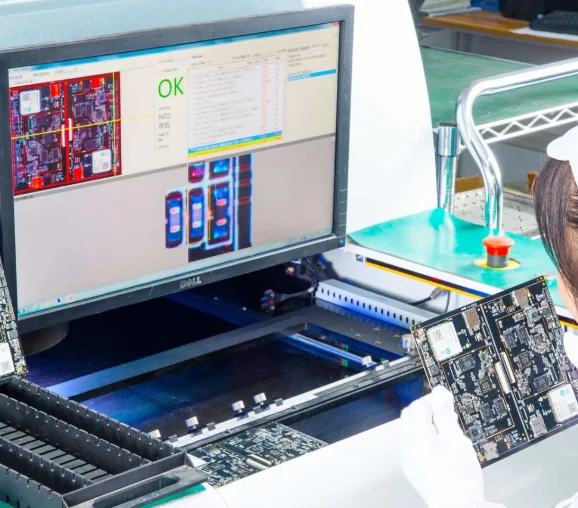

Automated Optical Inspection (AOI)

يعد AOI خط الدفاع الأول. فالكاميرات تتحقق من وجود المكونات والقطبية والانحراف وجودة اللحام.

- معايير الاجتياز: لا توجد قطع مفقودة، وعلامات القطبية مصطفة، وأشكال اللحام مطابقة لمعايير IPC.

- الحدود: لا يستطيع AOI رؤية ما تحت BGA أو QFN.

X-Ray Inspection (Axi)

يعد الفحص بالأشعة السينية ضروريًا للتحقق من BGA وQFN.

- معايير الاجتياز: يجب الالتزام بمتطلبات bga voiding control: stencil, reflow, and x-ray criteria. فراغات أقل من 25%، وشكل كرة متسق، ومن دون جسور.

- التطبيق: فحص 100% في النماذج الأولية، وفحص بالعينات في الإنتاج الكمي.

- للمزيد: فحص الأشعة السينية

In-Circuit Test (ICT) وFlying Probe

هنا تظهر القيمة الحقيقية لـ DFT.

- ICT: يستخدم fixture من نوع bed of nails لاختبار جميع الـ net في الوقت نفسه. وهو سريع، لكنه مكلف من حيث العدة. لذلك يجب تعريف test point منذ مرحلة DFT.

- Flying Probe: تستخدم أذرعًا روبوتية لاختبار النقاط من دون fixture. وهي أبطأ، لكنها مثالية للنماذج الأولية.

- معايير الاجتياز: جميع القيم السلبية ضمن التفاوت المسموح، ولا توجد shorts أو opens على الـ net الفعالة.

Functional Circuit Test (FCT)

هذه هي مرحلة التحقق النهائية. تُغذى اللوحة بالطاقة ويجب أن تؤدي وظيفتها الفعلية.

- معايير الاجتياز: يقلع الجهاز، ويُحمَّل firmware، وتستجيب منافذ I/O كما ينبغي.

قائمة تحقق لتأهيل المورد: RFQ والتدقيق وإمكانية التتبع

عند اختيار شريك يساعدك على تقليل عيوب PCBA باستخدام DFM وDFT، استخدم قائمة التحقق التالية.

1. القدرات الهندسية

- هل يجري المورد مراجعة DFM إلزامية قبل tooling؟

- هل يقدم DFM report تفصيليًا وليس مجرد pass/fail، مع إبراز مخاطر مثل acid trap وsliver؟

- هل يستطيع اقتراح footprint بديل لتحسين المردود؟

- راجع إرشادات DFM لمعرفة مستوى التوقعات.

2. ضبط العملية

- هل توجد SPI inline؟ فـ SPI تمنع نسبة كبيرة من عيوب المعجون واللحام.

- هل يتوفر فحص الأشعة السينية داخل المصنع نفسه؟

- هل يستطيع المورد تطبيق qfn reflow best practices to reduce voids مثل vacuum reflow أو تحسين profile؟

3. التتبع ونظام الجودة

- هل الموقع حاصل على ISO 9001 أو IATF 16949؟

- هل يوفّر تتبعًا على مستوى المكونات يربط دفعات محددة بأرقام تسلسلية محددة؟

- راجع نظام الجودة.

كيفية اختيار المستوى المناسب من DFM وDFT: المقايضات وقواعد القرار

ليست كل لوحة بحاجة إلى المستوى نفسه من DFM وDFT. وتساعد القواعد التالية على تحقيق توازن عملي بين التكلفة والمخاطر.

السيناريو A: إلكترونيات استهلاكية بسيطة منخفضة التكلفة وعالية الحجم

- الاستراتيجية: التركيز على DFM لرفع المردود وتقليل زمن الدورة.

- DFT: حد أدنى. والاعتماد على AOI وأخذ عينات وظيفية.

- المقايضة: قبول معدل أعطال ميداني أعلى قليلًا مقابل الحفاظ على انخفاض تكلفة الوحدة.

السيناريو B: منتجات طبية أو سيارات ذات موثوقية عالية وحجم متوسط

- الاستراتيجية: تطبيق قوي لكل من DFM وDFT.

- DFT: 100% ICT و100% اختبار وظيفي.

- المقايضة: ترتفع تكاليف NRE الخاصة بالـ fixture وبرمجة الاختبار، لكن معدلات العطل الميداني تقترب من الصفر.

- النقطة الخاصة: الالتزام الصارم بـ bga voiding control: stencil, reflow, and x-ray criteria.

السيناريو C: النمذجة الأولية السريعة

- الاستراتيجية: DFM "خفيف". لا يُعالَج إلا ما يمنع التجميع فعليًا.

- DFT: flying probe من دون تكلفة fixture.

- المقايضة: يزداد زمن اختبار كل وحدة، لكن التسليم الكلي يصبح أسرع.

الأسئلة الشائعة: التكلفة ومدة التنفيذ وملفات DFM والمواد والاختبارات

1. هل تزيد متطلبات DFM/DFT من سعر العرض؟ نعم في البداية. فزمن الهندسة وfixture الاختبار ضمن NRE يرفعان التكلفة الأولية. لكن التكلفة الإجمالية للمشروع تنخفض كثيرًا في حالات عديدة بسبب تحسن المردود وتراجع إعادة العمل.

2. كم تضيف مراجعة DFM إلى مدة التنفيذ؟ عادة من 1 إلى 2 يوم. فمراجعة DFM الجيدة تتم قبل طلب المواد. وهذا التأخير البسيط يوفر أسابيع قد تضيع لاحقًا عند اكتشاف أن اللوحة غير قابلة للتصنيع السلس.

3. هل يستطيع DFM إصلاح تصميم دائرة سيئ؟ لا. فـ DFM يضمن أن اللوحة قابلة للتصنيع والتجميع، لكنه لا يضمن أن الدائرة ستعمل كما ينبغي. فإذا كان المخطط يحتوي على أخطاء منطقية، فستُصنع اللوحة جيدًا لكنها ستفشل وظيفيًا.

4. ما الفرق بين DFM وDFA؟ يشير DFM عادة إلى قابلية تصنيع PCB نفسها، مثل الحفر والنقش. أما DFA فيتعلق بتجميع المكونات، مثل اللحام والخلوصات. وفي الممارسة اليومية يُستخدم DFM كثيرًا كمصطلح شامل للجانبين.

5. هل أحتاج إلى ICT إذا كان لدي اختبار وظيفي؟ في الوضع المثالي نعم. فـ ICT يحدد أي مكون أو أي net فيه المشكلة. أما الاختبار الوظيفي فعادة لا يخبرك إلا بأن اللوحة لا تعمل. ومن ناحية التشخيص والإصلاح، يكون ICT أكثر كفاءة بكثير.

6. كيف تؤثر المواد في DFM؟ يؤثر اختيار المادة، مثل High Tg FR4، في كيفية تمدد اللوحة أثناء reflow. ويعد عدم توافق CTE بين المكون واللوحة سببًا مهمًا في إجهاد وصلات اللحام.

7. ما أفضل طريقة لنقل ملاحظات DFM؟ أدرج ملف Read Me أو PDF داخل أرشيف Gerber. واكتب المتطلبات الخاصة بوضوح، مثل "Do not X-out arrays" أو "Mask plug vias at U1".

طلب عرض سعر أو مراجعة DFM: ما الذي يجب إرساله

إذا كنت تريد تحسين PCBA للإنتاج الكمي، فأرسل data package لإجراء مراجعة DFM شاملة.

قائمة التحقق لطلب عرض السعر:

- ملفات Gerber (RS-274X): طبقات النحاس، وsolder mask، والطباعة الحريرية، وبيانات الحفر، وطبقات المعجون.

- Bill of Materials (BOM): ملف Excel يضم Manufacturer Part Numbers (MPN) وreference designator.

- Centroid file (Pick and Place): إحداثيات X-Y وبيانات الدوران.

- Assembly drawings: ملف PDF يوضح مواقع المكونات وعلامات القطبية.

- متطلبات الاختبار: وصف للتغطية المطلوبة، مثل ICT أو FCT أو burn-in.

مسرد المصطلحات الرئيسية

| Term | Meaning | Why it matters in practice |

|---|---|---|

| DFM | Design for Manufacturability: قواعد layout لتقليل العيوب. | يقلل إعادة العمل والتأخير والتكلفة الخفية. |

| AOI | Automated Optical Inspection لاكتشاف عيوب اللحام والتجميع. | يرفع التغطية ويكشف الانحرافات المبكرة. |

| ICT | In-Circuit Test لفحص opens وshorts والقيم الكهربائية. | اختبار بنيوي سريع للإنتاج الكمي. |

| FCT | Functional Circuit Test مع تشغيل اللوحة والتحقق من سلوكها. | يثبت الوظيفة الحقيقية تحت الحمل. |

| Flying Probe | اختبار كهربائي من دون fixture باستخدام مجسات متحركة. | مناسب للنماذج الأولية والأحجام المنخفضة أو المتوسطة. |

| Netlist | تعريف التوصيلية للمقارنة بين design وPCB المصنّع. | يساعد على كشف opens وshorts قبل التجميع. |

| Stackup | تكوين الطبقات باستخدام core وprepreg والنحاس والسماكات. | يؤثر في impedance وwarpage والموثوقية. |

| Impedance | سلوك متحكم فيه للمسارات في إشارات RF أو high-speed مثل 50Ω. | يحد من الانعكاسات ومشكلات سلامة الإشارة. |

| ENIG | تشطيب سطحي من Electroless Nickel Immersion Gold. | يوازن بين قابلية اللحام والاستواء مع ضرورة مراقبة سماكة النيكل. |

| OSP | تشطيب Organic Solderability Preservative. | منخفض الكلفة لكنه أكثر حساسية للمناولة وتكرار reflow. |

الخلاصة: الخطوات التالية

إن فهم كيفية تقليل عيوب PCBA باستخدام DFM وDFT هو استثمار مباشر في عمر المنتج وسمعة العلامة التجارية. فعندما تُحدد بوضوح مواصفات الـ stencil وملفات reflow وإتاحة الاختبار، يتحول التصنيع من عملية غامضة إلى عملية قابلة للضبط ويمكن التنبؤ بها.

أشرك شريك التصنيع في وقت مبكر من مرحلة التصميم. فالمراجعة المشتركة لـ qfn reflow best practices to reduce voids وbga voiding control: stencil, reflow, and x-ray criteria توفر وقتًا ورأس مال ملموسين. أعطِ أولوية لشفافية data package، وتحقق من النتائج باختبارات صارمة، واختر موردًا يرى الجودة مسؤولية مشتركة.