تجمع اللوحات الرئيسية في Smart TV بين المعالجة التطبيقية، وعمليات scaling و video processing، وعدة واجهات عالية السرعة مثل HDMI و USB و Ethernet، واتصال لاسلكي، وانظمة صوت، وكل ذلك على لوحات يجب ان تحقق اهداف تكلفة شديدة الصرامة مع الحفاظ على تجربة مشاهدة ممتازة. وتمتد تحديات تصميم PCB من واجهات HDMI 2.1 فائقة السرعة ذات 48 Gbps مجمعة وصولا الى واجهات قيادة اللوحات الكبيرة ودمج منظومة الطاقة.

يركز هذا الدليل على الجوانب الخاصة بالـ PCB في تصميم Smart TV: كيفية تقسيم الوظائف بين main board و T-CON، ومتطلبات توجيه video SoC، وسلامة اشارة HDMI 2.1، وتصميم واجهة اللوحة، وبنية التغذية الكهربائية، والتوازن الحاسم بين الجودة وتحسين التكلفة في التصنيع بالنسبة الى منتجات التلفزيون.

Design Checklist (Fast Pass)

- حدد التقسيم مبكرا: احسم مبكرا توزيع الوظائف بين main board و T-CON و PSU board، ثم ثبت نوع الربط واختيار الموصل.

- ضع HDMI قريبا: اجعل مسارات HDMI 2.1 FRL قصيرة، وخطط منذ البداية لمواضع ESD و CMC و retimer.

- تعامل مع DDR كنظام كامل: يجب تصميم stackup والامبيدانس وتطابق الاطوال ومستويات المرجع ومسارات العودة كوحدة واحدة.

- صمم PDN والحرارة معا: توزيع النحاس ومصفوفات via ونقل الحرارة الى الشاسيه جزء من power design نفسه.

- استخدم DFM لضبط التكلفة: تجنب HDI عندما لا يكون ضروريا، وحسن استغلال لوحة التصنيع والوصول الى نقاط الاختبار.

In This Guide

- بنية لوحات التلفاز: تقسيم main board و T-CON

- متطلبات توجيه video processing SoC

- تنفيذ واجهة HDMI 2.1 عالية السرعة

- تصميم واجهة توقيت اللوحة

- تكامل الطاقة والاعتبارات الحرارية

- التصنيع المحسن من حيث التكلفة لمنتجات التلفزيون

TV Board Architecture: Main Board and T-CON Partitioning

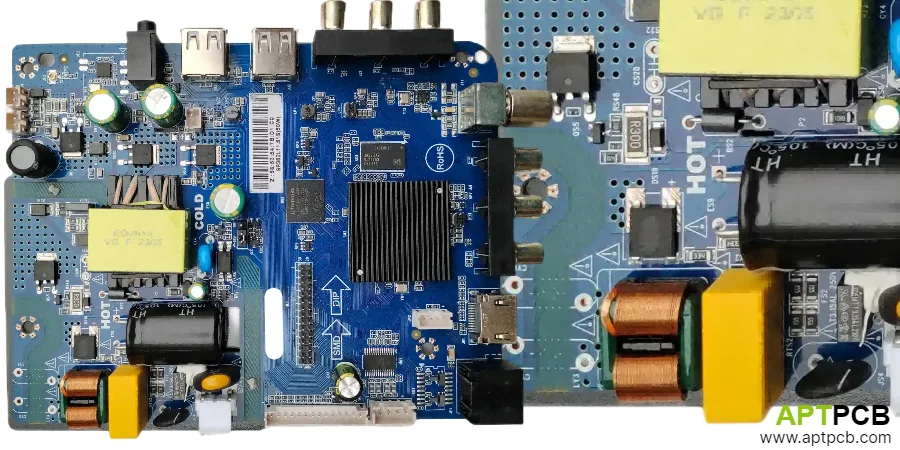

غالبا ما تتوزع الكترونيات Smart TV على عدة لوحات PCB: تتولى main board المعالجة التطبيقية والاتصال وادخال الفيديو ومعالجته، بينما تدير لوحة T-CON، اي timing controller، قيادة اللوحة وتحسين الصورة، وتتولى لوحة التغذية توفير عدة خطوط جهد. ويعكس هذا التقسيم متطلبات وظيفية واعتبارات سلسلة توريد في الوقت نفسه، لان اللوحات المختلفة قد تستخدم تصاميم T-CON مختلفة، بينما يمكن توحيد اللوحات الرئيسية عبر عدة سلاسل منتجات.

تنقل الواجهة بين main board و T-CON بيانات فيديو تمت معالجتها بالكامل حتى دقات تصل الى 8K. وهذا يفرض اما واجهات متوازية ذات عرض نطاق بالغ الارتفاع، حيث يحتاج LVDS الى عشرات الازواج، او بروتوكولات serialized مثل V-by-One و eDP تقلل عدد الموصلات لكنها تتطلب سلامة اشارة على مستوى multi-gigabit. وهذه الواجهة بين اللوحات هي التي تحدد في كثير من الاحيان السقف العملي لاداء الفيديو في النظام.

Board Partitioning Considerations

- نطاق main board: يشمل SoC والذاكرة ومستقبلات HDMI وواجهات USB و Ethernet ووحدات WiFi و Bluetooth ومعالجة الصوت وروابط الاتصال مع T-CON ولوحات الطاقة.

- مستوى دمج T-CON: بعض اللوحات تدمج T-CON داخل اللوحة نفسها، بينما تستخدم لوحات اخرى بطاقة T-CON منفصلة، وهذا يغير مباشرة متطلبات الواجهة على main board.

- اختيار الواجهة: تحدده مواصفات اللوحة. كثير من تصاميم 4K60 تستخدم V-by-One HS مع نحو 8 lanes ضمن فئة تقارب 3 الى 4 Gbps لكل lane، بينما تحتاج 8K عادة الى عدد اكبر من lanes او معدلات اعلى او واجهة مختلفة.

- انواع الموصلات: تعتمد الواجهات عالية السرعة على موصلات متخصصة تحافظ على مطابقة الامبيدانس، بينما تحد الكابلات الشريطية من عرض النطاق وتتطلب تصميما دقيقا.

- توزيع الطاقة: قد تقوم main board بتغذية T-CON، ما يرفع متطلبات حمل التيار على اللوحة الرئيسية، او يمكن ان تتلقى T-CON التغذية مباشرة من لوحة الطاقة.

- الترتيب الميكانيكي: تركب main board عادة في الجزء السفلي الخلفي من الشاشة، وتفرض الشروط الحرارية مسافة مناسبة عن اللوحة ومسارات تهوية كافية.

ان فهم هذه البنية على مستوى النظام يوجه قرارات partitioning الخاصة بالـ PCB، وهو ما ينعكس مباشرة على الاداء الكهربائي وكفاءة التصنيع.

Video Processing SoC Routing Requirements

تدمج شرائح SoC الخاصة بـ Smart TV قدرا كبيرا من التعقيد: معالجات تطبيقية quad-core او octa-core، ووحدات فك ترميز فيديو مخصصة تدعم عدة codecs بدقات 4K و 8K، ومحركات عرض تقوم بعمليات scaling وتحسين الصورة، بالاضافة الى عدد كبير من الواجهات. وتاتي هذه الشرائح المتكاملة في حزم BGA كبيرة غالبا ما تضم 500 الى اكثر من 1000 pin، مع pitch دقيق بين 0.4 و 0.65 mm. ولهذا يجب ان يحقق التوجيه التوازن بين الاداء وقابلية التصنيع.

وتبرز تحديات خاصة جدا في واجهات الذاكرة. فـ DDR4 و LPDDR4/5 تعمل بسرعات تتطلب ضبطا دقيقا للاطوال وتحكما صارما في الامبيدانس. وعلى عكس الهواتف الذكية التي تستخدم احيانا package-on-package، تعتمد تلفزيونات Smart TV عادة على ذاكرة منفصلة، ما ينقل كامل تحديات سلامة الاشارة الى مستوى اللوحة نفسها.

SoC Routing Guidelines

- استراتيجية BGA fanout: تحتاج حزم BGA ذات الخطوة الدقيقة الى via-in-pad او fanout من نوع dog-bone، بينما تحد vias النافذة من قنوات التوجيه، لذا قد تكون blind vias مناسبة للحزم عالية الكثافة.

- توجيه الذاكرة: يتطلب DDR4 عند 2666-3200 MT/s مطابقة اطوال داخل كل byte lane ضمن ±5 mm، ومطابقة DQS الى DQ ضمن ±10 mm، مع امبيدانس ثابتة.

- متطلبات مستويات المرجع: تحتاج اشارات الذاكرة والواجهات السريعة الى reference planes مستمرة، ويجب تجنب تمرير مسارات الطاقة او وضع vias في مناطق المستوى تحت الاشارات الحرجة.

- استراتيجية decoupling: تحتاج ارجل تغذية الـ SoC الى decoupling محلي، مثل 100 nF لكل مجموعة ارجل، مع سعات bulk بحدود 10-100 uF قريبا. ويجب وضع المكثفات بالقرب من الارجل بقدر ما يسمح به التوجيه.

- الوصول الى JTAG و debug: يجب ان تبقى واجهات debug مثل JTAG و UART متاحة للتطوير والاختبار الانتاجي، ولذلك يجب تحديد مواضع test points او headers بعناية.

- التصميم الحراري: ان قدرة تبديد SoC، التي تكون عادة بين 5 و 15 W، تتطلب فيا حرارية اسفل الحزمة وانتشارا كافيا للنحاس نحو نقاط تماس المشتت او الشاسيه.

يستفيد توجيه video SoC من اساليب high-speed PCB design لضمان وجود هوامش مناسبة في واجهات الذاكرة والعرض.

HDMI 2.1 High-Speed Interface Implementation

تعد HDMI 2.1 من اكثر واجهات المستهلك تطلبا. فهي توفر 12 Gbps لكل lane عبر اربع lanes بيانات، اي 48 Gbps مجمعة، بما يدعم 8K عند 60 Hz او 4K عند 120 Hz مع HDR. ويجب ان يحافظ التوجيه بين HDMI receiver IC والموصل على سلامة الاشارة عند ترددات تصبح فيها اطوال الموجات قريبة من اطوال المسارات، ما يجعل قواعد transmission line ضرورية وليست اختيارية.

كانت HDMI 1.4 و 2.0، حتى 18 Gbps مجمعة، تعتمد على اشارة تفاضلية مع source termination وتسامح امبيدانس اقل تشددا. اما HDMI 2.1 FRL، Fixed Rate Link، فترفع المتطلبات بوضوح: 100 ohm differential impedance (±10%)، ومطابقة محكمة للاطوال داخل كل زوج تفاضلي، وتحكما في insertion loss و return loss على امتداد القناة كلها، اي الموصل والـ PCB والكابل.

HDMI 2.1 Routing Requirements

- التحكم في الامبيدانس: 100 ohm تفاضلية ±10%، وتساعد الازواج التفاضلية المقترنة بقوة على خفض EMI والحفاظ على common-mode rejection.

- فقد القناة: عند 12 Gbps لكل lane يتلاشى هامش الفقد بسرعة. لذلك يجب ان تبقى المسارات قصيرة، وان لم يكن ذلك ممكنا فينبغي النظر في low-loss laminates و/او redriver او retimer.

- قيود الطول: يجب ابقاء مسارات HDMI قصيرة قدر الامكان، فالبقاء دون 50 mm يقلل الفقد وتراكم skew، ولهذا من المهم وضع الموصل قريبا من receiver IC.

- اختيار الطبقة: يفضل توجيه HDMI على طبقات مجاورة لـ ground planes صلبة؛ ويمكن استخدام microstrip على الطبقات الخارجية اذا كانت EMI مضبوطة، بينما تمنح stripline حماية افضل.

- الانتقال عبر via: يجب تجنبه ما امكن. وعندما يصبح ضروريا، ينبغي تقليل stubs، مثلا عبر backdrill عندما يكون ذلك منطقيا، والحفاظ على استمرارية planes المرجعية.

- حماية ESD: تحتاج منافذ HDMI الى حماية ESD. ويؤثر موضع عنصر الحماية مباشرة في سلامة الاشارة، لذا يجب استخدام TVS منخفضة السعة دون 0.3 pF ووضعها عند الموصل.

وقد يتطلب تنفيذ HDMI 2.1 اجراء محاكاة signal integrity للتحقق من ان التوجيه يحقق هامش المطابقة المطلوب، خصوصا عند استخدام مسارات اطول او FR-4 قياسي.

Panel Timing Interface Design

تنقل الواجهة بين main board، او T-CON، وبين لوحة LCD او OLED بيانات الفيديو بمعدلات يحددها pixel clock وعمق اللون. فلوحة 4K عند 60 Hz وعمق 10 bit تحتاج تقريبا الى 17 Gbps من بيانات الفيديو، يتم نقلها عبر LVDS او V-by-One او واجهات proprietary بحسب صانع اللوحة والدقة.

يهيمن V-by-One HS على تطبيقات 4K TV الحالية. فهو يستخدم عددا اقل من lanes مقارنة بـ LVDS، عادة 8 ازواج بدلا من 16 الى 32 زوجا، ولكن بسرعات اعلى، غالبا بين 3.6 و 4.0 Gbps لكل lane. ويسهل العدد الاقل من lanes عملية التوجيه، لكنه يرفع في المقابل متطلبات سلامة الاشارة لكل lane. كما ان وصلات flex الى اللوحة تضيف discontinuities في الامبيدانس يجب ضبطها عبر اختيار الموصل وتصميم termination المناسب على الـ PCB.

Panel Interface Implementation

- اختيار البروتوكول: تحدد مواصفات اللوحة نوع الواجهة. ويعد V-by-One HS شائعا في معظم لوحات 4K، بينما يبقى LVDS مستخدما في الدقات الاقل، وتلجأ بعض لوحات 8K الى واجهات عالية السرعة مملوكة.

- تهيئة lanes: يستخدم V-by-One HS عادة 8 lanes من اجل 4K 60 Hz عند 10 bit، ويزداد العدد مع الدقة ومعدل التحديث وعمق اللون.

- واجهة الموصل: يجب ان تحافظ موصلات اللوحة على مطابقة الامبيدانس، بينما يضيف flex بين اللوحة والدائرة المطبوعة فقدا و skew يحدان من اقصى bit rate يمكن الوصول اليه.

- ساعة المرجع: تحتاج واجهات اللوحة الى reference clock مستقرة، ويؤثر اختيار crystal او oscillator وترشيح التغذية وعزل التوجيه مباشرة في jitter.

- تصميم termination: تعد on-chip termination هي المعتادة في V-by-One receivers، لكن يجب ايضا التحقق من متطلبات termination في مدخل اللوحة ومطابقة output impedance في المصدر.

- اعتبارات EMI: يمكن لاشارات اللوحة ان تشع من كابلات flex، لذلك يساعد grounding الجيد للموصل وتدريع الكابل وابعاد التوجيه عن الدوائر الحساسة على تقليل EMI.

ويتطلب تصميم واجهة اللوحة تنسيقا وثيقا مع مورد اللوحة للتحقق من timing ومستويات الجهد وتوافق الموصلات.

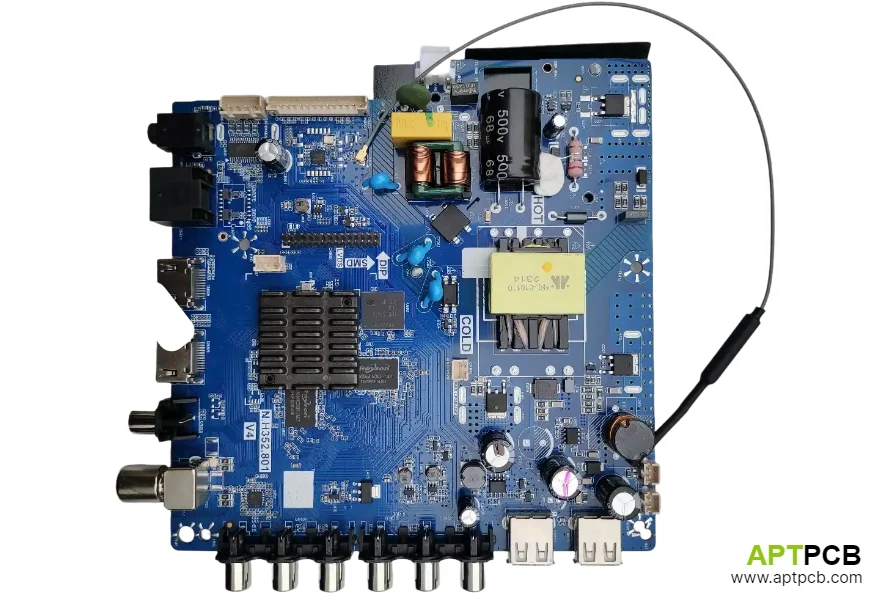

Power Supply Integration and Thermal Considerations

تتلقى اللوحات الرئيسية في Smart TV عادة 5 V او 12 V من لوحة الطاقة، ثم تولد محليا الجهود المطلوبة للـ SoC، مثل 0.9 الى 1.1 V للنواة مع جهود I/O، وللذاكرة، قرابة 1.2 V مع DDR4 او LPDDR4، وللدوائر الاخرى. ويجب على power delivery network ان يتحمل تيارات SoC العابرة مع الحفاظ على تنظيم الجهد ضمن حدود ضيقة، عادة ±3 % على خطوط النواة.

وتختلف الادارة الحرارية في لوحة TV الرئيسية عن نظيرتها في الاجهزة المحمولة. فالمساحة الاكبر تساعد على نشر الحرارة، لكن الشاسيه المغلق والرغبة في التشغيل من دون مروحة يحدان من اساليب التبريد. ولهذا يؤدي الـ PCB دور قاعدة ميكانيكية و heat spreader اساسي في الوقت نفسه، بينما تنتقل الحرارة الى الشاسيه المعدني عبر thermal interface materials.

Power and Thermal Design

- كفاءة DC-DC: تحقق buck converters متعددة الاطوار الخاصة بالـ SoC كفاءة تتجاوز 90 %، ويؤثر اختيار المحاثات و MOSFET في الكفاءة والاداء الحراري معا.

- تسلسل الجهد: يحتاج SoC الى تسلسل تشغيل محدد، عادة core ثم I/O ثم الذاكرة. ويضمن sequencing controller او PMIC مدمج التوقيت الصحيح.

- شبكة decoupling: يحتاج PDN الخاص بالـ SoC الى سعات bulk مثل MLCC او البوليمر او الالكتروليت، الى جانب مكثفات سيراميكية للترددات المتوسطة والعالية موزعة على الشبكة.

- تغطية النحاس: من المفيد زيادة copper pour في الطبقات الداخلية تحت SoC ومراحل التحويل، كما ان استخدام 1 oz او 2 oz من النحاس في power layers يحسن حمل التيار ونشر الحرارة معا.

- مصفوفات via الحرارية: تنقل arrays الكثيفة من vias تحت SoC و MOSFET الخاصة بمرحلة القدرة الحرارة الى الطبقات الداخلية والسطح الخلفي، بينما تمنع vias المملوءة سحب اللحام اثناء التجميع.

- واجهة المشتت: تتصل مناطق thermal pad في main board بالشاسيه عبر thermal interface materials، ويضمن صب النحاس المستوي تماس حراريا متسقا، لذا يفضل تجنب نتوءات vias داخل منطقة التماس.

ويتطلب التفاعل بين التغذية والحرارة فهما لكل من مبادئ power electronics واستراتيجيات thermal management الخاصة بالالكترونيات الاستهلاكية.

Cost-Optimized Manufacturing for Television Products

تتعرض منتجات التلفزيون لضغط هائل من ناحية التكلفة. فالسوق يتوقع تلفزيونات 4K كبيرة الحجم عند اسعار تفرض تحسين التكلفة بقوة عبر كامل التصميم. وتساهم تكلفة الـ PCB بشكل ملموس في BOM الكلي، لذلك تصبح قرارات المواد وعدد الطبقات واستغلال لوحة التصنيع قرارات حاسمة. وفي المقابل لا يمكن التضحية بالجودة، لان تكاليف الضمان الناتجة عن الاعطال الميدانية تتجاوز بسرعة اي وفر تحققه عملية التصنيع.

ويحتاج تحقيق التوازن بين التكلفة والجودة الى قرارات منضبطة: استخدام المواد القياسية عندما تسمح الاداء، وتقليل عدد الطبقات من دون المساس بالوظيفة، وتحسين شكل اللوحة لرفع استغلال panel التصنيعي، والتصميم بهدف رفع yield في التصنيع. كما يساعد اشراك شريك التصنيع مبكرا على اكتشاف فرص خفض التكلفة مع الحفاظ على الجودة.

Cost Optimization Strategies

- اختيار المواد: يعد FR-4 القياسي مع Tg بين 140 و 150 C كافيا لمعظم تطبيقات التلفزيون، بينما لا تستخدم المواد عالية السرعة الا عندما تفرضها فعلا HDMI 2.1 او واجهة حرجة اخرى.

- تقليل عدد الطبقات: يناسب البناء ذو 6 طبقات كثيرا من اللوحات الرئيسية للتلفزيون، بينما يمكن تحقيق 4 طبقات في التصاميم الاقل تعقيدا مع تحسين دقيق للتوجيه.

- استغلال panel: تحقق اللوحات المستطيلة ذات الابعاد المعيارية استغلالا افضل للوحة التصنيع، في حين تقلل الاشكال الخاصة هذا الاستغلال وترفع التكلفة لكل لوحة.

- تحسين vias: تقل تكلفة vias النافذة كثيرا عن blind و buried vias، لذا يفضل اعتماد through-hole كلما امكن، مع حصر HDI في المناطق الدقيقة التي لا غنى عنها.

- تشطيب السطح: يبقى HASL اقل الخيارات تكلفة للمكونات through-hole والمكونات ذات الخطوة الكبيرة، بينما يمنح ENIG سطحا مستويا للمكونات fine-pitch لكنه يضيف تكلفة.

- تغطية الاختبار: يساعد design for test مع test points يسهل الوصول اليها على تقليل تكلفة fixtures ورفع قدرة اكتشاف العيوب، كما يناسب flying-probe testing الاحجام المتوسطة.

وتتيح شراكات تصنيع PCB للانتاج الكمي تحسين التكلفة عبر كفاءة العمليات والتسعير الحجمي مع الحفاظ على ضوابط الجودة.

Technical Summary

يجب على تصميم PCB الخاص بـ Smart TV ان يوازن بين متطلبات متقدمة لسلامة الاشارة، مثل HDMI 2.1 والواجهات السريعة المتجهة الى اللوحة، وبين اهداف تكلفة شديدة الصرامة تميز منتجات التلفزيون الاستهلاكية. ويعتمد النجاح هنا على قرارات معمارية دقيقة تشمل تقسيم اللوحات واختيار الواجهات وتحديد المواد، بحيث يتم الوصول الى الاداء المطلوب من دون رفع التكلفة الاجمالية للنظام.

ومن بين القرارات التقنية الاكثر تاثيرا استراتيجية تنفيذ HDMI، وما يرتبط بها من طول المسارات واختيار المواد وادارة EMI، وتوافق واجهة اللوحة من حيث البروتوكول والموصل، وبنية توزيع الطاقة من حيث الكفاءة والاستجابة العابرة، والحل الحراري الذي يصبح فيه الـ PCB نفسه جزءا من منظومة التبريد.

وعند اختيار شريك التصنيع يجب تقييم القدرات التقنية، مثل high-speed routing وجودة التصنيع متعدد الطبقات، بالتوازي مع القدرة التنافسية في التكلفة. فالاحجام المعتادة في سوق التلفزيون تبرر غالبا تحسينات تصنيعية لا يمكن تبريرها في المنتجات منخفضة الحجم. ورغم ضغط التكلفة، تبقى انظمة الجودة القوية ضرورية، لان تكاليف الضمان الناتجة عن عيوب التصنيع تلتهم بسرعة اي وفر في الانتاج.