Ключевые выводы

- Определение: Покрытие заводского внутрисхемного тестирования (ICT) для ПЛК относится к проценту цепей и компонентов на плате программируемого логического контроллера, которые могут быть электрически проверены во время производства.

- Критичность: В отличие от бытовой электроники, ПЛК требуют почти 100% надежности; пропущенные дефекты могут привести к катастрофическим промышленным сбоям.

- Метрики: Стандарт PCOLA/SOQ является отраслевым эталоном для измерения качества покрытия, а не просто процентных пунктов.

- Проектирование для тестирования (DFT): Достижение высокого покрытия начинается на этапе проектирования схемы, а не на заводе.

- Компромиссы: Более высокое покрытие часто требует больших печатных плат или более дорогих приспособлений; балансировка этого является ключом к экономически эффективному производству.

- Валидация: Отчеты о моделировании должны быть подтверждены физическими результатами испытаний во время проверки первого образца (FAI).

- Партнерство: Работа с компетентным производителем, таким как APTPCB (APTPCB PCB Factory), гарантирует, что ваша стратегия DFT соответствует фактическим производственным возможностям.

Покрытие заводского внутрисхемного тестирования (ICT) для ПЛК (область применения и границы)

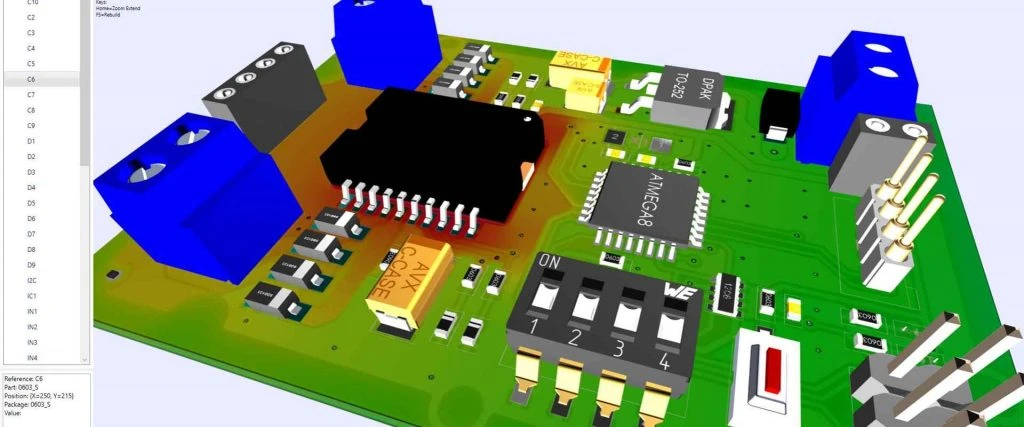

Понимание объема тестирования — это первый шаг к обеспечению промышленной надежности в системах управления. Покрытие внутрисхемного тестирования (ICT) на производстве для ПЛК — это количественная мера того, какая часть логики и связности печатной платы может быть проверена с помощью тестера типа "ложе гвоздей". В контексте программируемых логических контроллеров (ПЛК) этот показатель гораздо более критичен, чем в общей электронике. ПЛК работают в суровых условиях, включающих вибрацию, экстремальные температуры и электромагнитные помехи. Паяное соединение, которое проходит визуальный осмотр, но не выдерживает электрический стресс-тест, может привести к остановке завода через несколько месяцев.

ICT (внутрисхемное тестирование) конкретно нацелено на:

- Короткие замыкания и обрывы: Обеспечение отсутствия непреднамеренных мостов между цепями и непрерывности дорожек.

- Значения компонентов: Проверка соответствия сопротивления, емкости и индуктивности спецификации (BOM).

- Присутствие и ориентация компонентов: Обеспечение правильной установки и ориентации микросхем.

- Функция активных компонентов: Выполнение базовых логических проверок диодов, транзисторов и интегральных схем.

Важно отличать покрытие ICT от покрытия функционального тестирования цепи (FCT). ICT ищет производственные дефекты (паяные мосты, неправильные детали), в то время как FCT проверяет, выполняет ли плата свою предполагаемую логику. Для ПЛК высокое покрытие ICT является основой, которая делает FCT значимым. Если физические соединения не проверены в первую очередь, функциональная отладка становится невозможной. В APTPCB мы подчеркиваем, что покрытие — это не просто процентное число. Это инструмент управления рисками. Плата с 95% покрытием все еще может пропустить одно критически важное реле безопасности, которое защищает всю систему. Поэтому объем должен отдавать приоритет "критическим цепям" над общей статистикой покрытия.

Важные метрики (как оценивать качество)

Измерение покрытия требует больше, чем простого соотношения "прошел/не прошел"; оно требует детального анализа конкретных типов дефектов.

Для истинной оценки покрытия внутрисхемного тестирования (ICT) на заводе для ПЛК, инженеры используют специфические метрики, которые классифицируют, что тестируется и насколько хорошо. Отраслевым стандартом для этого является модель PCOLA/SOQ. Эта модель разделяет атрибуты компонентов (PCOLA) от атрибутов соединений (SOQ).

| Метрика | Почему это важно | Типичный диапазон или влияющие факторы | Как измерять |

|---|---|---|---|

| Коэффициент доступа к тесту | Определяет, могут ли щупы физически достигать цепей. | 90% - 100%. Ниже на платах HDI. | (Цепи с тестовыми точками / Общее количество цепей) × 100. |

| Покрытие компонентов | Гарантирует установку правильных деталей. | 85% - 98%. Ограничено параллельными шунтирующими конденсаторами. | Количество компонентов с проверенными значениями / Общее количество в спецификации. |

| Покрытие цепей | Проверяет непрерывность и изоляцию. | 95% - 100%. Критично для силовых и земляных плоскостей. | Количество полностью протестированных цепей / Общее количество в списке цепей. |

| Частота ложных отказов | Высокая частота ложных отказов замедляет производство и повреждает контактные площадки. | < 500 PPM. Зависит от качества оснастки и нагрузки. | (Ложные тревоги / Общее количество протестированных плат) × 1 000 000. |

| Оценка PCOLA | Проверяет Присутствие, Корректность, Ориентацию, Работоспособность, Выравнивание. | Высокая. Важно для сложных ИС и разъемов. | Автоматизированный программный анализ генерации тестовой программы. |

| Оценка SOQ | Проверяет Короткие замыкания, Обрывы, Качество (целостность паяного соединения). | Критическая. Должна быть близка к 100% для безопасности ПЛК. | Измеряется по пороговым значениям сопротивления во время фазы теста на короткое замыкание/обрыв. |

| Gauge R&R | Обеспечивает согласованность и повторяемость тестовой оснастки. | < 10%. Если >30%, тестовая система ненадежна. | Статистический анализ повторяющихся измерений на одном и том же устройстве. |

Руководство по выбору по сценариям (компромиссы)

Различные производственные сценарии диктуют различные подходы к достижению оптимального тестового покрытия.

Достижение 100% заводского ICT-покрытия для ПЛК часто физически невозможно или экономически нецелесообразно. Вы должны выбрать правильную стратегию, основанную на жизненном цикле вашего продукта и технических ограничениях. Ниже приведены распространенные сценарии и рекомендуемый подход для каждого.

1. Крупносерийное, низкоассортиментное производство

- Сценарий: Массовое производство стандартных модулей ввода/вывода ПЛК.

- Рекомендация: Инвестировать в высококачественную вакуумную оснастку с двусторонним зондированием.

- Компромисс: Высокая первоначальная стоимость оснастки (5–15 тыс. $), но самое низкое время тестирования на единицу и высочайшая повторяемость.

- Аналитика APTPCB: При объемах более 5000 единиц стоимость оснастки быстро окупается, оправдывая затраты для максимального охвата.

2. Прототип и NPI (Внедрение нового продукта)

- Сценарий: Первый запуск новой платы ЦП ПЛК.

- Рекомендация: Используйте тестирование летающими щупами (FPT) вместо стационарного приспособления ICT.

- Компромисс: Нулевая стоимость оснастки, но очень медленное время тестирования на плату.

- Почему: Изменения в дизайне часты. FPT позволяет обновлять тестовые точки в программном обеспечении без перестройки физического приспособления.

3. Конструкции с высокой плотностью межсоединений (HDI)

- Сценарий: Компактные ПЛК, использующие микропереходы и BGA с малым шагом.

- Рекомендация: Комбинируйте ICT с граничным сканированием (JTAG) и автоматической рентгеновской инспекцией (AXI).

- Компромисс: Щупы ICT не могут достичь каждой цепи в технологии печатных плат HDI. Вы должны полагаться на JTAG для цифровой логики и на рентген для паяных соединений BGA.

- Риск: Полагаясь исключительно на ICT здесь, вы получите низкое покрытие (<60%).

4. ПЛК, критичные для безопасности (SIL 3 / SIL 4)

- Сценарий: ПЛК, используемые в системах аварийного отключения.

- Рекомендация: Избыточное тестирование. 100% покрытие ICT на сетях безопасности, за которым следует 100% FCT.

- Компромисс: Самая высокая стоимость и самое длительное время цикла.

- Фокус: Соблюдение стандартов безопасности при проектировании печатных плат ПЛК часто требует физических изоляционных прорезей, что может усложнить вакуумную герметизацию приспособлений. Здесь предпочтительны механические прижимные приспособления.

5. Промышленные контроллеры высокого напряжения

- Сценарий: ПЛК, напрямую управляющие входами 220В/480В.

- Рекомендация: Выборочное внутрисхемное тестирование (ICT). Не тестируйте высоковольтные цепи напрямую, если тестер не может справиться с потенциальным разрядом.

- Компромисс: Меньшее покрытие по входам питания для защиты тестового оборудования.

- Смягчение: Используйте визуальный контроль (AOI) для высоковольтной секции и ICT для низковольтной логики.

6. Платы с покрытием (конформное покрытие)

- Сценарий: ПЛК, предназначенные для влажных или агрессивных сред.

- Рекомендация: Тестировать до нанесения покрытия. Если требуется тестирование после нанесения покрытия, используйте токопроводящие резиновые наконечники или специализированную маскировку.

- Компромисс: Маскировка увеличивает трудозатраты. Прокалывающие зонды могут повредить покрытие, нарушая защиту от влаги.

От проектирования к производству (контрольные точки реализации)

Успешная реализация ICT — это линейный процесс, который начинается задолго до окончательной доработки топологии печатной платы.

Для обеспечения высокого заводского покрытия ICT для ПЛК разработчики должны следовать строгому рабочему процессу Design for Test (DFT). Добавление тестовых точек на готовый макет — это путь к проблемам с целостностью сигнала и плохому покрытию.

- Этап схемы - Приоритизация цепей: Определите критические цепи (питание, сброс, тактовые сигналы, шины связи). Отметьте их как "Обязательно к тестированию" в схеме.

- Этап компоновки - Размещение тестовых точек: Размещайте тестовые точки (ТТ) на нижней стороне печатной платы, когда это возможно. Односторонние оснастки значительно дешевле и надежнее двусторонних.

- Выравнивание по сетке: Выровняйте ТТ по сетке 2,54 мм (100 мил) или 1,27 мм (50 мил). Точки вне сетки требуют дорогостоящего индивидуального сверления для оснастки.

- Геометрия ТТ: Используйте минимальный диаметр контактной площадки от 0,8 мм до 1,0 мм для стандартных щупов. Меньшие контактные площадки (0,5 мм) требуют дорогих, хрупких щупов.

- Правила зазоров: Поддерживайте зазор не менее 1,5 мм между тестовыми точками и корпусами компонентов, чтобы предотвратить удар головки щупа по компоненту.

- Соображения ЭМС: При работе с зонированием ЭМС и заземлением для ПЛК убедитесь, что тестовые точки на высокоскоростных линиях не действуют как антенны. Используйте "бесшлейфовые" тестовые точки или при необходимости закройте их заземляющим экраном.

- Технологические отверстия: Включите как минимум два неметаллизированных технологических отверстия (3 мм+) в противоположных углах. Они выравнивают печатную плату относительно оснастки. Без них точное зондирование невозможно.

- Генерация Gerber: Экспортируйте специальный файл "Тестовая точка" или список цепей IPC-356. Не полагайтесь на производителя, который будет угадывать, какие контактные площадки предназначены для тестирования.

- Изготовление оснастки: Отправьте данные производителю оснастки за 2-3 недели до изготовления печатной платы.

- Отладка: Первый проход обычно дает ложные сбои. Настройте допуски программного обеспечения (например, разброс резисторов), а не физически изменяйте плату.

- Тестирование тензодатчиков: Перед массовым производством измерьте механическое напряжение, которое приспособление оказывает на печатную плату. Чрезмерный изгиб может привести к растрескиванию керамических конденсаторов.

- Документация: Создайте "Отчет о покрытии", подробно описывающий, какие цепи тестируются, а какие пропускаются. Это жизненно важно для будущего устранения неполадок.

Подробные спецификации по требованиям к компоновке см. в наших рекомендациях DFM.

Распространенные ошибки (и правильный подход)

Даже опытные инженеры попадают в ловушки, которые снижают охват или увеличивают производственные затраты.

Избегание этих ловушек гарантирует, что ваша стратегия заводского ICT-покрытия для ПЛК будет эффективной и безопасной.

- Ошибка: Размещение тестовых точек под BGA или низкопрофильными компонентами.

- Исправление: Тестовые точки должны быть доступны. Если цепь доступна только под BGA, выведите ее на переходное отверстие или выделенную площадку.

- Ошибка: Полагаться на "Via-in-Pad" для зондирования.

- Исправление: Зондирование металлизированных переходных отверстий может вызвать "растрескивание бочки" или ненадежный контакт из-за пустот припоя. Всегда используйте плоскую, твердую тестовую площадку.

- Ошибка: Игнорирование высоких компонентов.

- Исправление: Высокие конденсаторы или трансформаторы на нижней стороне мешают плате ровно лежать на приспособлении. Держите нижнюю сторону относительно плоской или создайте "запретные" зоны для высоких компонентов.

- Ошибка: Предположение о необходимости 100% покрытия.

- Исправление: Погоня за последними 5% покрытия (обычно это шунтирующие конденсаторы или подтягивающие резисторы) может удвоить стоимость приспособления. Допустите меньшее покрытие для некритичных пассивных компонентов, если контроль процесса хороший.

- Ошибка: Забыть о процедуре "разряда".

- Исправление: Большие конденсаторы в ПЛК накапливают энергию. Приспособление ICT должно иметь разрядную цепь, чтобы предотвратить выход из строя щупов тестера при контакте.

- Ошибка: Использование паяльной маски поверх контрольных точек.

- Исправление: Контрольные точки должны быть открыты от маски. Щупы не могут надежно проникать через паяльную маску, не повреждая наконечник или плату.

- Ошибка: Пренебрежение плотностью щупов.

- Исправление: Слишком много щупов на небольшой площади (высокая плотность) создает огромное давление вверх, потенциально деформируя плату. Распределяйте контрольные точки равномерно.

- Ошибка: Игнорирование стандартов производства печатных плат для промышленного контроля.

- Исправление: Промышленные платы имеют более толстую медь и другие тепловые профили. Убедитесь, что параметры тестирования учитывают более высокую токовую нагрузку дорожек.

Часто задаваемые вопросы (FAQ)

В: Какова типичная стоимость приспособления ICT для ПЛК? A: Стандартная оснастка типа "ложе гвоздей" обычно стоит от 2 000 до 6 000 долларов, в зависимости от количества тестовых точек и того, является ли она односторонней или двусторонней.

В: Может ли внутрисхемный тест (ICT) тестировать программное обеспечение на ПЛК? О: В целом, нет. ICT тестирует аппаратное обеспечение (физику). Однако некоторые продвинутые системы ICT могут выполнять "Flash-программирование" для загрузки начального загрузчика, что является мостом к тестированию программного обеспечения.

В: Чем ICT отличается от тестирования летающим зондом? О: ICT использует фиксированную оснастку для одновременного тестирования всех точек (быстро, высокие затраты на настройку). Летающий зонд использует движущиеся роботизированные манипуляторы для последовательного тестирования точек (медленно, нулевые затраты на настройку). ICT предназначен для серийного производства; летающий зонд — для прототипов.

В: Каково минимальное расстояние между тестовыми точками? О: Для стандартных зондов (100 мил) сохраняйте расстояние 2,54 мм от центра к центру. Для мелкого шага (50 мил) можно уменьшить до 1,27 мм, но стоимость оснастки увеличивается, а долговечность снижается.

В: Повреждает ли ICT печатную плату? О: Он оставляет небольшие "следы контакта" (вмятины) на тестовых площадках. Это нормально и приемлемо. Однако чрезмерное давление может привести к трещинам в паяных соединениях, поэтому требуется тестирование тензодатчиками.

В: Могу ли я использовать переходные отверстия в качестве тестовых точек? О: Это не рекомендуется. Переходные отверстия часто закрыты паяльной маской. Даже если они открыты, они неровные. Лучше добавить выделенную тестовую площадку, подключенную к переходному отверстию.

В: Как обрабатывать тестовые точки для высокоскоростных дифференциальных пар? A: Добавление тестовой точки создает «заглушку», которая может отражать сигналы. Для высокоскоростных шин связи ПЛК используйте моделирование, чтобы убедиться, что тестовая точка не ухудшает целостность сигнала, или вместо этого тестируйте эти линии с помощью граничного сканирования.

Q: Почему мой отчет о покрытии показывает низкий процент? A: Это часто происходит, если у вас много параллельных конденсаторов (тестер видит их как один большой конденсатор) или если у вас много физически недоступных цепей (например, внутри BGA без разводки).

Q: Нужен ли мне ICT, если у меня есть AOI (автоматическая оптическая инспекция)? A: Да. AOI проверяет только, выглядит ли деталь правильно. Он не может определить, имеет ли резистор неправильное значение, неисправен ли чип или есть ли холодная пайка под компонентом.

Q: Какие данные нужны APTPCB для расчета стоимости ICT? A: Нам нужны файлы Gerber, BOM (спецификация материалов), файл XY Pick and Place и электрический Netlist (формат IPC-356).

Связанные страницы и инструменты

- Услуги тестирования ICT: Изучите наши специфические возможности в отношении аппаратного и программного обеспечения для внутрисхемного тестирования.

- Печатные платы для промышленного управления: Узнайте о специфических требованиях к материалам и изготовлению для промышленной электроники.

- Руководство по DFM: Загрузите наш контрольный список, чтобы убедиться, что ваш дизайн готов к тестированию массового производства.

Глоссарий (ключевые термины)

| Термин | Определение |

|---|---|

| Ложе гвоздей | Традиционное приспособление для внутрисхемного тестирования (ICT), содержащее сотни подпружиненных щупов, которые одновременно контактируют с печатной платой. |

| DFT (Design for Test) | Инженерная практика проектирования топологии печатной платы специально для облегчения простого и всестороннего тестирования. |

| DUT (Device Under Test) | Конкретная сборка печатной платы, находящаяся в данный момент в тестовом приспособлении. |

| Приспособление | Механический интерфейс (специальное оборудование), который удерживает печатную плату и выравнивает щупы по тестовым точкам. |

| Нетлист | Текстовый файл, описывающий электрические соединения печатной платы, определяющий, какие выводы компонентов подключены к каким цепям. |

| Пого-пин | Подпружиненный щуп, используемый в тестовых приспособлениях для установления электрического контакта с контактными площадками печатной платы. |

| IPC-356 | Стандартный формат файла, используемый для передачи координат тестовых точек и информации о цепях производителю. |

| Boundary Scan (JTAG) | Метод тестирования межсоединений на сложных ИС (таких как FPGA) без физических щупов, с использованием последовательного интерфейса. |

| След от щупа | Небольшое углубление, оставленное тестовым щупом на контактной площадке; доказательство того, что точка была протестирована. |

| Тензодатчик | Датчик, используемый для измерения физического изгиба или напряжения, приложенного к печатной плате во время вакуумного сжатия приспособления. |

| Ложный отказ | Результат теста, указывающий на дефект, хотя плата на самом деле исправна, обычно вызванный плохим контактом щупа или жесткими допусками. |

| Guard Trace | Метод в ИКТ, при котором окружающие цепи подаются на определенное напряжение для изоляции измеряемого компонента. |

Заключение (дальнейшие шаги)

Достижение высокого заводского покрытия ИКТ для ПЛК не является второстепенной задачей; это стратегическое решение, которое влияет на безопасность и надежность промышленных систем. Понимая метрики PCOLA/SOQ, выбирая правильную стратегию оснастки и придерживаясь строгих правил DFT, вы гарантируете, что каждый ПЛК, сходящий с линии, готов к суровым условиям заводского цеха.

Чтобы продвинуться вперед с вашим проектом ПЛК, APTPCB рекомендует провести всесторонний обзор DFM перед окончательной доработкой вашего макета. При запросе коммерческого предложения, пожалуйста, предоставьте:

- Файлы Gerber (включая выделенный слой тестовых точек, если доступен).

- BOM (спецификация) с номерами деталей производителя.

- Сетевой список (формат IPC-356).

- Схемы (PDF) для справки по отладке.

- Конкретные требования к тестированию (например, "Необходимо протестировать 100% цепей реле безопасности").

Высококачественное тестирование — это страховой полис для репутации вашего бренда. Начните свой путь валидации с правильными данными и правильным партнером.