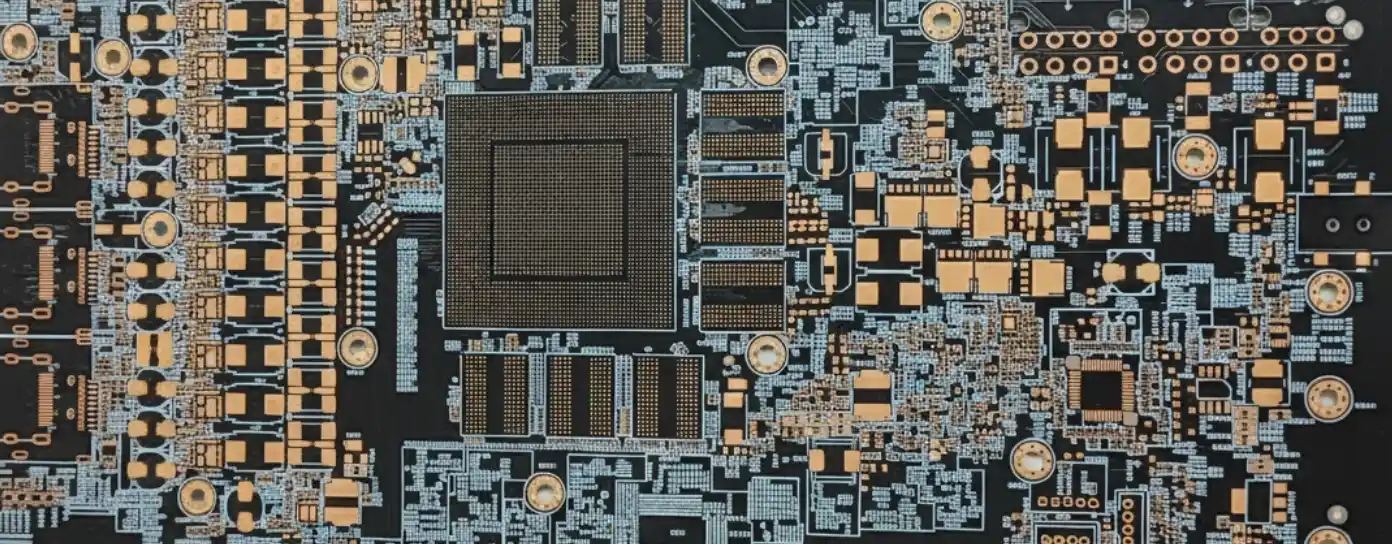

CAM workflow — превращаем дизайн‑данные в производимый HDI процесс

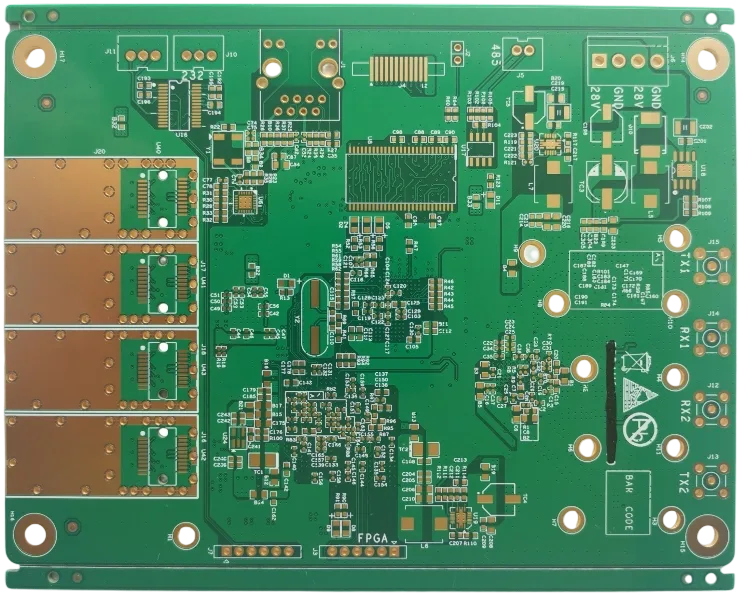

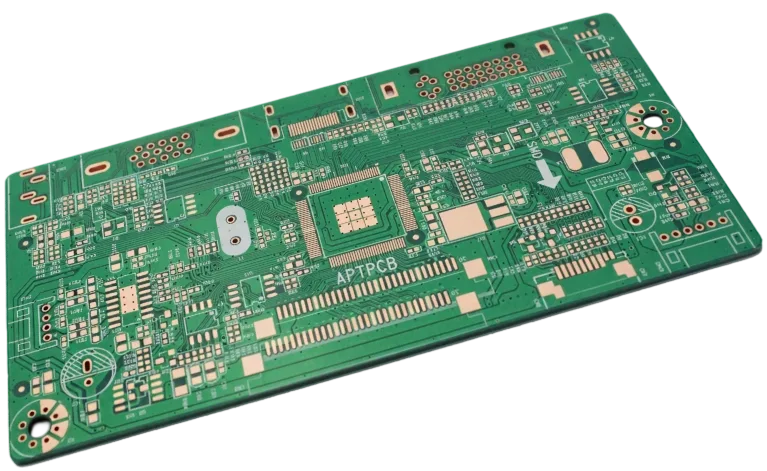

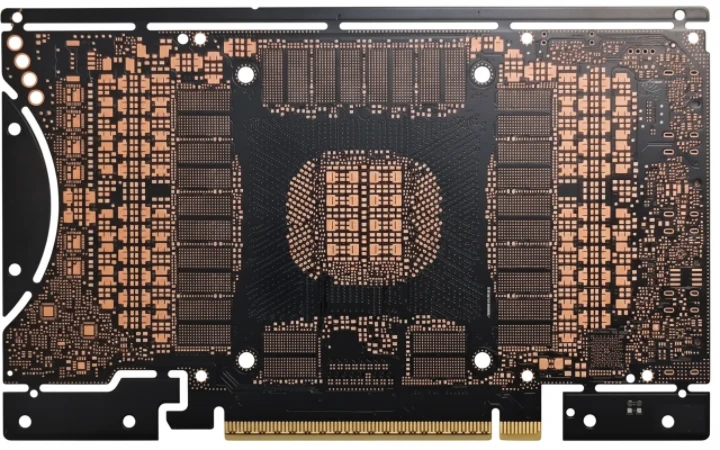

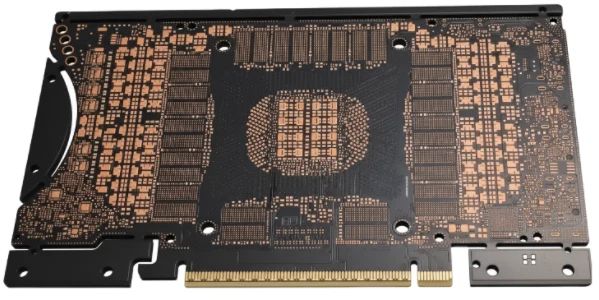

В процессе производства HDI первая ключевая фаза ведется CAM инженерами, которые переводят замысел дизайна в точный, производимый план. Получив Gerber или ODB++, они проверяют stack-up, конфигурации микровиа и требования по импедансу. Через DFM анализ, программирование сверловки и подготовку технологических примечаний CAM инженеры обеспечивают соответствие всех features производственным возможностям.

- Подтвердить структуру stack-up и конфигурацию SBU слоёв.

- Задать тип микровиа (staggered/stacked), VIPPO и правила via-in-pad.

- Провести DFM по trace/space, annular ring и зазорам via‑to‑trace.

- Определить программы лазерного сверления и профили copper fill.

- Спланировать импедансные купоны и стратегию измерения TDR.

- Проверить материалы (FR‑4/low-loss) и совместимость Tg/CTE.

- Согласовать с production engineering проверку производимости и валидацию process flow до release.