Координация CAM и SI для высокоскоростных плат

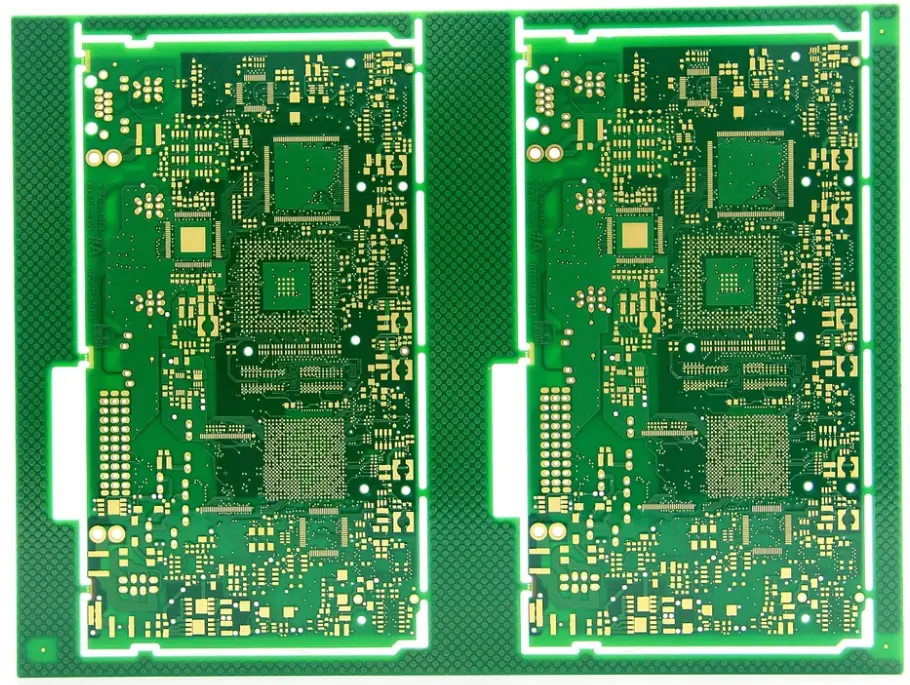

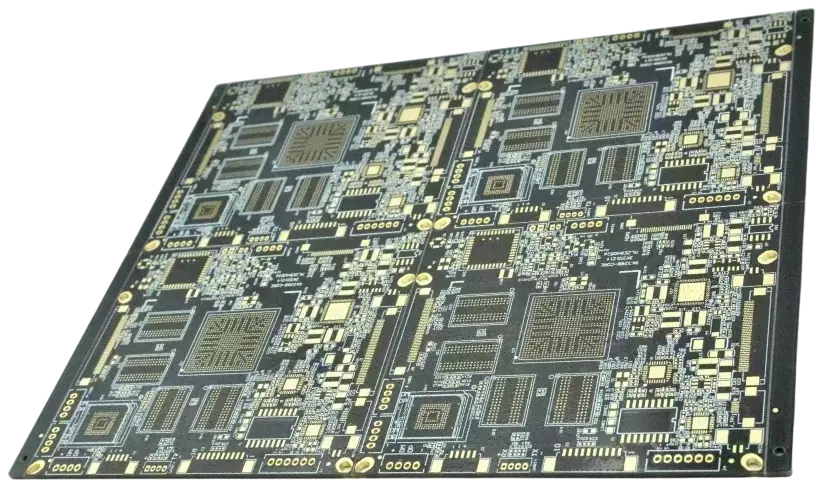

Инженеры CAM преобразуют ограничения SI в производственные файлы, определяя стеки, карты сверления, купоны импеданса и координаты обратного сверления.

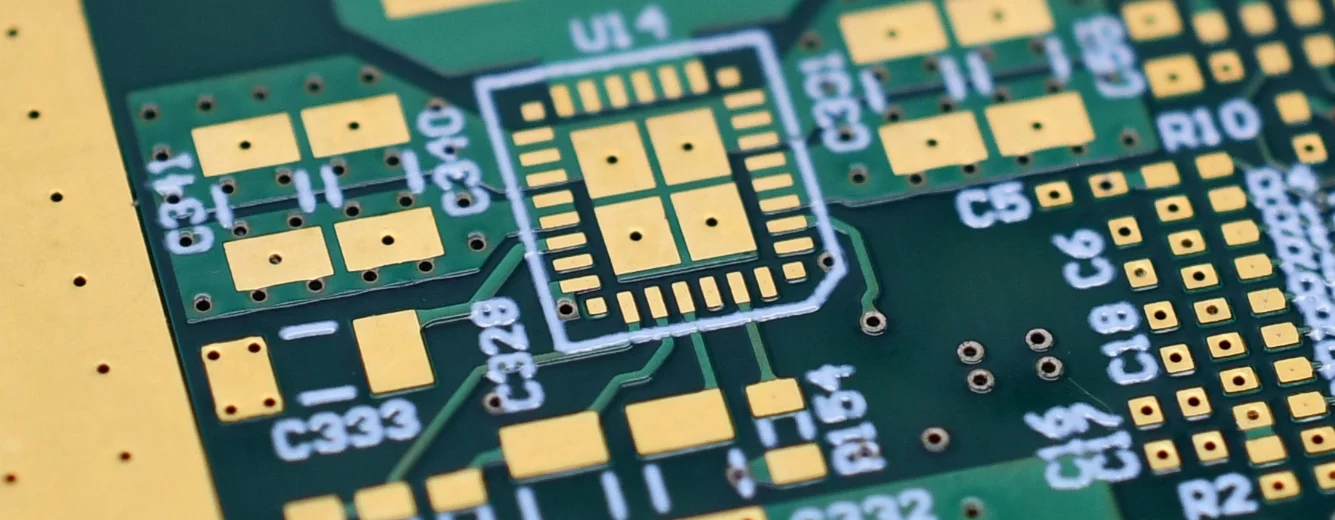

- Документируйте целевые значения диэлектрика, шероховатость меди и содержание смолы для каждого слоя.

- Определите купоны импеданса, геометрию дифференциальных пар и допуски стеков.

- Планируйте глубины обратного сверления, заполнения VIPPO и переходные отверстия для сшивки опорных плоскостей.

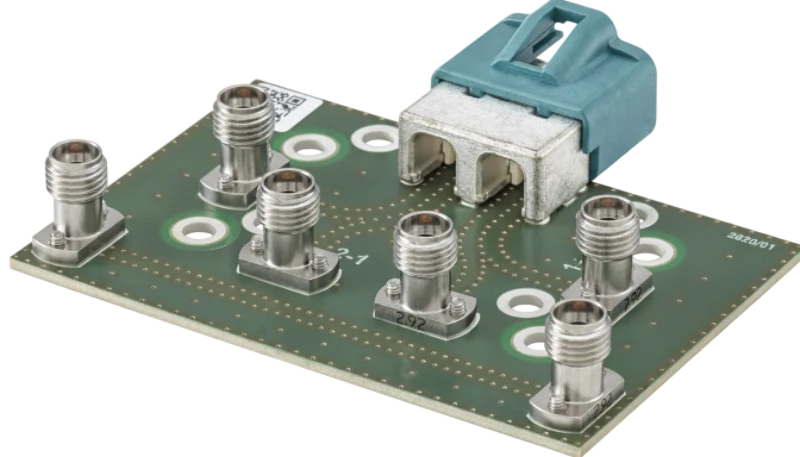

- Координируйте посадочные места запрессовываемых разъемов и требования к каплевидным контактным площадкам.

- Моделируйте или валидируйте переходы переходных отверстий с помощью выходных данных инструментов SI.

- Предоставьте инструкции по обращению и выпеканию для низкопотерных материалов.

- Выпустите производственные примечания, детализирующие разрешенные замены и контрольные точки качества.