Advanced Engineering Guide

Инженерная реальность производства PCB с большим числом слоёв

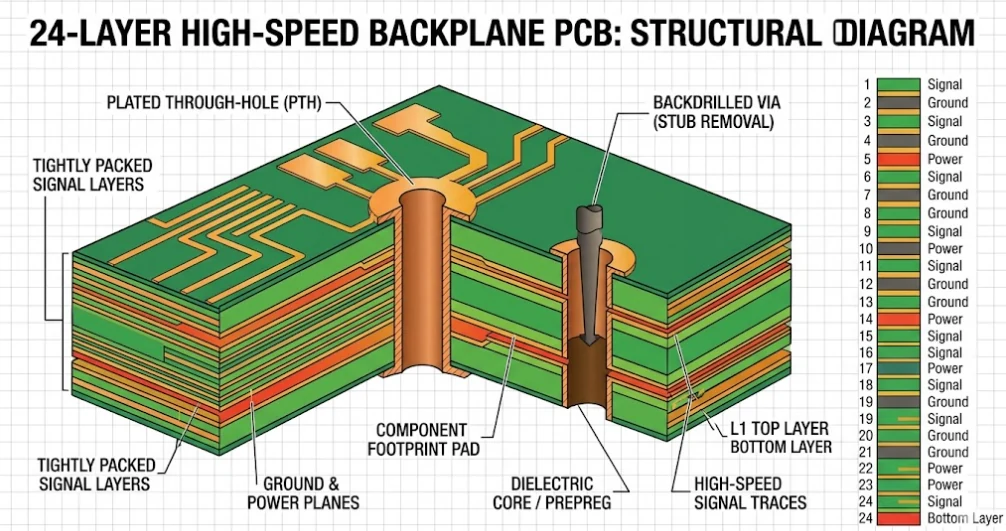

Проектирование 32-слойного backplane или 24-слойной AI motherboard в ECAD-софте — это сложная routing-задача, но её производство представляет собой борьбу с физикой, химией и термодинамикой. С ростом числа layer допуск на ошибку уменьшается экспоненциально. В APTPCB мы работаем с senior hardware engineers по всему миру, чтобы переводить такие экстремальные design из цифрового мира в физическую реальность. Ниже — глубокий разбор инженерных препятствий при производстве плат с большим числом слоёв и того, как мы их решаем.

1. Тирания регистрации и размерного scaling

Главная угроза для платы с большим числом слоёв — это failure регистрации. PCB строится путём прессования чередующихся слоёв полностью отверждённых core и неотверждённого prepreg под экстремальной температурой и гидравлическим давлением. Во время этого процесса ламинации материалы расширяются, а затем, по мере отверждения смолы и охлаждения, сжимаются. Такой размерный scaling анизотропен: усадка в направлении X и Y стеклоткани различается.

В 4-слойной плате небольшое смещение легко компенсируется annular ring, то есть медным pad вокруг просверленного отверстия. В 40-слойной плате, если внутренние layer смещаются неодинаково, механическое сверло, проходя сквозь плату, неизбежно выйдет за пределы медного pad на Layer 25, оборвав соединение или вызвав фатальный короткий замыкание с ближайшим ground plane.

Решение APTPCB: наши CAM-инженеры применяют нелинейные scaling factors к artwork каждого отдельного layer, математически прогнозируя усадку на основе плотности меди в этом слое. Во время layup мы используем системы X-Ray induction bonding для физического выравнивания внутренних слоёв между собой до цикла прессования, гарантируя точность регистрации layer-to-layer на уровне ±1.5 mil.

2. Металлизация с высоким aspect ratio: капиллярный вызов

По мере роста числа layer плата становится толще. 32-слойная плата легко может достигать толщины 5.0 mm (200 mil). Если требуется просверлить через неё via диаметром 10 mil (0.25 mm), образуется микроскопическая капиллярная трубка с aspect ratio 20:1.

Стандартные DC electroplating systems полагаются на гидродинамику, чтобы прокачивать богатые медью химические ванны через отверстия. В via 20:1 жидкость в центре barrel застаивается. Ионы меди истощаются, и процесс металлизации останавливается, в результате чего получается via с толстым медным слоем на поверхности, но опасно тонким или отсутствующим медным слоем в середине. При экстремальной температуре SMT reflow или wave soldering расширение платы по оси Z легко разрывает такой тонкий barrel, вызывая прерывистые обрывы, которые notoriously трудно отладить.

Решение APTPCB: для плат с aspect ratio выше 10:1 мы применяем Periodic Reverse Pulse Plating. Вместо непрерывного постоянного тока система быстро импульсно подаёт ток вперёд, а затем кратко разворачивает его. Обратный импульс действует как электрический "насос", удаляя истощённую химию и протягивая свежую богатую медью жидкость глубоко в центр via. Это гарантирует толстую и равномерную стенку barrel, выдерживающую многократные бессвинцовые reflow cycle.

3. Устранение резонанса сигнала с помощью прецизионного backdrilling

В high-speed digital архитектурах, таких как PCIe Gen5, 100G/400G Ethernet и 112G PAM4, физическая геометрия via становится активным RF-компонентом. Представьте сигнал, идущий от Layer 1 к Layer 5 на 24-слойном backplane. Сигнал успешно выходит на Layer 5, но оставшийся медный via barrel, продолжающийся от Layer 6 до Layer 24, работает как незавершённая антенна, то есть "via stub". Этот stub отражает электромагнитную энергию обратно в канал, создаёт разрушительные интерференции и закрывает eye diagram.

Решение APTPCB: для восстановления целостности сигнала мы используем Controlled-Depth Backdrilling. С помощью продвинутых CNC drilling machines, оснащённых проводящей технологией surface sensing, сверло заходит с нижней стороны платы (Layer 24) и высверливает нежелательный медный stub, точно останавливаясь до активного сигнального layer (Layer 5). Мы регулярно достигаем точности глубины ±50μm, оставляя безопасный остаточный stub менее 8-10 mil, тем самым очищая канал от разрушительных резонансов.

4. Управление импедансом в толстых архитектурах

В 6-слойной плате single-ended трасса на 50Ω может требовать ширины 6 mil. В 32-слойной плате, поскольку приходится использовать ultra-thin prepreg, например толщиной 2 mil, чтобы удержать общую толщину платы в допустимых пределах, расстояние между сигнальной трассой и её reference ground plane резко уменьшается. Чтобы сохранить те же 50Ω, ширина трассы должна уменьшаться пропорционально, часто до 2.5 или 3 mil.

Травление 3-mil trace с допуском по импедансу ±5% требует абсолютного контроля химии. Решение APTPCB: мы используем Laser Direct Imaging (LDI) для получения точности экспонирования на sub-mil уровне в сочетании с вакуумными линиями травления, которые вытягивают кислоту из промежутков между плотными trace и предотвращают undercut. Мы моделируем каждую impedance structure в Polar Si9000 и физически проверяем результат через TDR coupon на каждом производственном panel.