Содержание

- Контекст: почему обеспечить качество интерфейса соответствия сетевому коду сложно

- Ключевые технологии (Что действительно обеспечивает работоспособность)

- Взгляд на экосистему: связанные платы / интерфейсы / этапы производства

- Сравнение: типовые варианты и что вы получаете / теряете

- Опоры надежности и производительности (Сигнал / Питание / Тепловой режим / Контроль процесса)

- Будущее: куда движется направление (Материалы, интеграция, ИИ/автоматизация)

- Запрос КП / DFM-проверка для качества интерфейса соответствия сетевому коду (Что отправлять)

- Заключение

Ключевые тезисы

- Целостность сигнала критична: точность сетевого измерения (LVRT/HVRT) напрямую зависит от малошумящей топологии PCB и точного размещения компонентов.

- Изоляция и безопасность: корректные пути утечки, воздушные зазоры и выбор материалов (значения CTI) предотвращают опасные дуговые аварии.

- Тепловая устойчивость: интерфейсные платы часто находятся рядом с горячими силовыми модулями и должны выдерживать циклические температуры без расслоения.

- Повторяемость производства: автоматизированный контроль (AOI/SPI) удерживает одинаково высокий стандарт соответствия сети для каждой единицы.

Контекст: почему обеспечить качество интерфейса соответствия сетевому коду сложно

Разработка и производство интерфейса для сетевого оборудования, будь то ветрогенераторы, солнечные инверторы или системы хранения энергии на аккумуляторах (BESS), всегда требуют баланса между чувствительностью измерений и промышленной стойкостью. Платы должны улавливать минимальные изменения частоты и напряжения сети, чтобы вовремя активировать режимы соответствия, например Low Voltage Ride Through (LVRT). При этом они работают в непосредственной близости от мощных коммутирующих устройств (IGBT или SiC MOSFET), создающих выраженные электромагнитные помехи (EMI).

Для APTPCB (APTPCB PCB Factory) ключевая сложность в том, чтобы удерживать строгий контроль импеданса и чистоты на этапе изготовления. Даже небольшое отклонение толщины диэлектрика или минимальный остаток флюса могут ухудшить точность измерений либо ослабить высоковольтную изоляцию. Дополнительно сетевые нормы (например, IEEE 1547 и UL 1741) практически не допускают отклонений. Если плата со временем уходит по параметрам из-за недостаточного качества материалов, это может привести к внезапному отключению всей энергетической установки и серьезным финансовым потерям.

Ключевые технологии (Что действительно обеспечивает работоспособность)

Высокое качество интерфейса соответствия сетевому коду достигается только при сочетании продвинутых технологий изготовления PCB и точных процессов сборки.

- Гальваническая развязка: интерфейс обязан разделять низковольтную логику управления (DSP/FPGA) и высоковольтное сетевое подключение. Обычно применяются ширококорпусные оптопары или цифровые изоляторы. В разводке PCB требуется корректное трассирование изоляционных прорезей, чтобы исключить поверхностные токи утечки.

- Прецизионная аналоговая топология: для точного измерения сетевого напряжения и тока используются дифференциальные пары и выделенные аналоговые земли. Это уменьшает площадь петли и снижает восприимчивость к наводкам от силового переключения рядом.

- Материалы с высоким CTI: базовый ламинат играет критическую роль. FR4 с высоким сравнительным индексом трекинг-стойкости (CTI) лучше противостоит электрическому пробою и трекингу даже во влажной или загрязненной среде, характерной для наружных систем.

- Толстая медь и тепловые via: даже если сама интерфейсная часть маломощная, она часто проводит управляющие сигналы или располагается рядом с силовыми шинами. Трассы PCB с толстой медью и правильно расставленные тепловые via помогают отводить тепло, сохраняя точность чувствительных пассивных компонентов.

Взгляд на экосистему: связанные платы / интерфейсы / этапы производства

Интерфейс соответствия сети не существует отдельно. Он связывает «мышцы» (силовые модули) и «мозг» (центральный контроллер).

- Силовой каскад: интерфейсная плата получает обратную связь от силового каскада. Если топология платы для силовой энергетики выполнена слабо, шум напрямую попадет в измерительный тракт.

- Плата управления затвором: интерфейс соответствия часто передает сигналы на отдельную плату. Разъемы и кабели между ними должны быть согласованы по импедансу, иначе отражения (звон) вызовут ложные срабатывания.

- Сборка и защитное покрытие: после сборки такие платы почти всегда требуют конформного покрытия. Этот этап защищает чувствительные измерительные цепи от влаги и пыли в полевых условиях. Качественный интерфейсный дизайн предусматривает зоны запрета покрытия, чтобы материал не мешал разъемам и тестовым точкам.

Сравнение: типовые варианты и что вы получаете / теряете

При выборе параметров интерфейсной платы инженерная команда постоянно работает с компромиссами. Достаточно ли стандартной 4-слойной структуры, или стоит перейти на 6 слоев ради лучшей помехоустойчивости? Хватит ли обычного FR4, или целесообразно закладывать более дорогие диэлектрики?

Матрица ниже помогает оценить практический результат каждого выбора.

Матрица решений: технический выбор → практический результат

| Технический выбор | Прямое влияние |

|---|---|

| 4-слойная vs 6-слойная структура | 6 слоев позволяют разделить аналоговые и цифровые земляные плоскости, что заметно улучшает отношение сигнал/шум (SNR) при сетевых измерениях. |

| Стандартный FR4 vs FR4 с высоким CTI | Высокий CTI (>600V) снижает риск углеродного трекинга в зонах высокого напряжения и помогает соответствовать требованиям UL/IEC в компактных конструкциях. |

| Покрытие HASL vs ENIG | ENIG дает более ровную поверхность для мелкого шага выводов (например, DSP) и лучшую коррозионную стойкость, чем HASL, в долгосрочной эксплуатации. |

| Сборка Class 2 vs Class 3 | Class 3 обеспечивает более высокую надежность за счет строгих критериев по заполнению припоем и выравниванию компонентов, что особенно важно для критической инфраструктуры. |

Опоры надежности и производительности (Сигнал / Питание / Тепловой режим / Контроль процесса)

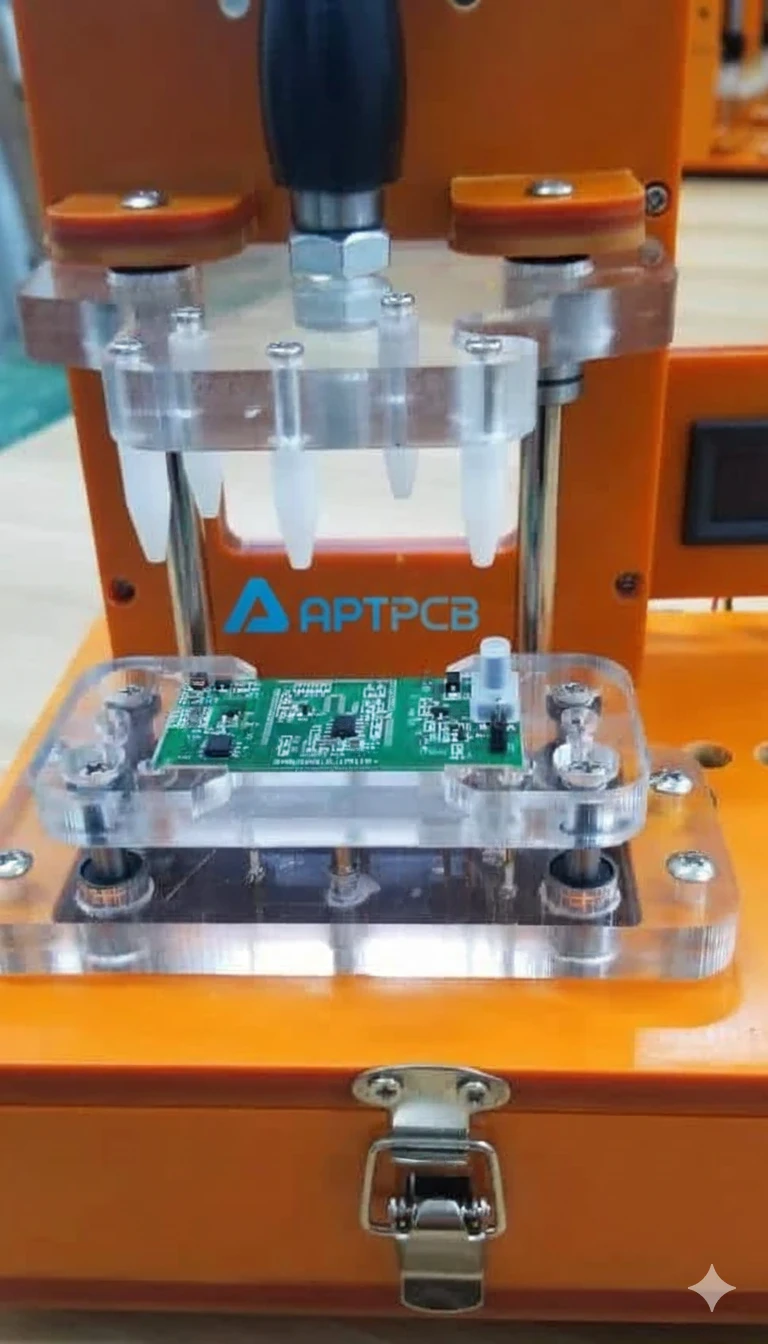

Чтобы интерфейс соответствия сети стабильно выполнял целевые требования, APTPCB применяет строгий процесс верификации. Недостаточно просто смонтировать компоненты: необходимо подтвердить, что плата выдерживает электрические и механические нагрузки реальной сети.

Ключевые опоры верификации

| Опора | Что проверяется | Критерий приемки |

|---|---|---|

| Целостность сигнала | Аналоговые линии измерения (Напряжение/Ток) | Уровень шума < 10mV; отсутствие перекрестных помех, влияющих на точность. |

| Изоляция | Барьер между высоким и низким напряжением | Прохождение Hi-Pot при 2.5kV (или по целевому стандарту) с током утечки < 1mA. |

| Тепловая нагрузка | Паяные соединения при циклировании | Отсутствие трещин после 1000 циклов (-40°C до +125°C). |

| Чистота | Ионные загрязнения | < 1.56 µg/cm² в эквиваленте NaCl для предотвращения электрохимической миграции. |

Контроль процесса во время сборки PCB не менее важен. Automated Optical Inspection (AOI) обнаруживает отсутствующие или смещенные компоненты, а In-Circuit Testing (ICT) подтверждает, что пассивные элементы (резисторы/конденсаторы) в измерительной сети находятся в допуске. Номинал 1% с фактическим отклонением 5% уже может привести к отказу по соответствию сети.

Будущее: куда движется направление (Материалы, интеграция, ИИ/автоматизация)

По мере того как энергосистема становится «умнее», а силовая электроника переходит на карбид кремния (SiC) и нитрид галлия (GaN), требования к качеству интерфейса возрастают. Более высокие частоты переключения означают больше EMI, а значит нужны более плотные правила топологии и более качественные материалы.

Траектория производительности на 5 лет (иллюстративно)

| Показатель | Сегодня (типично) | Ориентир через 5 лет | Почему это важно |

|---|---|---|---|

| Рабочая частота переключения | 20kHz - 50kHz | 100kHz - 500kHz | Рост частоты уменьшает размеры пассивных элементов, но повышает чувствительность к EMI и требует более продвинутой многослойной структуры. |

| Уровень интеграции | Дискретное измерение и управление | Интегрированные интеллектуальные модули | Объединение измерения, управления и связи на одной HDI-плате сокращает этапы сборки, но увеличивает сложность. |

| Аналитика данных | Базовые флаги состояния | ИИ-аналитика в реальном времени | Интерфейсы будут локально обрабатывать данные (Edge AI), чтобы прогнозировать сетевые отказы до их появления. |

Запрос КП / DFM-проверка для качества интерфейса соответствия сетевому коду (Что отправлять)

Когда вы переводите проект сетевого интерфейса из прототипа в серию, полный пакет данных необходим для точного расчета стоимости и корректной DFM-проверки.

- Gerber-файлы: формат RS-274X, включая все медные слои, паяльную маску и шелкографию.

- Чертеж изготовления: укажите класс IPC (2 или 3), требования к материалу (например, Tg 170, CTI > 600) и примечания по контролю импеданса.

- Детали многослойной структуры: задайте порядок слоев и толщины диэлектриков, если импеданс критичен.

- BOM (Bill of Materials): включите производительские артикулы, особенно для критичных изоляционных компонентов и прецизионных резисторов.

- Примечания по сборке: отметьте специальные требования, например селективную пайку для выводных разъемов или параметры конформного покрытия.

- Требования к тестированию: определите, нужны ли на заводе ICT, FCT (Functional Circuit Test) и/или Hi-Pot.

- Объем и срок поставки: оценка годового потребления и целевые даты поставок.

Заключение

Качество интерфейса соответствия сетевому коду — это не формальная отметка, а основа стабильной и безопасной энергосистемы. Грамотно спроектированный интерфейс обеспечивает надежную совместную работу возобновляемых источников и систем хранения с сетевой инфраструктурой, прохождение аварийных режимов и сохранение синхронизации.

Опора на надежные материалы, точную топологию и строгую верификацию помогает избежать дорогих провалов сертификации и отзывов в эксплуатации. Независимо от того, проектируете ли вы компактный бытовой инвертор или крупный узел энергосистемы, сотрудничество с опытным производителем вроде APTPCB повышает итоговую надежность и производительность интерфейсных плат.