Инвестиции в Design for Manufacturability (DFM) и Design for Testability (DFT) меняют сам подход к качеству: вместо реактивного исправления дефектов после появления проблемы вы переходите к их предупреждению еще до запуска производства. Для закупщиков и product manager понимание того, как снижать дефекты PCBA с помощью DFM и DFT, является одним из самых действенных способов уменьшить совокупную стоимость проекта и ускорить вывод изделия на рынок. В этом материале собраны технические требования и логика принятия решений, которые помогают согласовать конструкторскую документацию с реальными возможностями производства.

Ключевые моменты

- Предотвращение на ранней стадии: DFM заранее выявляет проблемы layout, которые приводят к перемычкам, tombstoning и void.

- Покрытие тестированием: DFT гарантирует, что если дефект все же возникнет, его можно будет обнаружить через ICT или функциональный тест, а не уже в эксплуатации.

- Снижение затрат: Исправление дефекта на стадии проектирования обходится примерно в 10x дешевле, чем на стадии сборки, и примерно в 100x дешевле, чем после отгрузки в поле.

- Согласование с поставщиком: Четкие требования к stencil и профилям reflow критичны для сложных компонентов, таких как BGA и QFN.

Основные выводы

Прежде чем переходить к деталям, полезно увидеть, как DFM и DFT напрямую влияют на стоимость и надежность изделия.

| Feature | DFM (Design for Manufacturability) | DFT (Design for Testability) |

|---|---|---|

| Главная цель | Обеспечить стабильную воспроизводимую сборку с высоким выходом годных. | Обеспечить быструю и точную проверку изделия. |

| Фокус по дефектам | Предотвращает появление дефектов, например мостов припоя. | Выявляет дефекты, которые все же возникли, например обрывы цепей. |

| Ключевой результат | Оптимизированные геометрии pad, thermal relief, зазоры между компонентами. | Test point, доступ JTAG, scan chain. |

| Драйвер ROI | Более высокий First Pass Yield (FPY), меньше переделок. | Более низкий уровень отказов в поле, быстрее диагностика. |

Как снизить дефекты PCBA с помощью DFM и DFT: область применения, контекст решения и критерии успеха

Снижение дефектности начинается не на линии SMT, а еще на этапе схемы и layout. Когда заказчик задается вопросом, как снизить дефекты PCBA через DFM и DFT, он должен понимать, что приобретает не просто плату как товар, а подтвержденную производственную способность процесса.

Контекст решения

Закупка почти всегда балансирует между дополнительным инженерным временем в начале проекта и скоростью выпуска дальше по цепочке. Если пропустить DFM-проверку ради ускорения прототипа, очень часто это приводит к платам, которые сложно собрать, или к высокому уровню брака в серийном производстве. Нужный уровень анализа зависит от сложности PCBA. Простая плата с крупными пассивными элементами может потребовать минимальной DFM-проверки, а HDI-плата с BGA требует глубокой и строгой оценки.

Критерии успеха

Чтобы понять, работают ли меры DFM и DFT, стоит отслеживать как минимум следующие показатели:

- First Pass Yield (FPY): доля плат, прошедших все тесты без переделки. Для зрелых продуктов типичная цель составляет 98%+.

- Покрытие тестами: доля net и компонентов, доступных автоматическому тестированию. Для сильного DFT ориентиром служит 90%+.

- Доля ложных отказов: как часто хорошие платы ошибочно бракуются из-за неудачных тестовых лимитов или нестабильных fixture.

- Engineering Change Orders (ECO): уменьшение числа ECO, связанных со сборкой, показывает, что DFM внедрен правильно.

Требования, которые нужно определить заранее

| Parameter | Recommended value / option | Why it matters | How to verify |

|---|---|---|---|

| Layer count | 4–8 (типично), при необходимости больше | Влияет на стоимость, выход годных и запас по трассировке | Stackup + DFM-report |

| Min trace/space | 4/4 mil (типично) | Влияет на выход и срок изготовления | DRC + производственная capability |

| Via strategy | Through vias vs VIPPO vs microvia | Влияет на надежность сборки | Микрошлиф + критерии IPC |

| Surface finish | ENIG/OSP/HASL | Влияет на паяемость и планарность | COC + тесты на паяемость |

| Solder mask | Матовая зеленая по умолчанию | Повышает читаемость AOI и снижает риск перемычек | AOI-проба + регистрация маски |

| Test | Flying probe / ICT / FCT | Компромисс между покрытием и стоимостью | Coverage report + план fixture |

| Acceptance class | IPC Class 2 / 3 | Определяет допустимые пределы дефектов | Примечания в чертеже + отчет инспекции |

| Lead time | Standard vs expedited | Влияет на риск по графику | Коммерческое предложение + подтверждение мощности |

Чтобы DFM и DFT реально работали, определенные требования должны быть явно прописаны в data package. Любая неоднозначность приводит к допущениям на производстве, а это один из главных источников дефектов.

1. Требования к данным для DFM

Передавайте contract manufacturer (CM) не только Gerber-файлы.

- Выбор IPC Class: явно укажите, должна ли плата соответствовать IPC-A-610 Class 2 или Class 3. От этого зависят критерии по объему припоя и выравниванию.

- Footprint компонентов: требуйте проверки footprint по Bill of Materials (BOM). Несовпадение между реальным компонентом и land pattern является одной из самых частых DFM-проблем.

- Стратегия panelization: определите структуру panel. Неудачная panelization может вызвать трещины от механических напряжений в керамических конденсаторах при depaneling.

- Перемычки solder mask: задайте минимальную ширину solder mask между pad, обычно 4 mil, чтобы избежать перемычек на fine-pitch IC.

2. Требования к данным для DFT

DFT часто вспоминают слишком поздно, и в итоге получают дорогие bed of nails fixture, которые даже не достают до критичных net.

- Доступность test point: требуйте, чтобы у всех критичных net был test point на нижней стороне PCB. Это позволяет делать односторонний In-Circuit Test (ICT), который заметно дешевле.

- Clearance вокруг test point: задайте минимальный зазор, например 50 mil, между test point и высокими компонентами, чтобы исключить повреждение щупов.

- JTAG/Boundary Scan: на сложных цифровых платах убедитесь, что цепочка JTAG разведена и доступна. Это позволяет тестировать соединения между микросхемами без физического контакта с каждым узлом.

- Netlist: всегда передавайте netlist в формате IPC-356. Она дает производителю возможность сравнить электрическую связность Gerber с связностью схемы.

Связанные материалы

Ключевые риски: первопричины, раннее выявление и профилактика

Понимание конкретных типов дефектов помогает правильно расставить приоритеты в DFM-проверках. Самые сложные проблемы часто связаны с компонентами с нижними выводами, такими как QFN (Quad Flat No-lead) и BGA.

1. Void в QFN и BGA

Void представляют собой воздушные полости внутри паяного соединения. Избыточное количество void ухудшает теплопроводность и снижает механическую прочность.

- Риск: перегрев мощных QFN из-за плохого отвода тепла через паяное соединение с большим количеством void.

- Профилактика (DFM): применяйте qfn reflow best practices to reduce voids. Речь идет о делении apertures на thermal pad на несколько окон. Вместо одного большого отпечатка пасты, который удерживает газы, делают сетку небольших квадратов с покрытием около 50-70%, чтобы во время reflow летучие компоненты могли выходить по каналам дегазации.

2. Дефекты пайки BGA: мосты и opens

BGA сложны тем, что их соединения скрыты.

- Риск: дефект Head-in-Pillow (HiP), когда шарик припоя лежит на пасте, но полноценного слияния не происходит.

- Профилактика (DFM/процесс): требуется строгий контроль по bga voiding control: stencil, reflow, and x-ray criteria.

- Stencil: используйте электрополированные stencil с трапецеидальными apertures для стабильного отделения пасты.

- Reflow: оптимизируйте зону soak. Если flux выгорает слишком рано, окисление мешает нормальному смачиванию.

- Рентген-критерии: заранее задайте четкие границы pass/fail. Для IPC Class 2 обычно void должны быть меньше 25% площади шара.

3. Tombstoning

Этот дефект возникает, когда небольшой пассивный компонент поднимается на один вывод во время reflow.

- Первопричина: неравномерные силы смачивания, часто потому, что один pad подключен к большому полигону земли и работает как теплоотвод, а второй связан только с тонкой дорожкой.

- Профилактика (DFM): используйте thermal relief на pad земли, чтобы оба pad одновременно достигали температуры reflow.

4. Shadowing

При wave soldering или selective soldering крупные компоненты могут перекрывать доступ волны припоя к более мелким компонентам позади них.

- Профилактика (DFM): задавайте правила расстояний с учетом направления движения платы через установку пайки.

Валидация и приемка: испытания и критерии прохождения

| Test / Check | Method | Pass criteria (example) | Evidence |

|---|---|---|---|

| Электрическая непрерывность | Flying probe / fixture | Проверено 100% net, отсутствуют opens и shorts | E-test report |

| Критические размеры | Измерение | Соответствует допускам чертежа | Протокол инспекции |

| Целостность металлизации / заполнения | Микрошлиф | Нет void и трещин за пределами IPC-лимитов | Фото микрошлифа |

| Паяемость | Тест смачивания | Приемлемое смачивание, без dewetting | Отчет по паяемости |

| Warpage | Измерение плоскостности | В пределах спецификации, например ≤0.75% | Запись по warpage |

| Функциональная валидация | FCT | Все сценарии пройдены, лог сохранен | Логи FCT |

Как доказать, что DFM и DFT сработали? Нужно заранее выстроить план валидации, связанный с целями по NPI assembly.

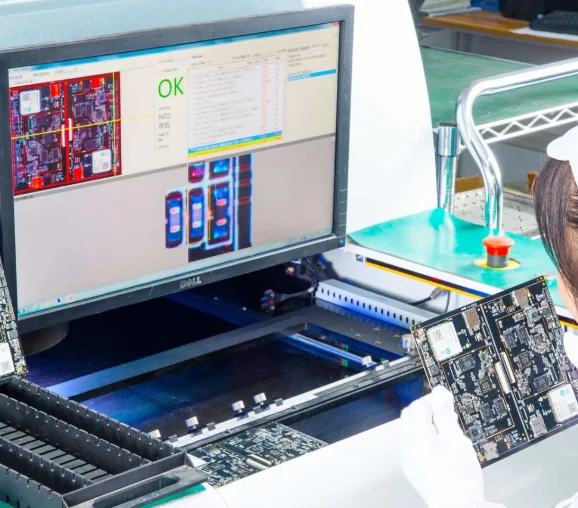

Automated Optical Inspection (AOI)

AOI является первой линией защиты. Камеры проверяют наличие компонентов, полярность, смещение и качество пайки.

- Критерии прохождения: отсутствуют пропущенные компоненты, метки полярности совпадают, паяные мениски соответствуют IPC.

- Ограничение: AOI не видит под BGA и QFN.

X-Ray Inspection (Axi)

Рентген-контроль необходим для валидации BGA и QFN.

- Критерии прохождения: должны соблюдаться требования bga voiding control: stencil, reflow, and x-ray criteria. Void <25%, форма шаров стабильная, перемычек нет.

- Применение: 100% контроль для прототипов и выборочный контроль для серийного производства.

- Подробнее: Рентген-инспекция

In-Circuit Test (ICT) и Flying Probe

Именно здесь DFT дает наибольшую отдачу.

- ICT: использует fixture типа bed of nails для одновременной проверки всех net. Это быстро, но дорого по оснастке. Поэтому test point должны быть предусмотрены заранее на этапе DFT.

- Flying Probe: роботизированные щупы проверяют точки без fixture. Метод медленнее, но отлично подходит для прототипов.

- Критерии прохождения: все пассивные значения находятся в допуске, на активных net отсутствуют shorts и opens.

Functional Circuit Test (FCT)

Это финальный этап валидации. Плата подается под питание и должна выполнять свою реальную функцию.

- Критерии прохождения: устройство запускается, firmware загружается, порты I/O корректно отвечают.

Чек-лист квалификации поставщика: RFQ, аудит и прослеживаемость

Если вы выбираете партнера, который поможет снизить дефекты PCBA с помощью DFM и DFT, используйте этот чек-лист.

1. Инженерные компетенции

- Выполняет ли поставщик обязательный DFM-review до запуска tooling?

- Выдает ли он подробный DFM-report, а не только pass/fail, с указанием таких рисков, как acid trap или sliver?

- Может ли он предложить альтернативные footprint для повышения выхода годных?

- Сверьтесь с Рекомендациями по DFM и ожидаемым уровнем проработки.

2. Управление процессом

- Есть ли inline SPI? SPI предотвращает значительную долю дефектов пасты и пайки.

- Есть ли рентген-контроль внутри собственного производства?

- Умеет ли поставщик уверенно применять qfn reflow best practices to reduce voids, например через vacuum reflow или настройку профиля?

3. Прослеживаемость и система качества

- Сертифицировано ли производство по ISO 9001 или IATF 16949?

- Доступна ли прослеживаемость на уровне компонентов с привязкой конкретных партий к конкретным серийным номерам?

- Изучите их Систему качества.

Как выбрать нужный уровень DFM и DFT: компромиссы и правила принятия решения

Не каждой плате требуется одинаковая глубина DFM и DFT. Ниже приведены ориентиры, которые помогают сбалансировать стоимость и риск.

Сценарий A: простая потребительская электроника, низкая себестоимость и большой объем

- Стратегия: сделать упор на DFM, чтобы поднять выход годных и сократить takt time.

- DFT: минимальный. Опора на AOI и функциональный выборочный контроль.

- Компромисс: допускается немного более высокий уровень отказов в поле ради низкой цены за единицу.

Сценарий B: медицинская и автомобильная электроника, высокая надежность и средний объем

- Стратегия: агрессивный DFM и DFT.

- DFT: 100% ICT и 100% функциональный тест.

- Компромисс: более высокие NRE-затраты на fixture и программирование теста, но практически нулевые отказы в поле.

- Специфика: строгое соблюдение bga voiding control: stencil, reflow, and x-ray criteria.

Сценарий C: быстрое прототипирование

- Стратегия: "мягкий" DFM. Исправляются только showstopper, мешающие сборке.

- DFT: flying probe без затрат на fixture.

- Компромисс: больше времени на тест одной платы, но быстрее общее выполнение заказа.

FAQ: стоимость, сроки, DFM-файлы, материалы и тестирование

1. Увеличивают ли требования DFM/DFT цену предложения? Да, на старте. Инженерная проработка и test fixture как NRE повышают начальную стоимость. Но часто общая стоимость проекта снижается за счет лучшего выхода годных и меньшего объема переделок.

2. Насколько DFM-review увеличивает срок изготовления? Обычно на 1-2 дня. Полноценный DFM-review выполняется до заказа материалов. Такая небольшая задержка позволяет избежать недель потерь позже, когда вскроется, что плату трудно или невозможно собрать.

3. Может ли DFM исправить плохую электрическую схему? Нет. DFM гарантирует, что плату можно изготовить и собрать, но не гарантирует правильную работу схемы. Если в схеме есть логические ошибки, плата будет произведена корректно и все равно не пройдет функционально.

4. В чем разница между DFM и DFA? DFM обычно относится к производимости печатной платы, например травлению и сверлению. DFA относится к сборке компонентов, включая пайку и зазоры. На практике DFM часто используют как общий термин для обеих областей.

5. Нужен ли ICT, если уже есть функциональный тест? В идеале да. ICT показывает, какой именно компонент или какая net неисправна. Функциональный тест чаще всего показывает только факт отказа платы. Для ремонта и диагностики ICT значительно эффективнее.

6. Как материалы влияют на DFM? Выбор материала, например High Tg FR4, определяет, как плата расширяется при reflow. Несовпадение CTE между компонентом и платой является частой причиной усталости паяных соединений.

7. Как лучше всего передавать DFM-примечания? Добавьте файл Read Me или PDF в архив Gerber. Явно перечислите специальные требования вроде "Do not X-out arrays" или "Mask plug vias at U1".

Запрос коммерческого предложения или DFM-review: что отправить

Если вы хотите оптимизировать PCBA под массовое производство, отправьте свой data package для полной DFM-проверки.

Чек-лист для запроса предложения:

- Gerber-файлы (RS-274X): медные слои, solder mask, шелкография, данные сверления и слои пасты.

- Bill of Materials (BOM): Excel-файл с Manufacturer Part Numbers (MPN) и reference designator.

- Centroid file (Pick and Place): координаты X-Y и данные по ориентации.

- Assembly drawings: PDF со схемой расположения компонентов и метками полярности.

- Требования к тесту: описание желаемого покрытия тестированием, например ICT, FCT или burn-in.

Глоссарий: ключевые термины

| Term | Meaning | Why it matters in practice |

|---|---|---|

| DFM | Design for Manufacturability: правила layout для снижения дефектов. | Снижает переделки, задержки и скрытые затраты. |

| AOI | Automated Optical Inspection для поиска дефектов пайки и сборки. | Повышает покрытие и рано выявляет отклонения. |

| ICT | In-Circuit Test для проверки opens, shorts и электрических значений. | Быстрый структурный тест для серийного производства. |

| FCT | Functional Circuit Test с подачей питания и проверкой поведения платы. | Подтверждает реальную работу под нагрузкой. |

| Flying Probe | Электрический тест без fixture с подвижными щупами. | Подходит для прототипов и малых или средних объемов. |

| Netlist | Описание электрической связности для сравнения design и изготовленного PCB. | Позволяет найти opens и shorts до сборки. |

| Stackup | Конструкция слоев с core, prepreg, медью и толщинами. | Влияет на impedance, warpage и надежность. |

| Impedance | Контролируемое поведение трасс для RF и high-speed сигналов, например 50Ω. | Помогает избежать отражений и проблем целостности сигнала. |

| ENIG | Финишное покрытие Electroless Nickel Immersion Gold. | Дает хороший баланс паяемости и планарности; важен контроль толщины никеля. |

| OSP | Organic Solderability Preservative как поверхностное покрытие. | Недорого, но чувствительно к обращению и многократному reflow. |

Заключение: следующие шаги

Понимание того, как снижать дефекты PCBA с помощью DFM и DFT, это инвестиция в срок службы изделия и в репутацию бренда. Если заранее определить требования к stencil, профилям reflow и доступности тестирования, производственный процесс перестает быть черным ящиком и становится управляемым и предсказуемым.

Подключайте производственного партнера уже на ранней стадии проектирования. Совместная проработка qfn reflow best practices to reduce voids и bga voiding control: stencil, reflow, and x-ray criteria экономит и время, и бюджет. Делайте data package прозрачным, проверяйте результат строгой валидацией и выбирайте поставщика, который рассматривает качество как общую ответственность.