Прототип объединительной платы PCIe Gen6: определение, область применения и для кого предназначен этот руководство

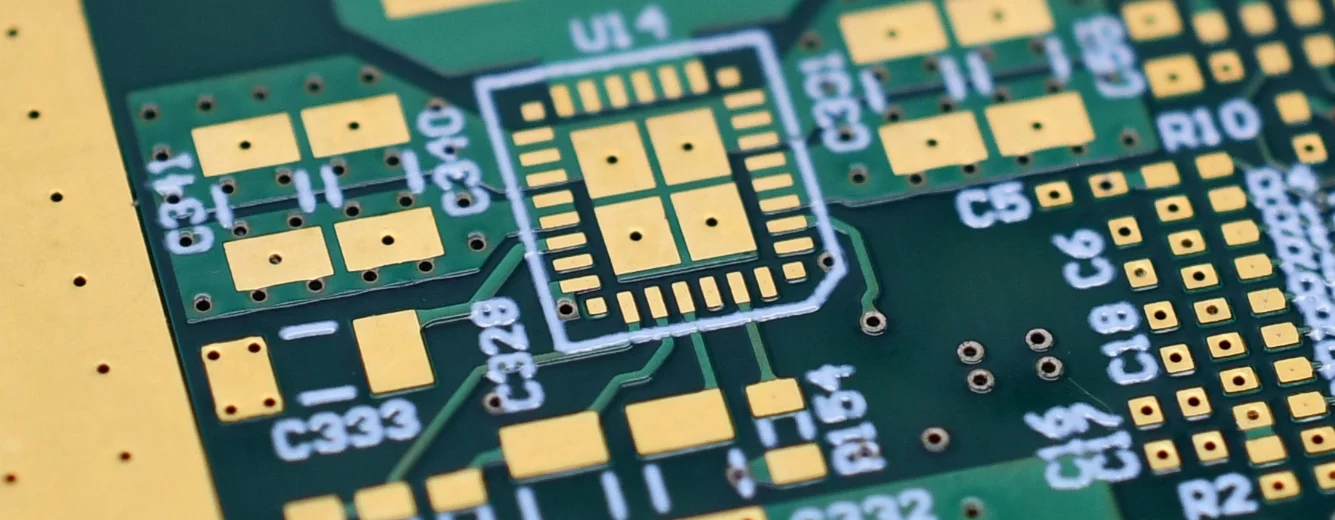

Прототип объединительной платы PCIe Gen6 представляет собой физическую проверку архитектуры высокоскоростных межсоединений, разработанной для поддержки скоростей передачи данных 64 ГТ/с с использованием сигнализации PAM4. В отличие от стандартных печатных плат, эти объединительные платы действуют как центральная нервная система для серверов, массивов хранения данных и сетевого оборудования, часто требуя большого количества слоев (20+), материалов со сверхнизкими потерями и точного обратного сверления для устранения сигнальных заглушек. Переход от моделирования к физическому прототипу является наиболее критическим этапом в разработке аппаратного обеспечения, поскольку он подтверждает, соответствуют ли модели целостности сигнала (SI) реальной производственной среде.

Это руководство написано для аппаратных архитекторов, инженеров по целостности сигнала и руководителей отдела закупок, которым поручено приобретение этих сложных плат. Оно выходит за рамки базовых определений, предлагая структурированный подход к спецификации, снижению рисков и проверке поставщиков. Цель состоит в том, чтобы помочь вам ориентироваться в жестких допусках, необходимых для сигнализации PAM4, и гарантировать, что ваш первый запуск прототипов даст функциональные платы, которые можно будет надежно протестировать. В APTPCB (Завод печатных плат APTPCB) мы понимаем, что прототип — это не просто образец; это доказательство инженерной компетентности. Это руководство объединяет лучшие практики, чтобы помочь вам минимизировать циклы итераций и избежать распространенных ошибок, связанных с высокоскоростной обработкой материалов и многослойным ламинированием.

Когда использовать прототип объединительной платы PCIe Gen6 (и когда стандартный подход лучше)

Понимание масштаба вашего проекта — это первый шаг; знание того, когда стоит вкладываться в стоимость и сложность сборки Gen6, — второй.

Разверните прототип объединительной платы PCIe Gen6, когда:

- Пропускная способность не подлежит обсуждению: Архитектура вашей системы требует 64 ГТ/с на линию для поддержки кластеров ИИ/МО, высокочастотных торговых платформ или коммутаторов центров обработки данных следующего поколения.

- Требуется сигнализация PAM4: Вы отходите от кодирования NRZ (Non-Return-to-Zero). PAM4 вводит четыре уровня напряжения, значительно уменьшая запас по шуму и требуя более строгого контроля импеданса, чем Gen5.

- Модульные конструкции с заделом на будущее: Вы разрабатываете шасси, предназначенное для нескольких поколений оборудования, требующее от объединительной платы поддержки текущих карт Gen5 и готовности к обновлениям Gen6.

- Сложная топология: Конструкция включает длинные трассы (до 20 дюймов), где вносимые потери становятся основным узким местом, что требует использования передовых материалов и посадочных мест для разъемов.

Придерживайтесь стандартных объединительных плат Gen4/Gen5, когда:

- Стоимость является основным фактором: Материалы, необходимые для Gen6 (например, Megtron 7/8, Tachyon), значительно дороже стандартных FR4 или ламинатов со средними потерями.

- Совместимость с устаревшими системами: Система взаимодействует только со старыми периферийными устройствами, которые не требуют четкости сигнала PAM4.

- Короткие длины трасс: Если путь сигнала очень короткий, преимущества материалов со сверхнизкими потерями могут быть незначительными по сравнению со стоимостью.

Спецификации прототипа объединительной платы PCIe Gen6 (материалы, стек, допуски)

Как только вы определили, что решение Gen6 необходимо, вы должны определить жесткие спецификации, чтобы гарантировать, что производитель сможет соответствовать требованиям к целостности сигнала.

- Базовый материал (ламинат): Должны использоваться материалы со сверхнизкими потерями. Распространенные варианты включают Panasonic Megtron 7 (или 8), Isola Tachyon 100G или серию Rogers RO4000 для гибридных стеков.

- Целевой Df (коэффициент рассеяния): < 0,002 @ 10 ГГц.

- Целевой Dk (диэлектрическая проницаемость): Стабилен по частоте (3,0 – 3,4).

- Шероховатость медной фольги: Медь HVLP (Hyper Very Low Profile) или VLP2 является обязательной.

- Причина: На частоте 32 ГГц (Найквист для 64 ГТ/с) доминирует скин-эффект. Шероховатая медь значительно увеличивает потери в проводнике.

- Количество слоев и толщина: Обычно от 20 до 40 слоев.

- Толщина платы: Часто варьируется от 3,0 мм до 6,0 мм (0,120" до 0,240").

- Соотношение сторон: Высокие соотношения сторон (до 20:1 или 25:1) для металлизированных сквозных отверстий (PTH).

- Контроль импеданса:

- Дифференциальный импеданс: 85Ω или 100Ω (в зависимости от архитектуры).

- Допуск: Строже стандартного; стремитесь к ±5% или ±7% вместо стандартных ±10%.

- Обратное сверление (сверление контролируемой глубины): Обязательно для всех высокоскоростных заглушек переходных отверстий.

- Длина заглушки: Должна быть < 6-8 мил (0,15 мм - 0,20 мм) для предотвращения проблем с резонансом.

- Диаметр обратного сверления: Обычно диаметр сверла + 8 мил зазора.

- Поверхностное покрытие: Иммерсионное серебро или ENIG (химическое никелирование с иммерсионным золочением).

- Предпочтение: Иммерсионное серебро часто предпочтительнее для меньших потерь на вносимое затухание, хотя ENIG распространен для срока хранения.

- Технология переходных отверстий:

- Использование глухих и скрытых переходных отверстий распространено, но увеличивает стоимость.

- Отверстия для разъемов с запрессовкой должны соответствовать строгим допускам на размер готового отверстия (обычно ±0,05 мм).

- Стиль плетения стекловолокна: Требуется стекловолокно с распределенным плетением (например, 1067, 1078, 1086) для уменьшения эффекта плетения волокон (FWE), который вызывает перекос между дифференциальными парами.

- Допуск на совмещение: Совмещение слоев должно быть точным (±3-5 мил), чтобы обратное сверление не повредило внутренние дорожки.

- Чистота: Уровни ионного загрязнения должны строго контролироваться для предотвращения электрохимической миграции (ECM) в высоковольтных средах центров обработки данных.

Риски производства прототипов печатных плат объединительных панелей PCIe Gen6 (первопричины и предотвращение)

Определение спецификаций — это только полдела; понимание того, где производственный процесс обычно дает сбои, позволяет предотвратить отказы.

Перекос сигнала из-за эффекта переплетения волокон

- Основная причина: Трассы дифференциальных пар, идущие параллельно пучкам стекловолокна; одна ветвь проходит по стеклу, другая по смоле.

- Обнаружение: Массивный джиттер, наблюдаемый в глазковых диаграммах во время тестирования.

- Предотвращение: Укажите стили «расширенного стекла» или поверните дизайн на панели (поворот на 10 градусов), чтобы усреднить диэлектрическую проницаемость.

Ошибки глубины обратного сверления (остатки шлейфов или обрезанные трассы)

- Основная причина: Изменение толщины платы или точности оси Z сверлильного станка.

- Обнаружение: TDR (рефлектометрия во временной области) показывает неожиданные провалы импеданса; обрывы цепи, если просверлено слишком глубоко.

- Предотвращение: Используйте сверление «контролируемой глубины» с электрическим зондированием; убедитесь, что производитель добавляет специальные «стоп-слои» или медные площадки для обнаружения сверлом.

Трещины в бочке металлизированного сквозного отверстия (PTH)

- Основная причина: Высокое соотношение сторон (толстая плата, маленькое отверстие) в сочетании с несоответствием теплового расширения во время оплавления.

- Обнаружение: Периодические сбои во время термоциклирования или IST-тестирования.

- Предотвращение: Убедитесь, что толщина медного покрытия в отверстиях достаточна (в среднем 25 мкм, мин. 20 мкм); используйте материалы с высоким Tg и низким КТР по оси Z.

Отклонения импеданса из-за коэффициента травления

- Причина: Трапециевидная форма дорожек после травления (верхняя ширина < нижняя ширина) влияет на импеданс.

- Обнаружение: Анализ поперечного сечения или тестирование образцов не соответствует спецификациям импеданса.

- Предотвращение: Производитель должен выполнять точную компенсацию травления на топологии; проверка DFM должна подтверждать корректировки ширины дорожек.

Кратеризация контактных площадок под разъемами с запрессовкой

- Причина: Механическое напряжение при установке разъема повреждает смолу под медной контактной площадкой.

- Обнаружение: Тестирование методом "краситель и отрыв" (dye and pry) или микрошлифовка.

- Предотвращение: Использовать "каплевидные" формы (teardrops) на контактных площадках; убедиться, что смола полностью отверждена; строго следовать спецификациям запрессовки производителя разъема.

Несоосность внутренних слоев

- Причина: Движение материала (масштабирование) во время ламинирования более 30 слоев.

- Обнаружение: Рентгеновский контроль показывает несоосность; короткие замыкания или обрывы в крайних случаях.

- Предотвращение: Использовать методы штифтового ламинирования; производитель должен применять коэффициенты масштабирования на основе данных о поведении материала.

Рост проводящих анодных нитей (CAF)

- Причина: Электрохимическая миграция вдоль стекловолокон между переходными отверстиями.

- Обнаружение: Испытание сопротивления изоляции высоким напряжением.

- Предотвращение: Использовать CAF-устойчивые материалы; поддерживать достаточный зазор между стенками переходных отверстий (шаг 0,8 мм - 1,0 мм требует тщательного планирования).

Недостаток смолы

- Первопричина: Толстые слои меди (силовые плоскости) препятствуют затеканию смолы в зоны зазора во время ламинирования.

- Обнаружение: Визуальные пустоты или расслоение в поперечных сечениях.

- Предотвращение: Сбалансировать распределение меди; при необходимости использовать высокотекучие препреги.

Валидация и приемка прототипа объединительной платы PCIe Gen6 (тесты и критерии прохождения)

Чтобы убедиться, что ваш прототип объединительной платы PCIe Gen6 готов к сборке и системной интеграции, требуется строгий план валидации.

- Измерение импеданса (TDR):

- Цель: Проверить соответствие дифференциального импеданса целевым значениям 85Ω/100Ω.

- Метод: Рефлектометрия во временной области на тестовых купонах и реальных трассах платы.

- Приемка: Все протестированные линии в пределах допуска ±5% (или согласованных ±7%).

- Измерение вносимых потерь (VNA):

- Цель: Подтвердить, что потери сигнала на дюйм соответствуют бюджету потерь для Gen6.

- Метод: Измерение векторным анализатором цепей до 32 ГГц.

- Приемка: Кривая потерь соответствует симуляции (например, < 1,0 дБ/дюйм при 16 ГГц) в пределах 10%.

- Анализ поперечного сечения (Микрошлифовка):

- Цель: Проверить конструкцию стека, толщину покрытия и выравнивание сверления.

- Метод: Разрушающий физический анализ купона или бракованной платы.

- Приемка: Толщина меди > 20 мкм в отверстиях; отсутствие трещин; толщина диэлектрика соответствует стеку.

- Проверка обратного сверления:

- Цель: Убедиться, что заглушки удалены без повреждения внутренних соединений.

- Метод: Рентгеновский контроль или микрошлифовка обратных отверстий (backdrilled vias).

- Приемлемость: Длина заглушки < 8 мил; сохранено минимальное изоляционное расстояние до внутренних слоев.

- Тест на стресс межсоединений (IST) или HATS:

- Цель: Проверить надежность переходных отверстий при термическом воздействии.

- Метод: Термическое циклирование (например, имитация оплавления при 260°C) с последующим контролем сопротивления.

- Приемлемость: Изменение сопротивления < 10% после 6 имитированных циклов оплавления.

- Проверка допуска отверстий для запрессовки (Press-Fit):

- Цель: Убедиться, что контакты разъема надежно входят, не повреждая плату.

- Метод: Калибр-пробка или координатно-измерительная машина (КИМ).

- Приемлемость: Размер готового отверстия в пределах ±0,05 мм от спецификации.

- Тест на паяемость:

- Цель: Убедиться, что поверхностное покрытие правильно принимает припой.

- Метод: Тест баланса смачивания IPC-J-STD-003.

- Приемлемость: > 95% покрытия; отсутствие десмачивания.

- Измерение изгиба и скручивания:

- Цель: Обеспечить плоскостность платы для сборки и установки в корпус.

- Метод: Измерение на поверочной плите.

- Приемлемость: < 0,75% (или < 0,5% для строгих требований) по диагонали.

Контрольный список квалификации поставщика прототипов объединительных плат PCIe Gen6 (RFQ, аудит, отслеживаемость)

При выборе партнера для прототипа объединительной платы PCIe Gen6, общих возможностей недостаточно. Используйте этот контрольный список для проверки поставщиков, специализирующихся на высокоскоростных работах с большим количеством слоев.

Группа 1: Входные данные для запроса предложений (Что вы должны предоставить)

- Полные файлы Gerber (RS-274X или X2) или ODB++.

- Подробный чертеж стека (с указанием типов материалов по названию, а не просто "FR4").

- Таблица сверления, различающая PTH, NPTH и обратное сверление (Backdrills).

- Таблица контроля импеданса (Слой, Ширина дорожки, Расстояние, Опорная плоскость).

- Сетевой список (IPC-356) для верификации электрических испытаний.

- Производственный чертеж с примечаниями о требованиях и допусках Класса 3.

- Спецификации для запрессовываемых разъемов (требования к размеру отверстий).

- Требования к панелизации (если сборка автоматизирована).

Группа 2: Подтверждение возможностей (Что они должны продемонстрировать)

- Опыт работы с материалами Megtron 7/8 или Tachyon (запросите примеры прошлых проектов).

- Способность обрабатывать соотношения сторон > 20:1.

- Автоматическое оборудование для обратного сверления с технологией определения глубины.

- Ламинационные прессы, способные работать с высоким давлением/вакуумом для >30 слоев.

- Внутреннее тестирование VNA/TDR до 40 ГГц.

- Возможность лазерного сверления для микропереходов (если используется HDI).

Группа 3: Система качества и прослеживаемость

- Квалификация IPC-6012 Класс 3.

- Сертификация UL для предложенного конкретного стека материалов.

- Автоматическая оптическая инспекция (АОИ) для внутренних слоев (100% контроль).

- Возможность рентгеновского контроля для проверки совмещения.

- Сертификаты соответствия материалов (CoC) от поставщика ламината.

- Протоколы калибровки для оборудования для тестирования импеданса.

Группа 4: Контроль изменений и доставка

- Формальный процесс заказа на изменение конструкции (ECO).

- Отчет DFM предоставляется до начала производства.

- Процесс EQ (инженерный запрос) для разрешения неоднозначностей данных.

- Безопасная обработка данных (защита ИС).

- Четкий график сроков выполнения, включая время закупки материалов.

- Стандарты упаковки (вакуумная упаковка с осушителем и индикатором влажности).

Как выбрать прототип объединительной платы PCIe Gen6 (компромиссы и правила принятия решений)

Каждое проектное решение включает в себя компромисс. Вот как ориентироваться в противоречивых ограничениях прототипа объединительной платы PCIe Gen6.

- Стоимость материала против потери сигнала:

- Правило: Если длина вашей трассы превышает 10 дюймов, выбирайте Megtron 7 или Tachyon, несмотря на стоимость.

- Компромисс: Если трассы < 5 дюймов, вы можете обойтись Megtron 6 или материалами со средними потерями, чтобы сэкономить 30% на стоимости ламината, но вы рискуете не пройти по запасам SI.

- Количество слоев против соотношения сторон:

- Правило: Если вам нужно больше слоев трассировки, вы должны увеличить толщину платы.

- Компромисс: Если толщина превышает 4 мм, убедитесь, что диаметр переходного отверстия достаточно велик, чтобы поддерживать соотношение сторон менее 20:1. Если вы используете маленькие переходные отверстия (0,2 мм) на толстой плате (5 мм), надежность металлизации будет нарушена.

- Обратное сверление (Backdrilling) против глухих переходных отверстий (Blind Vias):

- Правило: Используйте обратное сверление для стандартных контактов разъемов.

- Компромисс: Используйте глухие переходные отверстия только при экстремальной плотности. Глухие переходные отверстия значительно увеличивают циклы ламинирования и стоимость, тогда как обратное сверление — это механический процесс после ламинирования, который дешевле, но требует больших запретных зон.

- Покрытие поверхности: ENIG против иммерсионного серебра (Immersion Silver):

- Правило: Если потери на вносимое затухание являются абсолютным приоритетом, выберите иммерсионное серебро.

- Компромисс: Если платы будут храниться в течение нескольких месяцев перед сборкой, выберите ENIG для лучшей стойкости к окислению, принимая небольшой удар по потере сигнала из-за магнитных свойств никеля.

- Скорость прототипирования против качества DFM:

- Правило: Никогда не пропускайте проверку DFM, чтобы сэкономить 2 дня.

- Компромисс: "Быстрый оборот", который пропускает детальный инженерный обзор, часто приводит к бракованной плате из-за упущенных проблем с импедансом или регистрацией. Всегда выделяйте 2-3 дня на EQ (инженерные вопросы).

Часто задаваемые вопросы о прототипе объединительной платы PCIe Gen6 (стоимость, сроки, файлы DFM, материалы, тестирование)

В: Что является основным фактором стоимости прототипа объединительной платы PCIe Gen6? A: Основными факторами являются базовый ламинатный материал (например, Megtron 7) и количество слоев. Высокоскоростные материалы могут стоить в 3-5 раз дороже стандартного FR4, а большое количество слоев увеличивает трудозатраты на ламинирование и риск брака.

Q: Каков типичный срок выполнения для прототипа объединительной платы PCIe Gen6? A: Стандартный срок выполнения составляет 15-20 рабочих дней. Однако, если конкретный высокоскоростной материал отсутствует на складе, закупка может добавить 2-4 недели; всегда проверяйте наличие материала на складе на этапе коммерческого предложения.

Q: Какие DFM-файлы критически важны для производства прототипа объединительной платы PCIe Gen6? A: Помимо файлов Gerber, критически важны нетлист IPC-356 и подробный файл структуры слоев (с указанием диэлектрических постоянных). Без нетлиста производитель не сможет проверить соответствие готовой платы вашей электрической логике.

Q: Могу ли я использовать стандартный FR4 для прототипа объединительной платы PCIe Gen6, чтобы сэкономить деньги? A: Нет. Стандартный FR4 имеет слишком высокий тангенс угла диэлектрических потерь (Df) (0,020 против 0,002), что разрушит целостность сигнала PAM4 со скоростью 64 ГТ/с, делая прототип бесполезным для валидации.

Q: Как обратное сверление влияет на стоимость прототипа объединительной платы PCIe Gen6? A: Обратное сверление увеличивает стоимость платы примерно на 10-15% в зависимости от количества отверстий. Оно требует отдельной настройки ЧПУ и специализированного программирования контроля глубины.

Q: Каковы критерии приемки для тестирования импеданса этих прототипов? A: Большинство конструкций требуют допуск ±10%, но для Gen6 мы рекомендуем запрашивать ±5% или ±7%. Купоны TDR должны быть включены на направляющие панели для проведения испытаний без повреждения самой платы.

В: Нужно ли мне указывать "расширенное стекловолокно" (spread glass) для моего прототипа объединительной платы PCIe Gen6? О: Да. Стандартное тканое стекловолокно создает периодические зазоры, которые вызывают перекос (skew) в дифференциальных парах. Указание расширенного стекловолокна (например, 1067 или 1078) обеспечивает однородную диэлектрическую среду для сигналов.

В: Какие испытания проводятся для обеспечения надежности объединительной платы в эксплуатации? О: Помимо электрических испытаний, для прототипов рекомендуется проводить испытания на механическую прочность межсоединений (IST), чтобы убедиться, что переходные отверстия с высоким соотношением сторон могут выдерживать термические циклы без растрескивания стенок.

Ресурсы для прототипа объединительной платы PCIe Gen6 (связанные страницы и инструменты)

Чтобы дополнительно помочь вам в процессе проектирования и закупок, используйте эти конкретные ресурсы от APTPCB:

- Производство объединительных плат PCB: Подробное описание специфических возможностей, необходимых для крупноформатных объединительных плат с большим количеством слоев.

- Возможности высокоскоростных PCB: Узнайте о технологиях производства, используемых для сохранения целостности сигнала для приложений PCIe, Ethernet и DDR.

- Материалы Panasonic Megtron: Подробные спецификации семейства Megtron, промышленного стандарта для приложений Gen6.

- Калькулятор импеданса: Инструмент, который поможет вам оценить ширину и расстояние между дорожками для требуемых дифференциальных пар 85Ω или 100Ω.

- Рекомендации DFM: Основные правила проектирования, обеспечивающие возможность массового производства вашей сложной объединительной платы.

Запросить коммерческое предложение на прототип объединительной платы PCIe Gen6 (анализ DFM + ценообразование)

Готовы перейти от проектирования к аппаратному обеспечению? Отправьте свои данные для всестороннего анализа DFM и точного ценообразования. Для прототипа объединительной платы PCIe Gen6 приложите файлы Gerber, детали стека, таблицу сверления и любые специфические требования к импедансу.

Запросить коммерческое предложение и анализ DFM – Наша инженерная команда рассмотрит ваш стек и выбор материалов для обеспечения соответствия Gen6 до начала производства.

Заключение: Следующие шаги для прототипа объединительной платы PCIe Gen6

Успешная поставка прототипа объединительной платы PCIe Gen6 требует большего, чем просто отправка файлов на завод; это требует партнерства, ориентированного на материаловедение, прецизионное сверление и строгую проверку. Соблюдая строгие спецификации для материалов с низкими потерями и обратного сверления, а также активно управляя производственными рисками, такими как регистрация и перекос, вы гарантируете, что ваш прототип предоставит точные данные для проверки системы. APTPCB оснащена для решения этих сложностей, обеспечивая плавный и надежный переход от проектирования к физическому оборудованию.