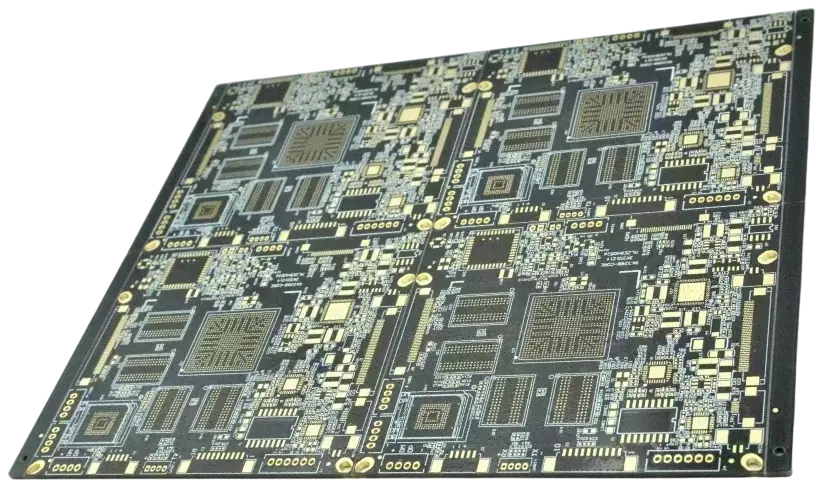

AI-Native PCB: definizione, ambito e a chi è destinata questa guida

Il termine AI-Native PCB si riferisce alle schede a circuito stampato ad alte prestazioni specificamente progettate per supportare gli ecosistemi hardware di Intelligenza Artificiale, inclusi server di addestramento, acceleratori di inferenza e nodi di edge computing. A differenza dell'elettronica standard, queste schede devono gestire simultaneamente un massiccio throughput di dati, carichi termici estremi e una latenza del segnale ultra-bassa. Poiché l'infrastruttura AI converge con le telecomunicazioni, i requisiti per queste schede spesso si sovrappongono a quelli delle infrastrutture ad alta frequenza come i moduli 5G AAU PCB (Unità Antenna Attiva) e 5G ADC PCB (Convertitore Analogico-Digitale), creando una complessa sfida di produzione che richiede una precisione superiore agli standard IPC Class 2.

Questo playbook è progettato per ingegneri hardware, responsabili NPI e responsabili degli acquisti che stanno passando dall'elettronica digitale standard all'hardware per il calcolo ad alte prestazioni (HPC). Taglia il rumore del marketing per concentrarsi sulle realtà fisiche della produzione: selezione dei materiali, integrità dello stackup e le specifiche fasi di validazione necessarie per prevenire guasti sul campo in costosi cluster AI. Presso APTPCB (APTPCB PCB Factory), abbiamo osservato che la causa principale dei ritardi di progetto in questo settore non è la capacità di progettazione, ma un disallineamento tra l'intento di progettazione e la realtà produttiva. Questa guida funge da quadro decisionale per colmare tale lacuna, garantendo che le vostre specifiche si traducano in hardware affidabile.

Quando utilizzare PCB AI-Native (e quando un approccio standard è migliore)

Comprendere l'ambito definito sopra ci permette di determinare esattamente quando il costo e la complessità di un PCB AI-Native sono giustificati rispetto a quando un design standard ad alta velocità è sufficiente.

Utilizzare un approccio AI-Native quando:

- Le velocità del segnale superano i 56 Gbps PAM4: Il FR4 standard non può supportare l'integrità del segnale richiesta per le moderne interconnessioni AI senza un'attenuazione massiccia.

- Il numero di strati supera i 18: Gli acceleratori AI spesso richiedono un routing ad alta densità e piani di alimentazione estesi che le presse di laminazione standard non possono allineare con precisione senza utensili specializzati.

- La densità termica è critica: Se la vostra GPU o TPU genera calore che richiede compatibilità con il raffreddamento a liquido o a immersione, i materiali standard del soldermask e del substrato potrebbero degradarsi.

- Integrazione con l'infrastruttura 5G: I progetti che incorporano la tecnologia 5G AAU PCB per l'AI edge richiedono capacità di segnale misto (RF + Digitale) che richiedono stackup ibridi.

Attenersi a PCB ad alta velocità standard quando:

- Dispositivi IoT Edge: L'inferenza semplice su microcontrollori (ad esempio, riconoscimento vocale) raramente richiede materiali esotici; il FR4 standard con impedenza controllata è solitamente sufficiente.

- Interfacce Legacy: Se la scheda gestisce principalmente PCIe Gen 3 o inferiore, il costo aggiuntivo per materiali a bassissima perdita di grado AI è inutile.

- Solo Prototipazione Logica: Se si sta convalidando la logica a basse velocità prima di scalare a piena velocità, i materiali standard possono far risparmiare costi significativi durante le prime revisioni.

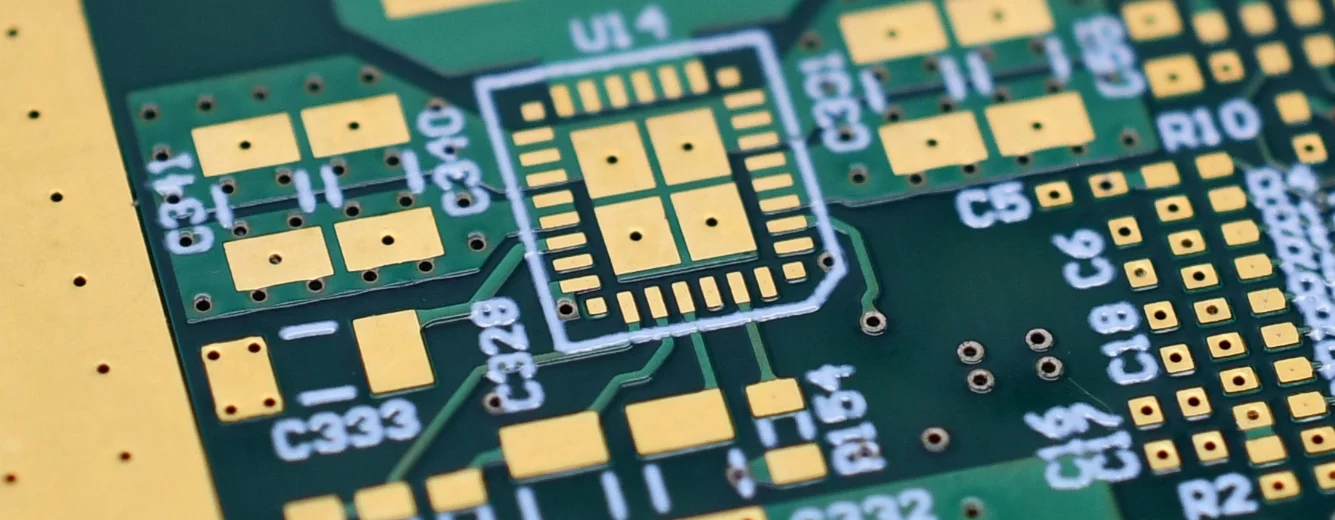

Specifiche PCB AI-Native (materiali, stackup, tolleranze)

Una volta determinato che il vostro progetto richiede un PCB AI-Native, il passo successivo è definire le specifiche rigide che governeranno il processo di produzione.

- Materiali di Base (Laminati):

- Requisito: I materiali a bassissima perdita sono non negoziabili.

- Obiettivo: Df (Fattore di Dissipazione) < 0,002 @ 10GHz; Dk (Costante Dielettrica) < 3,6.

- Esempi: Panasonic Megtron 7/8, Isola Tachyon 100G o serie Rogers RO3000 per sezioni RF ibride.

- Rugosità della Lamina di Rame:

- Requisito: Rame HVLP (Hyper Very Low Profile) o HVLP2.

- Obiettivo: Rugosità superficiale (Rz) < 1,5 µm per minimizzare le perdite per effetto pelle alle alte frequenze.

- Numero di Strati e Stackup:

- Intervallo: Tipicamente da 20 a 40+ strati per schede di grado server.

- Struttura: Cicli di laminazione multipli (3+); spesso richiede HDI (High Density Interconnect) "any-layer" o ELIC (Every Layer Interconnect).

- Foratura e Via:

- Retroforatura: Obbligatoria per gli strati di segnale ad alta velocità per rimuovere i monconi di via.

- Tolleranza: La tolleranza di profondità della retroforatura deve essere controllata entro ±0,05 mm a ±0,10 mm per preservare l'integrità del segnale senza tagliare gli strati interni.

- Rapporto d'aspetto: È richiesta una capacità di placcatura con elevato rapporto d'aspetto (da 15:1 a 20:1) per schede spesse (3,0 mm+).

- Controllo dell'impedenza:

- Tolleranza: Controllo rigoroso di ±5% o ±7% (lo standard è ±10%) su coppie single-ended e differenziali.

- Test: Test TDR (Time Domain Reflectometry) al 100% su coupon e schede di produzione.

- Finitura superficiale:

- Preferito: ENIG (Electroless Nickel Immersion Gold) o ENEPIG per il supporto del wire bonding.

- Alternativa: Argento ad immersione per una minore perdita di inserzione, sebbene la durata di conservazione sia più breve.

- Affidabilità termica:

- Tg (Temperatura di transizione vetrosa): > 180°C (Tg elevata).

- Td (Temperatura di decomposizione): > 350°C per resistere a più cicli di reflow durante l'assemblaggio di grandi componenti BGA.

- Precisione di registrazione:

- Obiettivo: Registrazione strato-strato entro ±2-3 mil (50-75µm) per garantire l'allineamento dei pad con i via in stack ad alto numero di strati.

- Pulizia:

- Contaminazione ionica: < 0,65µg/cm² equivalente NaCl, critica per prevenire la migrazione elettrochimica in ambienti di data center ad alta tensione.

Rischi di produzione di PCB AI-Native (cause profonde e prevenzione)

Con le specifiche bloccate, l'attenzione si sposta sulla mitigazione delle specifiche modalità di guasto associate alla produzione di progetti di PCB AI-Native ad alte prestazioni.

- Crescita di filamenti anodici conduttivi (CAF)

- Causa radice: Elevata polarizzazione di tensione tra vie ravvicinate combinata con l'assorbimento di umidità nel sistema di resina.

- Rilevamento: Test CAF (oltre 1000 ore ad alta temperatura/umidità).

- Prevenzione: Utilizzare materiali resistenti al CAF (tessuto di vetro spalmato) e massimizzare la spaziatura via-via dove possibile.

- Cratering del pad

- Causa radice: Materiali laminati fragili (comuni nei materiali ad alta velocità) si fratturano sotto lo stress meccanico dell'espansione termica dei grandi BGA.

- Rilevamento: Microscopia acustica o test dye-and-pry durante la validazione.

- Prevenzione: Utilizzare laminati rinforzati con resina e incollaggio angolare/sottoriempimento su grandi BGA.

- Perdita di integrità del segnale dovuta a variazione di incisione

- Causa radice: Sovra-incisione o sotto-incisione di tracce trapezoidali modifica il profilo di impedenza.

- Rilevamento: Analisi in sezione trasversale e test TDR.

- Prevenzione: Specificare i fattori di "compensazione dell'incisione" nell'ingegneria CAM e utilizzare apparecchiature di incisione sotto vuoto.

- Delaminazione durante il reflow

- Causa principale: L'umidità intrappolata nelle schede spesse vaporizza durante le temperature di rifusione senza piombo (260°C).

- Rilevamento: SAM (Microscopia Acustica a Scansione) dopo simulazione di rifusione.

- Prevenzione: Rigorosi protocolli di cottura (4-8 ore) prima dell'assemblaggio e imballaggio barriera contro l'umidità (MBB).

- Residui di stub di backdrill

- Causa principale: L'usura della punta del trapano o un errore di calcolo della profondità lascia un piccolo stub conduttivo.

- Rilevamento: Ispezione a raggi X o analisi TDR specifica alla ricerca di anomalie di riflessione.

- Prevenzione: Controlli ottici automatizzati delle punte del trapano e verifica a raggi X del primo articolo.

- Deformazione / Incurvamento e Torsione

- Causa principale: Distribuzione asimmetrica del rame o stackup sbilanciato in schede di grande formato.

- Rilevamento: Misurazione Shadow Moiré.

- Prevenzione: distribuzione del rame rigorosamente bilanciata su tutti gli strati; utilizzo di materiali a basso CTE.

- Vuoti di placcatura in via con elevato rapporto d'aspetto

- Causa principale: La soluzione di placcatura non circola efficacemente in fori profondi e stretti (ad esempio, scheda spessa 3 mm con via da 0,2 mm).

- Rilevamento: Sezionamento trasversale e test di shock termico.

- Prevenzione: Tecnologia di placcatura a impulsi e limiti di progettazione del rapporto d'aspetto (mantenere al di sotto di 15:1 se possibile).

- Discontinuità di impedenza alle transizioni di strato

- Causa principale: Disallineamento tra il pad del via e la distanza del piano di riferimento.

- Rilevamento: Test VNA (Analizzatore di Rete Vettoriale).

- Prevenzione: Imaging diretto laser (LDI) per gli strati interni per garantire un allineamento preciso.

Validazione e accettazione di PCB nativi AI (test e criteri di superamento)

Per garantire che i rischi sopra menzionati siano gestiti, è necessario eseguire un robusto piano di validazione prima della produzione di massa di qualsiasi PCB nativo AI.

- Test di stress dell'interconnessione (IST):

- Obiettivo: Verificare l'affidabilità dei via sotto cicli termici.

- Metodo: Sottoporre i coupon a cicli ripetuti da temperatura ambiente a 150°C (o superiore).

- Accettazione: Nessun aumento della resistenza > 10% dopo 500 cicli.

- Verifica dell'integrità del segnale (parametri S):

- Obiettivo: Confermare che la perdita di inserzione e la perdita di ritorno soddisfano i modelli di simulazione.

- Metodo: Misurazione VNA fino a 28GHz o 56GHz.

- Accettazione: Deviazione della perdita di inserzione < 1dB/pollice dalla simulazione; Perdita di ritorno < -15dB.

- Test Hipot (alto potenziale):

- Obiettivo: Garantire l'isolamento tra i rail di alimentazione ad alta tensione (comune nell'alimentazione dei server AI).

- Metodo: Applicare alta tensione (ad esempio, 500V-1000V) tra le reti.

- Accettazione: Corrente di dispersione < 1mA; nessun guasto.

- Test di shock termico:

- Obiettivo: Testare la forza di adesione del materiale e l'integrità della placcatura dei via.

- Metodo: Trasferimento liquido-liquido da -55°C a +125°C.

- Accettazione: Nessuna delaminazione, formazione di bolle o circuiti aperti dopo 100 cicli.

- Test di saldabilità:

- Obiettivo: Assicurarsi che la finitura superficiale accetti correttamente la saldatura.

- Metodo: IPC J-STD-003 (Dip and Look o Bilancia di bagnatura).

- Accettazione: > 95% di copertura; tempo di bagnatura < 2 secondi.

- Test di contaminazione ionica (ROSE):

- Obiettivo: Verificare la pulizia della scheda.

- Metodo: IPC-TM-650 2.3.25.

- Accettazione: < 1,56 µg/cm² equivalente NaCl (spesso più severo per l'IA: < 0,65).

- Resistenza alla pelatura del rame:

- Obiettivo: Verificare l'adesione del rame al dielettrico.

- Metodo: Test di pelatura meccanico.

- Accettazione: > 0,8 N/mm (o secondo le specifiche del datasheet del materiale).

- Stabilità dimensionale:

- Obiettivo: Assicurarsi che la scheda si adatti al telaio e si allinei con i socket.

- Metodo: CMM (Macchina di Misura a Coordinate).

- Accettazione: Tolleranze entro ±0,1 mm per il contorno; Deformazione < 0,75%.

Lista di controllo per la qualificazione dei fornitori di PCB AI-Native (RFQ, audit, tracciabilità)

Quando si seleziona un partner come APTPCB, utilizzare questa lista di controllo per assicurarsi che la fabbrica sia veramente in grado di gestire i requisiti dei PCB AI-Native piuttosto che solo la produzione standard.

Gruppo 1: Input RFQ (Cosa è necessario fornire)

- File Gerber X2 o ODB++ completi (preferiti per dati complessi).

- Netlist IPC-356 per la verifica del test elettrico.

- Disegno dettagliato dello stackup che specifica i tipi di materiale (marca/serie) e lo spessore dielettrico.

- Tabella di impedenza che fa riferimento a strati specifici e larghezze di traccia.

- Disegno di foratura che distingue tra fori passanti, via ciechi/interrati e backdrill.

- Disegno di fabbricazione con note sui requisiti di Classe 3 (se applicabile).

- Requisiti di panelizzazione (se l'assemblaggio richiede binari/fiducial specifici).

- File Readme che evidenzia le netlist critiche (es. "Non modificare il routing sulla Net X").

Gruppo 2: Prova di Capacità (Cosa il fornitore deve dimostrare)

- Elenco attrezzature: Macchine Laser Direct Imaging (LDI) per strati interni.

- Elenco attrezzature: Linee di incisione sottovuoto (per linee sottili < 3 mil).

- Elenco attrezzature: Macchine di backdrilling automatizzate con sensore di controllo della profondità.

- Esperienza: Casi di studio o campioni anonimi di schede a 20+ strati.

- Scorte di materiale: Prova di inventario o catena di fornitura diretta per materiali Megtron/Rogers.

- Capacità HDI: Capacità dimostrata per microvia impilati (es. 3+N+3).

Gruppo 3: Sistema Qualità & Tracciabilità

- Certificazioni: ISO 9001 (Generale), IATF 16949 (se AI automobilistica), UL 94V-0.

- Tracciabilità: Possono tracciare una scheda specifica fino al lotto di materia prima e al ciclo di pressatura di laminazione?

- IQC (Controllo Qualità in Ingresso): Procedura per la verifica delle proprietà del pre-preg e del materiale del nucleo.

- AOI (Ispezione Ottica Automatica): L'AOI viene eseguita su ogni strato interno?

- Sezionamento: Frequenza dell'analisi micro-sezionale per lotto di produzione.

Gruppo 4: Controllo delle Modifiche & Consegna

- Politica PCN (Product Change Notification): Impegno a notificare prima di cambiare materiali o sub-fornitori.

- Processo EQ (Engineering Question): Come gestiscono le discrepanze DFM (rapporto formale vs. e-mail).

- Imballaggio: Sacchetti barriera all'umidità (MBB) con schede indicatrici di umidità (HIC) e disidratante.

- Logistica: Esperienza nella spedizione internazionale di carichi pesanti in rame/di peso elevato.

Come scegliere PCB AI-Native (compromessi e regole decisionali)

Ogni decisione ingegneristica comporta un compromesso. Ecco come affrontare i conflitti più comuni quando si specificano architetture di PCB AI-Native.

- Costo del materiale vs. Integrità del segnale

- Regola: Se la lunghezza totale della traccia è breve (< 5 pollici) e la velocità è < 25 Gbps, è possibile utilizzare materiale "Mid-Loss" (ad esempio, Isola FR408HR).

- Regola: Se la lunghezza della traccia è lunga o la velocità è > 25 Gbps, è necessario scegliere materiale "Ultra-Low Loss" (ad esempio, Megtron 7). Il costo di attenuazione del segnale del FR4 richiederà costose riprogettazioni.

- HDI vs. Fori passanti

- Regola: Se si dispone di componenti BGA con passo < 0,65 mm, è necessario utilizzare HDI (Microvias).

- Regola: Se il passo BGA è > 0,8 mm, attenersi ai fori passanti o a semplici vie cieche per ridurre il costo della scheda del 30-50%.

- Backdrilling vs. Vie cieche

- Regola: Se è necessario rimuovere stub su una scheda spessa (3 mm+), il backdrilling è generalmente più conveniente della laminazione sequenziale (vie cieche) per una semplice rimozione di stub.

- Regola: Se è necessario spazio di routing sugli strati esterni sopra il via, utilizzare i via ciechi (Blind Vias).

- Finitura superficiale: ENIG vs. OSP

- Regola: Se l'affidabilità e la durata di conservazione sono fondamentali (Server/Data Center), scegliere ENIG.

- Regola: Se l'integrità del segnale a frequenze estremamente elevate (> 50GHz) è l'unica priorità, l'OSP (Organic Solderability Preservative) non ha uno strato di nichel che possa causare perdite magnetiche, ma l'assemblaggio deve avvenire immediatamente.

- Spessore della scheda vs. Rapporto d'aspetto

- Regola: Se la scheda deve essere spessa (per rigidità/strati), è necessario aumentare il diametro del via per mantenere un rapporto d'aspetto di placcatura < 15:1.

- Regola: Se la dimensione del via è fissa (piccola), è necessario ridurre lo spessore della scheda o accettare una maggiore perdita di resa/costo.

Domande frequenti (FAQ) sui PCB AI-Native (costo, tempi di consegna, file DFM, materiali, test)

D: Come si confronta il costo dei PCB AI-Native con i PCB standard? R: Aspettatevi costi da 3 a 10 volte superiori rispetto alle schede FR4 standard. Ciò è dovuto a materie prime costose (Megtron/Rogers possono costare 5 volte il costo dell'FR4), processi a bassa resa (HDI, backdrilling) e requisiti di test estesi.

D: Qual è il tempo di consegna tipico per i prototipi di PCB AI-Native? R: Il tempo di consegna standard è di 15-20 giorni lavorativi a causa dei cicli di laminazione sequenziali.

- Accelerato: Può essere ridotto a 10-12 giorni con costi aggiuntivi.

- Ritardo materiale: Controllare sempre la disponibilità di materiali esotici; l'ordinazione di materiali può aggiungere 2-4 settimane se non sono in stock. D: Quali file DFM specifici sono necessari per la modellazione dell'impedenza di PCB nativi AI? R: È necessario fornire un file di stackup che indichi esplicitamente la costante dielettrica (Dk) e il fattore di dissipazione (Df) alla frequenza operativa (ad esempio, 10 GHz), non solo il valore a 1 MHz trovato nelle schede tecniche generiche.

D: Possiamo mescolare materiali (stackup ibrido) per risparmiare sui costi? R: Sì, questo è comune nei progetti di PCB AAU 5G.

- Metodo: Utilizzare materiale ad alta frequenza costoso per gli strati di segnale e FR4 più economico per gli strati di alimentazione/massa/meccanici.

- Rischio: Il disallineamento del CTE tra i materiali può causare deformazioni; richiede un'attenta validazione ingegneristica.

D: Quali sono i criteri di accettazione per la profondità di retroforatura? R: Lo standard industriale è tipicamente "Non deve tagliare il rame dello strato target" e "Lunghezza dello stub residuo < 10 mil (0,25 mm)". Tolleranze più strette (ad esempio, < 6 mil) aumentano i costi e il rischio di circuiti aperti.

D: Come si testa l'affidabilità nelle sezioni PCB ADC 5G? R: Oltre al test E standard, raccomandiamo test specifici del rumore di fondo e test di intermodulazione passiva (PIM) se l'ADC è integrato con linee di trasmissione RF.

D: Perché il "thieving" o bilanciamento del rame è critico per queste schede? R: Le schede AI sono spesso grandi. Una distribuzione non uniforme del rame porta a "incurvamento e torsione" durante la rifusione, il che causa guasti ai giunti di saldatura BGA. Il bilanciamento automatico del rame viene aggiunto alle aree vuote per bilanciare lo stress.

D: Devo specificare IPC Classe 3 per l'hardware AI? R: Sebbene la classe IPC 2 sia standard, la maggior parte dei proprietari di infrastrutture AI specifica "IPC Classe 2 con requisiti di placcatura di Classe 3" (cioè rame più spesso nei via) per garantire affidabilità a lungo termine senza l'intero onere di costi/ispezioni della Classe 3.

Risorse per PCB nativi AI (pagine e strumenti correlati)

- Produzione di PCB ad alta velocità: Approfondimento sulle tecniche di produzione specifiche per l'integrità del segnale > 25 Gbps.

- PCB per server e data center: Comprendere gli standard di affidabilità specifici richiesti per ambienti operativi 24 ore su 24, 7 giorni su 7.

- Capacità PCB HDI: Scopri le strutture microvia e la laminazione sequenziale necessarie per i chip AI ad alta densità.

- Calcolatore di impedenza: Uno strumento per stimare la larghezza e la spaziatura delle tracce prima di inviare il tuo stackup finale.

- Materiali PCB Panasonic Megtron: Specifiche per il materiale a bassa perdita più comune utilizzato negli acceleratori AI.

- Linee guida DFM: Regole di progettazione essenziali per garantire che la tua scheda AI sia producibile su larga scala.

Richiedi un preventivo per PCB nativi AI (revisione DFM + prezzi)

Pronto a passare dalla progettazione alla validazione? Presso APTPCB, forniamo una revisione DFM completa insieme al tuo preventivo per identificare potenziali rischi di integrità del segnale o di stackup prima dell'inizio della produzione.

Per ottenere un preventivo e una DFM accurati, si prega di preparare:

- File Gerber/ODB++: Set di dati completo.

- Stackup e Impedenza: Numero di strati desiderato e impedenza target.

- Specifiche Materiali: Requisiti specifici del laminato (es. "Megtron 7 o equivalente").

- Volume: Quantità prototipo vs. Obiettivi di produzione di massa.

Clicca qui per richiedere un preventivo e una revisione DFM

Conclusionee: Prossimi passi per i PCB AI-Native

Il successo nel dispiegamento di un PCB AI-Native richiede un cambiamento di mentalità, passando dal "collegare componenti" al "progettare un sistema di linea di trasmissione". Definendo rigorosamente le specifiche dei materiali, comprendendo i rischi della costruzione a più strati e validando la capacità del fornitore di gestire il backdrilling e l'HDI, è possibile garantire la base hardware su cui si basano i vostri algoritmi di intelligenza artificiale. Che stiate costruendo un PCB 5G AAU o un cluster di addestramento massivo, la fisica della produzione rimane il guardiano ultimo delle prestazioni.