Portare un PCB con interfaccia CXL 3.0 alla produzione di massa richiede un passaggio rigoroso dai normali metodi di fabbricazione a processi di ultra precisione. Con velocità di 64 GT/s in segnalazione PAM4, il margine di errore su controllo d’impedenza, scelta dei materiali e tolleranze di foratura è praticamente nullo. Questa guida riassume i limiti numerici concreti, i controlli di processo e i passaggi di verifica necessari per ottenere alta resa e integrità del segnale nella produzione in volume.

Risposta rapida (30 secondi)

- Regola critica: Mantenere l’impedenza differenziale a 85 Ω ±5%; la tolleranza standard di ±10% non è sufficiente per la segnalazione PAM4 del CXL 3.0.

- Requisito materiale: Utilizzare materiali Ultra-Low Loss, ad esempio Megtron 7/8 o Tachyon 100G, con Df < 0,002 a 10 GHz.

- Errore chiave: Tratti residui dei via superiori a 6 mil (0,15 mm) generano risonanze fatali; la retroforatura è obbligatoria per backplane spessi.

- Verifica: Eseguire TDR al 100% sui provini di prova e campionamento casuale sulle schede reali per verificare l’attenuazione d’inserzione.

- Caso limite: Se la lunghezza della traccia supera 10 pollici, valutare rame a bassa rugosità (HVLP/VLP, Rz < 2 µm) per ridurre le perdite da effetto pelle.

- Voce DFM: Specificare una tolleranza di profondità di retroforatura di ±2 mil per rimuovere i tratti residui senza danneggiare gli strati interni attivi.

Punti salienti

- Sensibilità PAM4: CXL 3.0 utilizza modulazione di ampiezza d’impulso a 4 livelli, riducendo il rapporto segnale/rumore rispetto a NRZ.

- Precisione dell’impilamento: La registrazione tra strati deve rimanere entro 3 mil per evitare discontinuità di impedenza.

- Tecnologia di foratura: Vias con rapporto d’aspetto elevato, fino a 20:1, richiedono foratura meccanica avanzata o foratura laser.

- Finitura superficiale: ENIG o ENEPIG sono preferibili per la planarità; HASL è da escludere perché le superfici irregolari degradano i segnali ad alta frequenza.

- Pulizia: La contaminazione ionica deve essere controllata rigorosamente per prevenire la migrazione elettrochimica nei layout ad alta densità.

- Test: Spesso sono richieste misure VNA fino a 32 GHz per caratterizzare il canale.

Contenuto

- Definizione e ambito (che cos’è e che cosa non è)

- Regole e specifiche (parametri chiave e limiti)

- Passi di implementazione (checkpoint di processo)

- Risoluzione dei problemi (modalità di guasto e correzioni)

- Come scegliere (decisioni progettuali e compromessi)

- FAQ (costo, lead time, materiali, test, criteri di accettazione)

- Glossario (termini chiave)

- Richiedi un preventivo (revisione DFM + prezzo)

- Conclusione (passi successivi)

Definizione e ambito (che cos’è e che cosa non è)

Si applica quando:

- Si producono schede madri server, schede acceleratrici o moduli di espansione memoria compatibili con lo standard Compute Express Link (CXL) 3.0.

- Il progetto utilizza il physical layer PCIe 6.0 a 64 GT/s.

- L’impilamento PCB comprende da 12 a oltre 32 strati, spesso con HDI o strutture backplane spesse.

- I requisiti di integrità del segnale impongono laminati Ultra-Low Loss (ULL) e un controllo d’impedenza stretto.

- I volumi vanno da piccoli lotti pilota NPI fino alla piena fabbricazione PCB in serie.

Non si applica quando:

- Si progetta per CXL 1.0/1.1 o PCIe 4.0/5.0 a 32 GT/s NRZ, dove materiali Low Loss standard possono ancora bastare.

- La velocità d’interfaccia è sotto 16 GT/s e quindi sono tollerabili impedenze con ±10%.

- Si usa FR-4 standard con Tg 130-150 °C e Df > 0,015, troppo elevato per queste frequenze.

- La scheda è un semplice PCB consumer da 2 a 6 strati senza esigenze di impedenza controllata.

Regole e specifiche (parametri chiave e limiti)

Ottenere conformità CXL 3.0 in produzione di massa richiede rispetto rigoroso di parametri fisici ed elettrici. La tabella seguente riassume le regole di fabbricazione non negoziabili.

| Regola | Valore/intervallo consigliato | Perché conta | Come verificare | Se ignorata |

|---|---|---|---|---|

| Impedenza differenziale | 85 Ω ± 5% | La specifica CXL 3.0/PCIe 6.0 richiede 85 Ω per ridurre la perdita di ritorno. | TDR su provini di prova. | Le riflessioni aumentano il BER e provocano errori nell’addestramento del collegamento. |

| Perdita del materiale (Df) | < 0,002 a 10 GHz | L’attenuazione ad alta frequenza deve essere minimizzata per 64 GT/s. | Metodo IPC-TM-650 2.5.5.5 o certificato del datasheet materiale. | Una perdita d’inserzione eccessiva chiude l’occhio del segnale; il link non negozia la velocità. |

| Rugosità del rame | Rz < 2,0 µm (HVLP/VLP) | L’effetto pelle a 16-32 GHz spinge la corrente in superficie; il rame ruvido aumenta la perdita. | Analisi SEM della lamina. | Aumento di perdita d’inserzione e distorsione di fase. |

| Lunghezza del tratto residuo del via | < 6 mil (0,15 mm) | I tratti residui agiscono come antenne o filtri e creano buchi di risonanza nella risposta in frequenza. | Analisi in sezione o ispezione a raggi X. | Le risonanze a Nyquist distruggono l’integrità del segnale. |

| Skew intra-coppia | < 5 ps | I segnali differenziali devono arrivare simultaneamente per mantenere la reiezione del modo comune. | Misura VNA o simulazione del tempo di volo. | Conversione di modo e chiusura dell’occhio. |

| Tolleranza di profondità della retroforatura | ± 2 mil (0,05 mm) | Garantisce la rimozione del tratto residuo senza incidere lo strato interno attivo. | Ispezione a raggi X dei fori retroforati. | O resta troppo tratto residuo oppure si interrompe la traccia attiva. |

| Registrazione degli strati | ± 3 mil | Il disallineamento influisce sull’impedenza e può causare corti in aree BGA ad alta densità. | Verifica foratura a raggi X e microsezione. | Discontinuità di impedenza e potenziali cortocircuiti. |

| Ponte della solder mask | Min. 3 mil (0,075 mm) | Previene ponti di saldatura sulle footprint dei connettori CXL a passo fine. | AOI. | Ponti di saldatura in assemblaggio e cortocircuiti. |

| Rapporto d’aspetto del rivestimento | Max 20:1 | Assicura sufficiente spessore di rame nel barrel dei via profondi. | Analisi di microsezione. | Cracking del barrel in reflow e aperture intermittenti. |

Passi di implementazione (checkpoint di processo)

Trasferire un design CXL 3.0 in produzione di massa richiede controlli di processo precisi.

1. Selezione materiale e verifica

- Azione: Selezionare materiali come Panasonic Megtron 7/8, Isola Tachyon 100G o equivalenti.

- Controllo: Verificare lo stile di vetro del prepreg, per esempio 1035 o 1067, affinché il contenuto di resina riduca lo skew dovuto all’effetto della tessitura del vetro.

- Accettazione: Tolleranza Dk ±0,05; Df < 0,002.

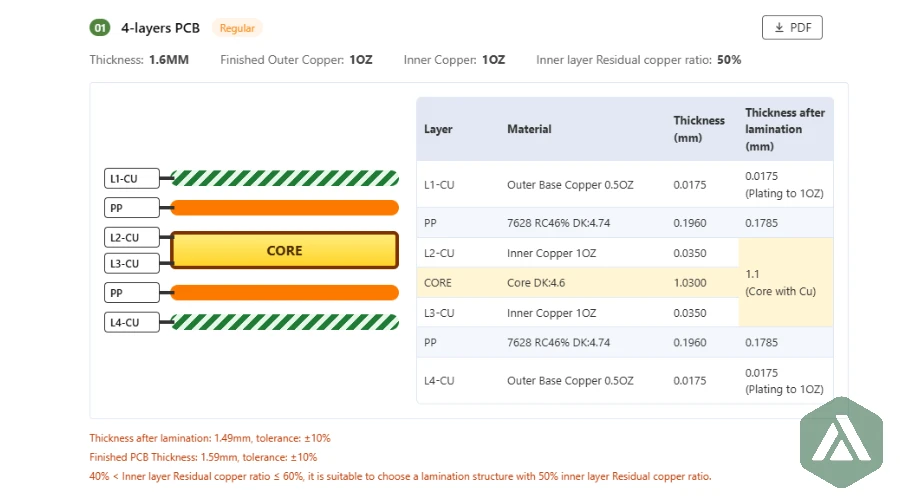

2. Impilamento e modellazione dell’impedenza

- Azione: Usare un risolutore di campo 2D/3D, ad esempio Polar SI9000, per calcolare la larghezza delle tracce.

- Controllo: Considerare il flusso della resina e lo spessore finale del rame pressato. Per CXL 3.0, le tracce da 85 Ω sono spesso leggermente più larghe delle normali tracce da 100 Ω.

- Accettazione: La simulazione deve rientrare entro ±1 Ω rispetto al target di 85 Ω prima dell’avvio produttivo. Vedere la nostra guida impilamento PCB.

3. Immagine degli strati interni e incisione

- Azione: Utilizzare Laser Direct Imaging (LDI) per alta precisione.

- Controllo: I fattori di compensazione d’incisione devono essere accurati. La tolleranza di larghezza traccia deve rimanere entro ±0,5 mil o meglio.

- Accettazione: L’AOI non deve mostrare restringimenti o sporgenze sulle linee ad alta velocità.

4. Laminazione e registrazione

- Azione: Utilizzare sistemi pin-lam o di allineamento ottico per conteggi elevati di strati, 20 e oltre.

- Controllo: Verificare con raggi X l’allineamento degli strati dopo la laminazione.

- Accettazione: Registrazione entro 3 mil da strato a strato per garantire che i via pad colpiscano centralmente gli strati target.

5. Foratura e retroforatura

- Azione: Forare i passanti e poi eseguire retroforatura a profondità controllata per rimuovere i tratti residui.

- Controllo: Monitorare la vita utensile delle punte per evitare rugosità sulle pareti del foro.

- Accettazione: La profondità di retroforatura deve rientrare in ±2 mil rispetto allo strato target.

6. Metallizzazione e finitura superficiale

- Azione: Applicare una deposizione di rame con elevato throw power per garantire integrità del barrel nei via con elevato rapporto d’aspetto.

- Controllo: Misurare lo spessore del rame al centro del barrel, minimo 0,8 mil cioè 20 µm.

- Accettazione: La finitura superficiale ENIG o ENEPIG deve essere piana per l’assemblaggio di connettori ad alta densità.

7. Test elettrici (TDR e VNA)

- Azione: Eseguire test di netlist al 100% e test TDR d’impedenza sui provini di prova.

- Controllo: Per CXL 3.0, una misura VNA a campione, ad esempio SET2DIL, serve a misurare la perdita d’inserzione per pollice.

- Accettazione: Impedenza 85 Ω ±5%; perdita entro budget, ad esempio -0,9 dB/pollice a 16 GHz.

Risoluzione dei problemi (modalità di guasto e correzioni)

Nell’assemblaggio di PCB con interfaccia CXL 3.0, i guasti si manifestano spesso come problemi di integrità del segnale invece che come semplici aperti o corti.

Sintomo 1: BER elevato o link instabile

- Causa probabile: Lunghezza eccessiva del tratto residuo del via, che genera risonanza.

- Controllo: Ispezionare a raggi X i via retroforati. Il tratto residuo supera 6 mil?

- Correzione: Regolare i parametri di profondità della retroforatura.

- Prevenzione: Specificare chiaramente gli strati da non intaccare nei dati ODB++ e aumentare la distanza di sicurezza della retroforatura.

Sintomo 2: impedenza costantemente bassa, per esempio 78 Ω invece di 85 Ω

- Causa probabile: La traccia è troppo larga oppure il dielettrico è più sottile del previsto.

- Controllo: Eseguire una sezione della scheda. Misurare larghezza reale della traccia, sopra e sotto, e altezza del dielettrico.

- Correzione: Regolare i fattori di compensazione di incisione per il lotto successivo.

- Prevenzione: Effettuare una microsezione sul primo articolo prima di lanciare l’intero lotto di serie.

Sintomo 3: chiusura verticale del diagramma a occhio

- Causa probabile: Alta perdita d’inserzione dovuta al materiale o alla rugosità del rame.

- Controllo: Verificare il lotto materiale, per esempio se si tratta davvero di Megtron 7. Controllare anche la rugosità della lamina di rame, cioè se è HVLP.

- Correzione: Passare a una lamina di rame più liscia o a un materiale meno dissipativo.

- Prevenzione: Richiedere certificati materiale (CoC) a ogni spedizione.

Sintomo 4: jitter indotto da skew

- Causa probabile: Effetto della tessitura del vetro, quando i fasci di vetro si allineano alle tracce.

- Controllo: Verificare lo stile di vetro usato, per esempio 106, 1080 o 1035.

- Correzione: Ruotare il progetto di 10° con instradamento a zigzag oppure usare vetro steso.

- Prevenzione: Specificare FR4 con vetro steso o stili di vetro equivalenti di fascia alta nelle note di fabbricazione.

Sintomo 5: pad cratering BGA o pad sollevati

- Causa probabile: Laminato fragile combinato con stress meccanico.

- Controllo: Verificare Tg e CTE del materiale.

- Correzione: Usare materiali con CTE più basso sull’asse Z o migliorare la tenacità della resina.

- Prevenzione: Ottimizzare il profilo di reflow per BGA/QFN fine pitch così da ridurre lo shock termico.

Come scegliere (decisioni progettuali e compromessi)

Prendere le decisioni corrette già in fase di progetto riduce i costi e migliora la resa nella fabbricazione PCB in serie.

Se la lunghezza della traccia è inferiore a 5 pollici:

- Scegliere: Materiali a perdita intermedia, come Megtron 6 o IT-968, possono bastare se il budget di perdita lo consente.

- Compromesso: Riduce il costo materiale ma lascia meno margine.

Se la lunghezza della traccia supera 10 pollici:

- Scegliere: Materiali Ultra-Low Loss come Megtron 7/8 o Tachyon 100G e rame HVLP.

- Compromesso: Costo materiale più alto, ma necessario per la conformità CXL 3.0.

Se il numero di strati supera 20:

- Scegliere: Materiali High-Tg sopra 180 °C e materiali Low-CTE.

- Compromesso: Riduce barrel crack e pad cratering durante più cicli di reflow.

Se la densità di routing è estrema, per esempio BGA da 0,4 mm di passo:

- Scegliere: Tecnologia HDI PCB con microvias stacked.

- Compromesso: Più costosa di una soluzione a foro passante, ma migliora l’integrità del segnale riducendo naturalmente i tratti residui.

Se si usano connettori press-fit:

- Scegliere: Tolleranza foro più stretta di +0,05/-0,05 mm e, se richiesto, finitura in oro duro o stagno immersione.

- Compromesso: Richiede gestione estremamente precisa delle punte.

Se il budget è stretto ma le prestazioni restano critiche:

- Scegliere: Impilamento ibrido con materiale ULL per gli strati ad alta velocità e FR4 standard per alimentazione, massa e segnali lenti.

- Compromesso: Ciclo di laminazione più complesso e rischio di imbarcamento per mancata corrispondenza del CTE.

FAQ (costo, lead time, materiali, test, criteri di accettazione)

D: Quanto incide la foratura di retro-lavorazione sul costo dei PCB CXL 3.0? R: La foratura di retro-lavorazione aggiunge in genere il 10-20% al costo della scheda nuda. Richiede un programma NC separato, macchine specializzate per il controllo della profondità e ispezioni aggiuntive a raggi X.

D: Qual è il tempo di consegna tipico per materiali Ultra-Low Loss? R: Materiali come Megtron 7 o Tachyon hanno spesso tempi di consegna di 2-4 settimane se non sono disponibili a stock. Per esigenze di PCB a consegna rapida è necessario verificare subito la disponibilità del materiale.

D: È necessario test VNA al 100% in produzione di massa? R: No. Il test VNA al 100% è troppo lento e costoso. In genere si esegue TDR d’impedenza al 100% e si usa un campionamento statistico, ad esempio un pannello per lotto, per verificare la perdita d’inserzione via VNA.

D: Possiamo usare FR4 standard per design CXL 3.0? R: No. L’FR4 standard ha un Df di circa 0,020, che genera perdite elevate a 16 GHz, Nyquist per 32 GT/s, e a 32 GHz, Nyquist per 64 GT/s. Bisogna usare materiali con Df < 0,005.

D: Qual è la larghezza minima della traccia per 85 Ω? R: Dipende dall’impilamento, ma per le stripline è tipicamente 4-5 mil, cioè 0,10-0,127 mm. Tracce più strette aumentano le perdite da effetto pelle; tracce più larghe richiedono dielettrici più spessi.

D: Come gestite l’effetto della tessitura del vetro in produzione? R: Utilizziamo vetro steso, quindi fibre meccanicamente allargate, oppure instradiamo le tracce con un piccolo angolo, per esempio 10°, rispetto alla tessitura. In questo modo si mediano le variazioni di Dk.

D: Qual è la finitura superficiale migliore per CXL 3.0? R: ENIG o ENEPIG. Entrambe forniscono una superficie piana per componenti a passo fine e non aggiungono perdite significative come HASL.

D: Quali sono i criteri di accettazione per l’impedenza in produzione di massa? R: IPC Class 2 o 3 usa spesso ±10% come valore predefinito, ma per CXL 3.0 bisogna specificare ±5% nelle note di fabbricazione e nel disegno principale.

Glossario (termini chiave)

| Termine | Significato | Perché conta nella pratica |

|---|---|---|

| PAM4 | Pulse Amplitude Modulation a 4 livelli. | Codifica 2 bit per UI e richiede SNR e linearità superiori rispetto a NRZ. |

| UI (Unit Interval) | Durata temporale di un bit o simbolo. | A 64 GT/s l’UI è estremamente breve, circa 15,6 ps, con margine minimo per il jitter. |

| Insertion Loss (IL) | Perdita di potenza del segnale lungo la traccia. | È il principale limite alla lunghezza della traccia; il budget va pianificato con attenzione, ad esempio -30 dB sull’intero canale. |

| Return Loss (RL) | Potenza di segnale riflessa verso la sorgente. | È causata da disadattamento d’impedenza e degrada l’occhio del segnale. |

| Backdrilling | Rimozione della porzione inutilizzata di un foro metallizzato passante, cioè del tratto residuo. | È essenziale per CXL 3.0 quando i fori passanti lascerebbero risonatori troppo lunghi. |

Conclusione

La produzione in serie di un PCB con interfaccia CXL 3.0 risulta più gestibile quando specifiche e piano di verifica vengono definiti presto e poi confermati tramite revisione DFM e copertura dei test. Usate regole, checkpoint e schemi di troubleshooting indicati sopra per ridurre i cicli di iterazione e proteggere la resa quando i volumi crescono. Se un vincolo non è ancora chiaro, validatelo con un piccolo lotto pilota prima di bloccare il rilascio produttivo.