Il calcolo ad alte prestazioni richiede velocità di trasferimento dati più elevate tra chip eterogenei, rendendo il controllo dell'impedenza della scheda di interconnessione EMIB un fattore critico nell'incapsulamento moderno dei semiconduttori. Man mano che i progetti si muovono verso il packaging 2.5D e le architetture chiplet, i confini tradizionali tra il PCB e il substrato del package si sfumano. Garantire l'integrità del segnale attraverso il ponte integrato e il substrato organico circostante richiede un'esecuzione di produzione precisa. Questa guida fornisce un flusso di lavoro completo per ingegneri e team di approvvigionamento per gestire l'impedenza in queste interconnessioni avanzate.

Punti Chiave

- Definizione: Il controllo dell'impedenza della scheda di interconnessione EMIB si riferisce al mantenimento di una specifica impedenza caratteristica (solitamente 85Ω o 100Ω differenziale) attraverso la transizione dal ponte di silicio al substrato organico.

- Metrica Critica: La perdita di ritorno e la perdita di inserzione sono altrettanto importanti quanto il valore di impedenza target ($Z_0$) nell'integrazione di chiplet ad alta velocità.

- Impatto del Materiale: La disomogeneità della costante dielettrica ($D_k$) tra il ponte di silicio e gli strati di costruzione del PCB è la fonte primaria di riflessione del segnale.

- Idea Sbagliata: Molti presumono che le tolleranze standard dei PCB (+/- 10%) siano sufficienti; tuttavia, i progetti EMIB spesso richiedono un controllo di +/- 5% o più stretto.

- Validazione: I test di riflettometria nel dominio del tempo (TDR) devono essere eseguiti su specifici coupon di test che imitano la transizione ponte-scheda, non solo su coupon di traccia standard.

- Consiglio di produzione: Il controllo della rugosità superficiale del rame è essenziale per minimizzare le perdite per effetto pelle a frequenze superiori a 25 GHz.

- APTPCB (APTPCB PCB Factory) è specializzata nei processi di PCB HDI e simili a substrato ad alta precisione necessari per supportare queste architetture di packaging avanzate.

Cosa significa realmente il controllo dell'impedenza delle schede di interconnessione EMIB

Comprendere la definizione fondamentale è il primo passo prima di analizzare metriche specifiche e tolleranze di produzione.

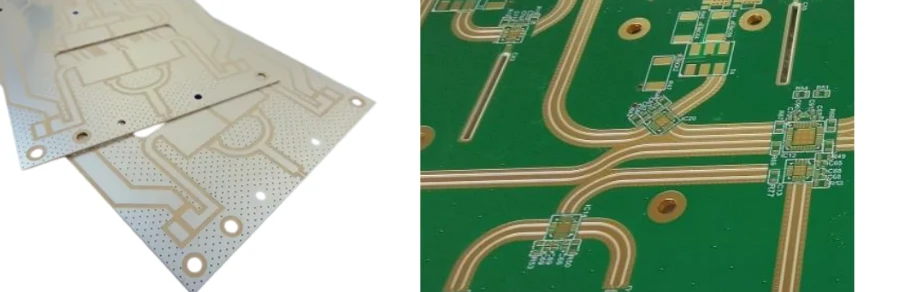

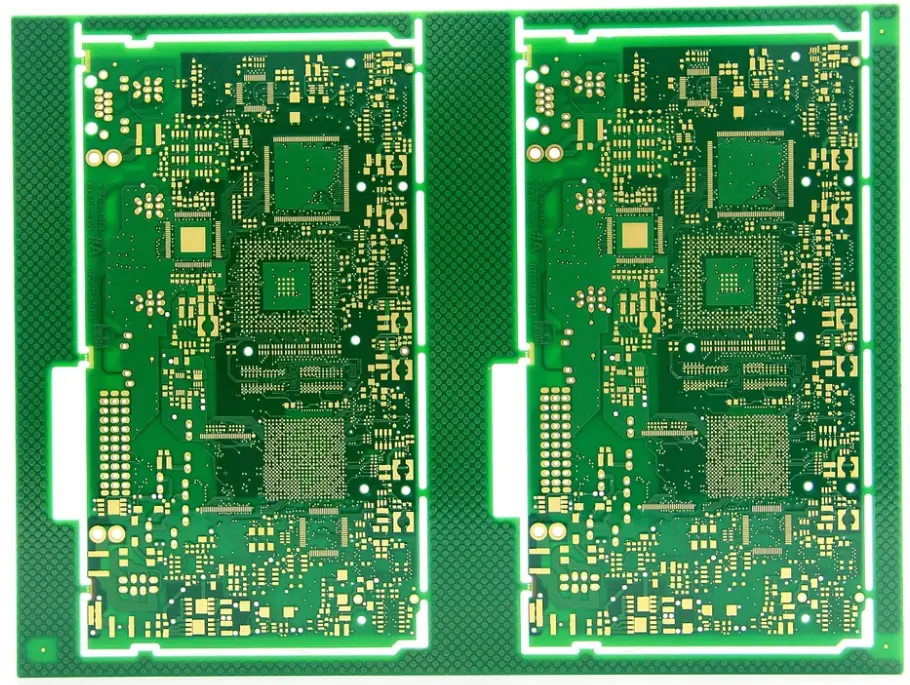

Il controllo dell'impedenza delle schede di interconnessione EMIB è la disciplina ingegneristica che gestisce la resistenza elettrica ai segnali CA mentre viaggiano tra il ponte di silicio incorporato e il substrato del package organico. A differenza dei PCB standard dove le tracce corrono su strati uniformi di fibra di vetro, una struttura EMIB (Embedded Multi-die Interconnect Bridge) implica un ambiente ibrido. I segnali devono attraversare da un die di silicio, attraverso micro-bump, in un ponte di silicio, e da lì al substrato del package. La "scheda di interconnessione" in questo contesto funge da portante. Deve corrispondere all'impedenza dell'instradamento a passo ultra-fine sul ponte di silicio. Se l'impedenza non corrisponde all'interfaccia, si verificano riflessioni del segnale. Queste riflessioni causano corruzione dei dati, aumento dei tassi di errore di bit (BER) e riduzione dell'efficienza energetica. Per APTPCB, raggiungere questo controllo significa utilizzare tecniche HDI (High Density Interconnect) avanzate, microvias laser e materiali dielettrici ultrasottili che colmano il divario tra la produzione di semiconduttori e la fabbricazione tradizionale di PCB.

Metriche di controllo dell'impedenza della scheda di interconnessione EMIB che contano

Una volta definito l'ambito del controllo dell'impedenza, gli ingegneri devono quantificare la qualità utilizzando indicatori di prestazione specifici.

Il successo di un progetto di scheda di interconnessione EMIB si basa sulla stretta aderenza alle metriche di integrità del segnale. Nelle applicazioni ad alta velocità come gli acceleratori AI o i processori per data center, un semplice "passa/non passa" sulla resistenza è insufficiente. È necessario valutare come la scheda si comporta su uno spettro di frequenza.

| Metrica | Perché è importante | Intervallo tipico / Fattori | Come misurare |

|---|---|---|---|

| Impedenza Caratteristica ($Z_0$) | Determina se il percorso del segnale corrisponde alla sorgente e al carico. I disadattamenti causano riflessioni. | 85Ω o 100Ω (Differenziale); 50Ω (Single-ended). Tolleranza: ±5% a ±10%. | Riflettometria nel Dominio del Tempo (TDR) su coupon di test. |

| Perdita di inserzione | Misura quanta potenza del segnale viene persa mentre viaggia attraverso l'interconnessione. | < -1,5 dB per pollice alla frequenza di Nyquist. Fortemente influenzato dalla rugosità del rame e da $D_k$. | Analizzatore di rete vettoriale (VNA) o estrazione dei parametri S. |

| Perdita di ritorno | Misura la quantità di segnale riflessa verso la sorgente a causa di discontinuità di impedenza. | < -10 dB a -15 dB è desiderabile. Minore è meglio. | VNA (parametro S11). |

| Skew (Intra-coppia) | La differenza di ritardo temporale tra le linee positiva e negativa di una coppia differenziale. | < 5 ps (picosecondi). Critico per la segnalazione differenziale. | TDR o Oscilloscopio. |

| Stabilità della costante dielettrica ($D_k$) | Le variazioni di $D_k$ causano fluttuazioni di impedenza lungo la traccia. | $D_k$ stabile su tutte le frequenze (es. 3,0 - 3,5 per substrati avanzati). | Verifica della scheda tecnica del materiale e anelli risonatori. |

| Rugosità superficiale del rame | Il rame ruvido aumenta la resistenza alle alte frequenze (effetto pelle). | $R_z$ < 2 µm (si consiglia lamina di rame VLP o HVLP). | Profilometro o SEM (Microscopio Elettronico a Scansione). |

Come scegliere il controllo dell'impedenza della scheda di interconnessione EMIB: guida alla selezione per scenario

Una volta stabilite le metriche, la prossima sfida è selezionare la giusta strategia di controllo basata sullo scenario applicativo specifico. Diversi casi d'uso finale richiedono diversi livelli di rigore nel controllo dell'impedenza delle schede di interconnessione EMIB. Una sovra-specifica aggiunge costi inutili, mentre una sotto-specifica porta a guasti del sistema.

Scenario 1: Calcolo ad alte prestazioni (HPC) e IA

- Requisito: Larghezza di banda massima (integrazione HBM).

- Compromesso: Richiede la tolleranza di impedenza più stretta (±5%) e materiali a bassissima perdita.

- Guida: Scegliere film di build-up avanzati (ABF) e rame HVLP. Il costo è secondario rispetto alle prestazioni.

Scenario 2: Dispositivi mobili di consumo

- Requisito: Miniaturizzazione e durata della batteria.

- Compromesso: I vincoli di spazio impongono dielettrici più sottili, rendendo più difficile il controllo dell'impedenza.

- Guida: Dare priorità ai materiali con nucleo sottile. Accettare tolleranze leggermente più ampie (±7-10%) per mantenere la resa e ridurre i costi.

Scenario 3: Sistemi ADAS automobilistici

- Requisito: Affidabilità e stabilità termica.

- Compromesso: I materiali devono resistere ai cicli termici, che possono alterare l'impedenza nel tempo.

- Guida: Selezionare materiali ad alto Tg con $D_k$ stabile su ampi intervalli di temperatura. La convalida deve includere test di stress termico.

Scenario 4: Infrastruttura 5G / Stazioni base

- Requisito: Alta frequenza e bassa latenza.

- Compromesso: Le lunghe tracce sul substrato aumentano i rischi di perdita di inserzione.

- Guida: Concentrarsi su laminati "Low Loss" e "Ultra Low Loss". Il controllo dell'impedenza deve tenere conto delle bande di frequenza specifiche (mmWave).

Scenario 5: Prototipo / NPI (Introduzione Nuovo Prodotto)

- Requisito: Velocità di consegna e debug.

- Compromesso: I tempi rapidi potrebbero limitare la disponibilità dei materiali.

- Guida: Utilizzare materiali ad alta velocità standard disponibili. Concentrarsi sulla convalida della logica di progettazione piuttosto che sull'ottimizzazione perfetta dell'impedenza.

Scenario 6: Produzione di Massa (Sensibile ai Costi)

- Requisito: Resa ed efficienza dei costi.

- Compromesso: Non può sostenere tolleranze ultra-strette senza alti tassi di scarto.

- Guida: Progettazione per la Produzione (DFM). Allargare le tracce dove possibile per rendere l'impedenza meno sensibile alle variazioni di incisione.

Punti di controllo per l'implementazione del controllo dell'impedenza delle schede di interconnessione EMIB

Dopo aver selezionato la strategia giusta, l'attenzione si sposta sull'esecuzione tattica, dai file di progettazione al prodotto finale.

L'implementazione del controllo dell'impedenza delle schede di interconnessione EMIB richiede uno sforzo sincronizzato tra l'ingegnere di layout e il reparto di produzione. Utilizzare questa checklist per assicurarsi che nessun passaggio critico venga tralasciato durante il processo di fabbricazione del PCB HDI.

- Definizione dello Stackup:

- Raccomandazione: Definire esplicitamente il numero di strati, gli spessori dielettrici e i pesi del rame.

- Rischio: Stackup ambigui portano a calcoli di impedenza errati da parte dell'ingegnere CAM.

- Accettazione: Foglio di stackup approvato firmato sia dal progettista che dal fabbricante.

Selezione del materiale:

- Raccomandazione: Specificare la serie esatta del materiale (es. Megtron 6, Rogers o film ABF specifici).

- Rischio: Le indicazioni generiche "FR4" falliranno alle velocità EMIB.

- Accettazione: Certificazione del materiale (CoC) dal fornitore.

Larghezza e spaziatura delle tracce (L/S):

- Raccomandazione: Regolare la larghezza delle tracce in CAM per compensare i fattori di incisione (forma trapezoidale).

- Rischio: L'eccessiva incisione riduce la larghezza delle tracce, aumentando l'impedenza.

- Accettazione: Analisi in sezione trasversale (micro-sezione) che verifica la geometria.

Continuità del piano di riferimento:

- Raccomandazione: Assicurare piani di massa solidi sotto i segnali ad alta velocità, specialmente vicino all'interfaccia del ponte.

- Rischio: Le interruzioni nel piano di riferimento causano immediate discontinuità di impedenza.

- Accettazione: Ispezione Ottica Automatica (AOI) degli strati interni.

Registrazione dei microvia:

- Raccomandazione: L'allineamento della foratura laser deve essere preciso per collegare i pad del ponte al substrato.

- Rischio: Il disallineamento modifica l'accoppiamento capacitivo, alterando l'impedenza.

- Accettazione: Ispezione a raggi X dell'allineamento dei via.

Spessore della placcatura in rame:

- Raccomandazione: Mantenere una distribuzione uniforme della placcatura.

- Rischio: Le variazioni nello spessore del rame influenzano l'induttanza totale della linea.

- Accettazione: Misurazione dello spessore non distruttiva (CMI).

Applicazione della finitura superficiale:

- Raccomandazione: Utilizzare ENIG o ENEPIG per superfici piane adatte al wire bonding o al flip-chip.

- Rischio: Le finiture HASL spesse creano superfici irregolari e variazioni di impedenza.

- Accettazione: Misurazione dello spessore della finitura superficiale (XRF).

Compensazione dell'incisione:

- Raccomandazione: La fabbrica deve applicare una compensazione globale dell'incisione basata sul peso del rame.

- Rischio: L'incisione incoerente su tutto il pannello porta a variazioni di impedenza tra le unità.

- Accettazione: Test del coupon di impedenza sui bordi del pannello.

Effetto della maschera di saldatura:

- Raccomandazione: Tenere conto del $D_k$ della maschera di saldatura nel calcolo dell'impedenza (per gli strati esterni).

- Rischio: La maschera di saldatura riduce l'impedenza di 2-3 ohm; ignorare ciò causa guasti.

- Accettazione: Misurazione TDR dopo l'applicazione della maschera di saldatura.

Validazione TDR finale:

- Raccomandazione: Test al 100% dei coupon di impedenza per lotti critici.

- Rischio: Spedizione di schede che superano la continuità elettrica ma falliscono l'integrità del segnale.

- Accettazione: Rapporto TDR che mostra il superamento/fallimento rispetto alla tolleranza.

Errori comuni nel controllo dell'impedenza delle schede di interconnessione EMIB

Anche con una checklist, errori specifici si verificano frequentemente nell'ambiente complesso della produzione di ponti embedded.

Evitare questi comuni errori nel controllo dell'impedenza delle schede di interconnessione EMIB può far risparmiare settimane di tempo di riprogettazione e migliaia di dollari in scarti.

- Ignorare la "zona di transizione": La discontinuità di impedenza più critica si verifica quando il segnale si sposta dal ponte di silicio al substrato del PCB. I progettisti spesso abbinano l'impedenza della traccia ma ignorano la capacità parassita del pad/bump di atterraggio. Correzione: Simulare la transizione in risolutori di campo 3D e ottimizzare lo stack del pad.

- Utilizzare costanti dielettriche generiche: Affidarsi al valore $D_k$ "di marketing" (es. 4,0) invece del valore dipendente dalla frequenza (es. 3,8 a 10 GHz). Correzione: Richiedere la tabella dei materiali dipendenti dalla frequenza da APTPCB.

- Trascurare i modelli di rugosità del rame: I calcolatori di impedenza standard assumono rame liscio. A velocità EMIB, la rugosità aggiunge un ritardo e una perdita significativi. Correzione: Utilizzare il modello Huray o fattori di correzione della rugosità simili nei calcoli.

- Coupon di test inadeguati: Posizionare i coupon di test troppo lontano dal circuito effettivo o utilizzare progetti che non corrispondono alla densità effettiva delle tracce. Correzione: Utilizzare coupon incorporati o strutture di test "in-circuit" ove possibile.

- Trascurare le tolleranze di fabbricazione: Progettare una linea da 50 ohm che richiede una traccia da 3,1 mil, quando la capacità minima della fabbrica è di 3 mil +/- 0,5 mil. Correzione: Consultare tempestivamente il Calcolatore di impedenza e le regole di progettazione.

- Mancata considerazione delle aree ricche di resina: Nei substrati eterogenei, la resina può accumularsi negli spazi tra le tracce, modificando il $D_k$ locale. Correzione: Utilizzare un riempimento di rame fittizio (thieving) per garantire una distribuzione e una pressatura uniformi della resina.

Domande frequenti (FAQ) sul controllo dell'impedenza delle schede di interconnessione EMIB

Per concludere i dettagli tecnici, ecco le risposte alle domande più urgenti riguardanti la logistica e l'esecuzione.

D: In che modo un rigoroso controllo dell'impedenza delle schede di interconnessione EMIB influisce sul costo complessivo? R: Il restringimento delle tolleranze da ±10% a ±5% può aumentare i costi del 15-25%. Ciò è dovuto alla necessità di materiali di qualità superiore, test TDR più frequenti e rese di produzione inferiori.

D: Qual è il tempo di consegna tipico per i prototipi di schede di interconnessione EMIB con requisiti di impedenza? R: I tempi di consegna standard sono di 15-20 giorni. Tuttavia, se sono richiesti materiali specializzati a bassa perdita o film ABF, i tempi di consegna possono estendersi a 4-6 settimane a seconda della disponibilità del materiale.

D: Quali materiali sono i migliori per il controllo dell'impedenza delle schede di interconnessione EMIB a 56 Gbps? R: Il FR4 standard non è adatto. Dovresti usare materiali come Panasonic Megtron 6/7, Isola Tachyon o film Ajinomoto Build-up (ABF) specializzati che offrono una bassa tangente di perdita ($D_f$) e un $D_k$ stabile.

D: Come vengono eseguiti i test per gli strati interrati in un substrato EMIB? A: Testare gli strati interrati è difficile sulla scheda finita. Utilizziamo "coupon di test" posizionati sui bordi del pannello che hanno la stessa struttura di strato e geometria delle tracce della scheda reale. Questi vengono testati tramite TDR prima che gli strati esterni vengano laminati o dopo la fabbricazione finale.

Q: Quali sono i criteri di accettazione per i test TDR su queste schede? A: Il criterio di accettazione standard è che l'impedenza misurata deve rientrare nella tolleranza specificata (ad esempio, 100Ω ±10%). Inoltre, la forma d'onda TDR dovrebbe essere liscia, senza bruschi cali o picchi che indichino discontinuità.

Q: Posso usare via standard per la progettazione di schede di interconnessione EMIB? A: Generalmente, no. I progetti EMIB richiedono un routing ad alta densità che necessita di microvia laser, via cieche e via interrate per gestire l'integrità del segnale e la densità. I fori meccanici sono spesso troppo grandi e creano troppa capacità parassita.

Q: Come specifico il controllo dell'impedenza nei miei file Gerber? A: Non affidarti solo ai nomi dei file Gerber. Includi un disegno di fabbricazione dettagliato (Fab Drawing) che elenchi gli strati specifici, le larghezze delle tracce, i piani di riferimento e i valori di impedenza target per ogni gruppo di segnali.

Q: Qual è la differenza tra impedenza single-ended e differenziale in questo contesto? A: L'impedenza single-ended si riferisce a una traccia rispetto a un piano di massa (solitamente 50Ω). L'impedenza differenziale si riferisce a due tracce l'una rispetto all'altra e al piano di massa (solitamente 85Ω o 100Ω). I percorsi dati EMIB sono quasi esclusivamente differenziali per rifiutare il rumore.

Risorse per il controllo dell'impedenza delle schede di interconnessione EMIB

- Fabbricazione di PCB ad alta velocità: Esplora le capacità di produzione di schede che supportano elevate velocità di trasmissione dati.

- Calcolatore di impedenza: Uno strumento per stimare la larghezza e la spaziatura delle tracce per l'impedenza target.

- Tecnologia PCB HDI: Scopri le tecnologie microvia e fine-line essenziali per i substrati EMIB.

- Progettazione dello stackup PCB: Linee guida sull'organizzazione degli strati per ottenere un'integrità del segnale ottimale.

Glossario del controllo dell'impedenza delle schede di interconnessione EMIB

| Termine | Definizione |

|---|---|

| EMIB | Embedded Multi-die Interconnect Bridge. Una tecnologia che utilizza un ponte di silicio incorporato in un substrato per collegare i die. |

| Impedenza ($Z_0$) | L'opposizione che un circuito presenta al passaggio di una corrente quando viene applicata una tensione. |

| TDR | Riflettometria nel dominio del tempo. Una tecnica di misurazione utilizzata per determinare l'impedenza di una linea. |

| Microvia | Un piccolo foro praticato con un laser (tipicamente < 150µm) per collegare strati adiacenti nelle schede HDI. |

| ABF | Film Ajinomoto Build-up. Un materiale isolante dominante utilizzato nei substrati IC per CPU/GPU ad alte prestazioni. |

| CTE | Coefficiente di Dilatazione Termica. La velocità con cui un materiale si espande con il calore. Le disuguaglianze causano problemi di affidabilità. |

| Insertion Loss | Perdita di Inserzione. La perdita di potenza del segnale risultante dall'inserimento di un dispositivo (o traccia) in una linea di trasmissione. |

| Return Loss | Perdita di Ritorno. La perdita di potenza nel segnale restituito/riflesso da una discontinuità in una linea di trasmissione. |

| Differential Pair | Coppia Differenziale. Due segnali complementari utilizzati per trasmettere dati, offrendo un'elevata immunità al rumore. |

| Skin Effect | Effetto Pelle. La tendenza della corrente alternata ad alta frequenza a distribuirsi vicino alla superficie del conduttore. |

| Dielectric Constant ($D_k$) | Costante Dielettrica ($D_k$). Una misura della capacità di un materiale di immagazzinare energia elettrica in un campo elettrico. Influisce sulla velocità del segnale e sull'impedenza. |

| Loss Tangent ($D_f$) | Tangente di Perdita ($D_f$). Una misura della potenza del segnale persa come calore all'interno del materiale dielettrico. |

| RDL | Strato di Ridistribuzione. Strati metallici su un die o substrato che reindirizzano i pad I/O a posizioni diverse. |

Conclusionee: Prossimi passi per il controllo dell'impedenza della scheda di interconnessione EMIB

La padronanza del controllo dell'impedenza delle schede di interconnessione EMIB è un prerequisito per competere nell'era dei chiplet e dell'integrazione eterogenea. Richiede un cambiamento di mentalità, dal "collegare punti" al "gestire linee di trasmissione". Comprendendo le metriche di perdita di inserzione e perdita di ritorno, selezionando i materiali giusti e applicando rigorosi punti di controllo di produzione, potete garantire che i vostri progetti ad alte prestazioni funzionino come previsto.

Se siete pronti a portare il vostro progetto dal concetto alla produzione, APTPCB è pronta ad assistervi. Per ottenere una revisione DFM accurata e un preventivo, si prega di fornire quanto segue:

- File Gerber (RS-274X) o dati ODB++.

- Diagramma di stackup che indica i materiali desiderati e il numero di strati.

- Requisiti di impedenza (ad es. Strato 3, 100Ω Diff, Larghezza traccia 4mil).

- Netlist per la validazione dei test elettrici.

Visitate la nostra Pagina di preventivo per iniziare il vostro progetto oggi stesso.