Punti chiave

- Definizione: La copertura ICT (In-Circuit Test) di fabbrica per PLC si riferisce alla percentuale di reti e componenti su una scheda di Controllore Logico Programmabile che possono essere verificati elettricamente durante la produzione.

- Criticità: A differenza dell'elettronica di consumo, i PLC richiedono un'affidabilità prossima al 100%; difetti non rilevati possono portare a guasti industriali catastrofici.

- Metriche: Lo standard PCOLA/SOQ è il punto di riferimento del settore per misurare la qualità della copertura, non solo semplici punti percentuali.

- Design for Test (DFT): Raggiungere un'elevata copertura inizia nella fase schematica, non in fabbrica.

- Compromessi: Una copertura più elevata spesso richiede PCB più grandi o attrezzature più costose; bilanciare questo è fondamentale per una produzione economicamente vantaggiosa.

- Validazione: I rapporti di simulazione devono essere convalidati rispetto ai risultati dei test fisici durante l'Ispezione del Primo Articolo (FAI).

- Partnership: Lavorare con un produttore competente come APTPCB (APTPCB PCB Factory) assicura che la tua strategia DFT si allinei con le effettive capacità di produzione.

Nel contesto dei Controllori Logici Programmabili (PLC) (ambito e limiti)

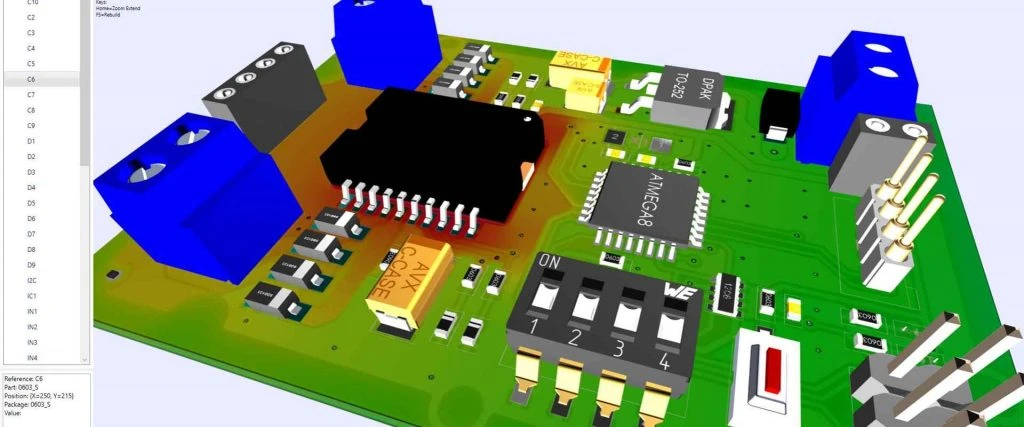

Comprendere l'ambito dei test è il primo passo per garantire l'affidabilità industriale nei sistemi di controllo. Copertura ICT di fabbrica per PLC è una misura quantitativa di quanta logica e connettività di una scheda a circuito stampato può essere convalidata utilizzando un tester "a letto di aghi". Nel contesto dei Controllori Logici Programmabili (PLC), questa metrica è molto più critica che nell'elettronica generale. I PLC operano in ambienti difficili che comportano vibrazioni, temperature estreme e interferenze elettromagnetiche. Una giunzione di saldatura che supera un'ispezione visiva ma fallisce un test di stress elettrico può causare un arresto della fabbrica mesi dopo.

L'ICT (In-Circuit Test) si concentra specificamente su:

- Cortocircuiti e Interruzioni: Assicurando che non esistano ponti non intenzionali tra le reti e che le tracce siano continue.

- Valori dei Componenti: Verificando che resistenza, capacità e induttanza corrispondano alla distinta base (BOM).

- Presenza e Orientamento dei Componenti: Assicurando che i chip siano montati e ruotati correttamente.

- Funzione dei Componenti Attivi: Eseguendo controlli logici di base su diodi, transistor e circuiti integrati.

È importante distinguere la copertura ICT dalla copertura del Test Funzionale del Circuito (FCT). L'ICT cerca difetti di fabbricazione (ponti di saldatura, parti sbagliate), mentre l'FCT verifica che la scheda esegua la sua logica prevista. Per un PLC, un'elevata copertura ICT è la base che rende significativo l'FCT. Se le connessioni fisiche non vengono verificate per prime, il debug funzionale diventa impossibile. Presso APTPCB, sottolineiamo che la copertura non è solo un numero percentuale. È uno strumento di gestione del rischio. Una scheda con una copertura del 95% potrebbe comunque mancare l'unico relè di sicurezza critico che protegge l'intero sistema. Pertanto, l'ambito deve dare priorità alle "reti critiche" rispetto alle statistiche di copertura generiche.

Metriche importanti (come valutare la qualità)

Misurare la copertura richiede più di un semplice rapporto passa/non passa; richiede un'analisi granulare di specifici tipi di difetti.

Per valutare veramente la copertura ICT di fabbrica per PLC, gli ingegneri utilizzano metriche specifiche che categorizzano ciò che viene testato e quanto bene. Lo standard industriale per questo è il modello PCOLA/SOQ. Questo modello separa gli attributi dei componenti (PCOLA) dagli attributi di connessione (SOQ).

| Metrica | Perché è importante | Intervallo tipico o fattori influenzanti | Come misurare |

|---|---|---|---|

| Rapporto di accesso al test | Determina se le sonde possono raggiungere fisicamente le reti. | 90% - 100%. Inferiore sulle schede HDI. | (Reti con punti di test / Reti totali) × 100. |

| Copertura dei componenti | Assicura che le parti corrette siano installate. | 85% - 98%. Limitato dai condensatori di bypass in parallelo. | Conteggio dei componenti con valori verificati / Conteggio totale della distinta base. |

| Copertura della rete | Verifica continuità e isolamento. | 95% - 100%. Critico per i piani di alimentazione e di massa. | Conteggio delle reti completamente testate / Conteggio totale della netlist. |

| Tasso di falsi fallimenti | Un alto numero di falsi fallimenti rallenta la produzione e danneggia i pad. | < 500 PPM. Influenzato dalla qualità del fixture e dalla sollecitazione. | (Falsi allarmi / Schede totali testate) × 1.000.000. |

| Punteggio PCOLA | Verifica Presenza, Correttezza, Orientamento, Funzionamento, Allineamento. | Alto. Essenziale per IC e connettori complessi. | Analisi software automatizzata della generazione del programma di test. |

| Punteggio SOQ | Verifica Cortocircuiti, Aperture, Qualità (integrità della saldatura). | Critico. Deve essere vicino al 100% per la sicurezza del PLC. | Misurato tramite soglie di resistenza durante la fase di test di cortocircuito/apertura. |

| Gauge R&R | Garantisce che il fixture di test sia coerente e ripetibile. | < 10%. Se >30%, il sistema di test non è affidabile. | Analisi statistica di misurazioni ripetute sulla stessa unità. |

Guida alla selezione per scenario (compromessi)

Diversi scenari di produzione dettano approcci diversi per raggiungere una copertura di test ottimale.

Raggiungere il 100% di copertura ICT di fabbrica per PLC è spesso fisicamente impossibile o economicamente non fattibile. È necessario selezionare la strategia giusta in base al ciclo di vita del prodotto e ai vincoli tecnici. Di seguito sono riportati scenari comuni e l'approccio raccomandato per ciascuno.

1. Produzione ad alto volume, a basso mix

- Scenario: Produzione di massa di moduli I/O PLC standard.

- Raccomandazione: Investire in un fixture a vuoto di fascia alta con sonda a doppio lato.

- Compromesso: Elevato costo iniziale degli strumenti (5k $ - 15k $), ma il tempo di test per unità più basso e la massima ripetibilità.

- Approfondimento APTPCB: Per volumi superiori a 5.000 unità, il costo dell'attrezzatura si ammortizza rapidamente, giustificando la spesa per la massima copertura.

2. Prototipo e NPI (Introduzione Nuovo Prodotto)

- Scenario: Prima produzione di una nuova scheda CPU PLC.

- Raccomandazione: Utilizzare il test a sonde mobili (FPT) invece di un'attrezzatura ICT fissa.

- Compromesso: Costo degli strumenti pari a zero, ma tempo di test per scheda molto lento.

- Perché: Le modifiche al design sono frequenti. L'FPT consente di aggiornare i punti di test nel software senza dover ricostruire un'attrezzatura fisica.

3. Design con interconnessioni ad alta densità (HDI)

- Scenario: PLC compatti che utilizzano micro-vias e BGA a passo fine.

- Raccomandazione: Combinare ICT con Boundary Scan (JTAG) e Ispezione a raggi X automatizzata (AXI).

- Compromesso: Le sonde ICT non possono raggiungere ogni rete nella tecnologia PCB HDI. È necessario affidarsi a JTAG per la logica digitale e ai raggi X per i giunti di saldatura BGA.

- Rischio: Affidarsi esclusivamente all'ICT qui comporterà una bassa copertura (<60%).

4. PLC critici per la sicurezza (SIL 3 / SIL 4)

- Scenario: PLC utilizzati nei sistemi di arresto di emergenza.

- Raccomandazione: Test ridondante. Copertura ICT al 100% sulle reti di sicurezza, seguita da FCT al 100%.

- Compromesso: Costo più elevato e tempo di ciclo più lungo.

- Focus: L'adesione agli standard di sicurezza per la progettazione di PCB PLC spesso richiede slot di isolamento fisico, il che può complicare la sigillatura sottovuoto per i dispositivi di fissaggio. Qui sono preferiti i dispositivi di fissaggio meccanici a pressione.

5. Controllori Industriali ad Alta Tensione

- Scenario: PLC che gestiscono direttamente ingressi a 220V/480V.

- Raccomandazione: ICT selettivo. Non sondare direttamente le reti ad alta tensione se il tester non è in grado di gestire la potenziale scarica.

- Compromesso: Copertura inferiore sugli ingressi di alimentazione per proteggere le apparecchiature di test.

- Mitigazione: Utilizzare l'ispezione visiva (AOI) per la sezione ad alta tensione e l'ICT per la logica a bassa tensione.

6. Schede Rivestite (Rivestimento Conforme)

- Scenario: PLC destinati ad ambienti umidi o corrosivi.

- Raccomandazione: Testare prima del rivestimento. Se è richiesto il test dopo il rivestimento, utilizzare punte in gomma conduttiva o mascheratura specializzata.

- Compromesso: La mascheratura aggiunge manodopera. Le sonde perforanti possono danneggiare il rivestimento, compromettendo la protezione dall'umidità.

Dalla progettazione alla produzione (punti di controllo dell'implementazione)

L'implementazione di successo dell'ICT è un processo lineare che inizia molto prima che il layout del PCB sia finalizzato.

Per garantire un'elevata copertura ICT di fabbrica per i PLC, i progettisti devono seguire un rigoroso flusso di lavoro Design for Test (DFT). L'adattamento di punti di test su un layout finito è una ricetta per problemi di integrità del segnale e scarsa copertura.

- Fase Schematica - Prioritizzazione delle Net: Identificare le net critiche (alimentazione, reset, clock, bus di comunicazione). Contrassegnarle come "Da Testare Obbligatoriamente" nello schema.

- Fase di Layout - Posizionamento dei Punti di Test: Posizionare i punti di test (TP) sul lato inferiore del PCB ogni volta che sia possibile. I fixture a lato singolo sono significativamente più economici e affidabili di quelli a doppio lato.

- Allineamento alla Griglia: Allineare i TP a una griglia di 2.54mm (100 mil) o 1.27mm (50 mil). I punti fuori griglia richiedono una costosa foratura personalizzata per il fixture.

- Geometria del TP: Utilizzare un diametro minimo del pad da 0.8mm a 1.0mm per le sonde standard. Pad più piccoli (0.5mm) richiedono sonde costose e fragili.

- Regole di Spazio: Mantenere almeno 1.5mm di spazio tra i punti di test e i corpi dei componenti per evitare che la testa della sonda colpisca il componente.

- Considerazioni EMC: Quando si tratta di zonizzazione EMC e messa a terra per PLC, assicurarsi che i punti di test sulle linee ad alta velocità non agiscano come antenne. Utilizzare punti di test "senza stub" o coprirli con schermatura di massa se necessario.

- Fori di Fissaggio: Includere almeno due fori di fissaggio non placcati (3mm+) negli angoli opposti. Questi allineano il PCB al fixture. Senza di essi, una sondatura accurata è impossibile.

- Generazione Gerber: Esportare un file specifico "Punto di Test" o una netlist IPC-356. Non fare affidamento sul produttore per indovinare quali pad sono per il test.

- Fabbricazione del Fixture: Inviare i dati alla ditta di fixture 2-3 settimane prima della costruzione del PCB.

- Debugging: Il primo passaggio di solito produce falsi fallimenti. Regolare le tolleranze del software (ad es. varianza del resistore) piuttosto che modificare fisicamente la scheda.

- Test con estensimetro: Prima della produzione di massa, misurare lo stress meccanico che il dispositivo applica al PCB. Una flessione eccessiva può rompere i condensatori ceramici.

- Documentazione: Creare un "Rapporto di Copertura" che dettagli esattamente quali reti vengono testate e quali vengono saltate. Questo è vitale per la risoluzione dei problemi futuri.

Per specifiche dettagliate sui requisiti di layout, fare riferimento alle nostre linee guida DFM.

Errori comuni (e l'approccio corretto)

Anche gli ingegneri esperti cadono in trappole che riducono la copertura o aumentano i costi di produzione.

Evitare questi errori garantisce che la vostra strategia di copertura ICT di fabbrica per PLC sia efficace e sicura.

- Errore: Posizionare i punti di test sotto componenti BGA o a basso profilo.

- Correzione: I punti di test devono essere accessibili. Se una rete è accessibile solo sotto un BGA, sdoppiarla su una via o un pad dedicato.

- Errore: Affidarsi a "Via-in-Pad" per la sonda.

- Correzione: La sonda di vie placcate può causare "crepe a barile" o un contatto inaffidabile a causa di vuoti di saldatura. Utilizzare sempre un pad di test piatto e solido.

- Errore: Ignorare i componenti alti.

- Correzione: Condensatori o trasformatori alti sul lato inferiore impediscono alla scheda di appoggiarsi piatta sul dispositivo. Mantenere il lato inferiore relativamente piatto o creare zone di "esclusione" per i componenti alti.

- Errore: Presupporre che sia necessaria una copertura del 100%.

- Correzione: Inseguire l'ultimo 5% di copertura (solitamente condensatori di bypass o resistori di pull-up) può raddoppiare il costo del dispositivo. Accettare una copertura inferiore sui componenti passivi non critici se il controllo del processo è buono.

- Errore: Dimenticare la routine di "scarica".

- Correzione: I grandi condensatori nei PLC immagazzinano energia. Il dispositivo ICT deve avere un circuito di scarica per evitare di bruciare le sonde del tester al contatto.

- Errore: Utilizzare la maschera di saldatura sui punti di test.

- Correzione: I punti di test devono avere un'apertura nella maschera. Le sonde non possono penetrare la maschera di saldatura in modo affidabile senza danneggiare la punta o la scheda.

- Errore: Trascurare la densità delle sonde.

- Correzione: Troppe sonde in una piccola area (alta densità) creano una massiccia pressione verso l'alto, potenzialmente deformando la scheda. Distribuire i punti di test in modo uniforme.

- Errore: Trascurare gli standard di produzione di PCB per il controllo industriale.

- Correzione: Le schede industriali hanno rame più spesso e profili termici diversi. Assicurarsi che i parametri di test tengano conto della maggiore capacità di trasporto di corrente delle tracce.

Domande frequenti (FAQ)

D: Qual è il costo tipico per un dispositivo ICT per PLC? A: Un dispositivo standard a "letto di aghi" costa tipicamente tra i $2.000 e i $6.000, a seconda del numero di punti di test e se è a lato singolo o doppio.

D: L'ICT può testare il software sul PLC? R: Generalmente, no. L'ICT testa l'hardware (fisica). Tuttavia, alcuni sistemi ICT avanzati possono eseguire la "Programmazione Flash" per caricare il bootloader iniziale, che è un ponte per il test del software.

D: In cosa differisce l'ICT dal Test a Sonda Volante? R: L'ICT utilizza un dispositivo fisso per testare tutti i punti simultaneamente (veloce, alto costo di setup). La Sonda Volante utilizza bracci robotici mobili per testare i punti sequenzialmente (lento, costo di setup zero). L'ICT è per la produzione di massa; la Sonda Volante è per i prototipi.

D: Qual è la spaziatura minima tra i punti di test? R: Per le sonde standard (100 mil), mantenere 2,54 mm centro-a-centro. Per il passo fine (50 mil), si può scendere a 1,27 mm, ma il costo del dispositivo aumenta e la durabilità diminuisce.

D: L'ICT danneggia il PCB? R: Lascia piccoli "segni di contatto" (fossette) sulle piazzole di test. Questo è normale e accettabile. Tuttavia, una pressione eccessiva può rompere i giunti di saldatura, motivo per cui è richiesto il test con estensimetri.

D: Posso usare le via come punti di test? R: Non è raccomandato. Le via sono spesso ricoperte da maschera di saldatura. Anche se aperte, sono irregolari. È meglio aggiungere una piazzola di test dedicata collegata alla via.

D: Come gestisco i punti di test per le coppie differenziali ad alta velocità? A: L'aggiunta di un punto di test crea uno "stub" che può riflettere i segnali. Per bus di comunicazione PLC ad altissima velocità, utilizzare la simulazione per assicurarsi che il punto di test non degradi l'integrità del segnale, oppure testare queste linee tramite boundary scan.

Q: Perché il mio rapporto di copertura mostra una bassa percentuale? A: Questo accade spesso se si hanno molti condensatori in parallelo (il tester li vede come un unico grande condensatore) o se si hanno molte reti fisicamente inaccessibili (ad esempio, all'interno di un BGA senza fan-out).

Q: Ho bisogno dell'ICT se ho l'AOI (Ispezione Ottica Automatica)? A: Sì. L'AOI controlla solo se il componente ha l'aspetto corretto. Non può dire se un resistore ha il valore sbagliato, se un chip è guasto o se c'è una saldatura fredda sotto un componente.

Q: Quali dati necessita APTPCB per quotare l'ICT? A: Abbiamo bisogno dei file Gerber, della BOM (Bill of Materials), del file XY Pick and Place e della Netlist elettrica (formato IPC-356).

Pagine e strumenti correlati

- Servizi di test ICT: Esplora le nostre capacità specifiche relative all'hardware e al software di test in-circuit.

- PCB per controllo industriale: Scopri i requisiti specifici di materiale e fabbricazione per l'elettronica industriale.

- Linee guida DFM: Scarica la nostra checklist per assicurarti che il tuo progetto sia pronto per i test di produzione di massa.

Glossario (termini chiave)

| Termine | Definizione |

|---|---|

| Letto di aghi | Un tradizionale dispositivo ICT contenente centinaia di sonde a molla che contattano contemporaneamente il PCB. |

| DFT (Design for Test) | La pratica ingegneristica di progettare un layout PCB specificamente per facilitare un test facile e completo. |

| DUT (Device Under Test) | L'assemblaggio PCB specifico attualmente posizionato nel dispositivo di test. |

| Fixture | L'interfaccia meccanica (hardware personalizzato) che tiene il PCB e allinea le sonde ai punti di test. |

| Netlist | Un file di testo che descrive la connettività elettrica del PCB, definendo quali pin dei componenti sono collegati a quali net. |

| Pogo Pin | Una sonda a molla utilizzata nei dispositivi di test per stabilire un contatto elettrico con i pad del PCB. |

| IPC-356 | Il formato di file standard utilizzato per comunicare le coordinate dei punti di test e le informazioni sulla netlist al produttore. |

| Boundary Scan (JTAG) | Un metodo per testare le interconnessioni su IC complessi (come gli FPGA) senza sonde fisiche, utilizzando un'interfaccia seriale. |

| Witness Mark | La piccola indentazione lasciata su un pad di saldatura dalla sonda di test; prova che il punto è stato testato. |

| Strain Gauge | Un sensore utilizzato per misurare la flessione fisica o lo stress applicato al PCB durante la compressione sottovuoto del dispositivo. |

| False Fail | Un risultato di test che indica un difetto quando la scheda è in realtà buona, solitamente causato da un contatto scadente della sonda o tolleranze strette. |

| Guard Trace | Una tecnica nell'ICT in cui le reti circostanti sono portate a una tensione specifica per isolare il componente in fase di misurazione. |

Conclusionee (prossimi passi)

Ottenere un'elevata copertura ICT di fabbrica per PLC non è un ripensamento; è una decisione strategica che influisce sulla sicurezza e l'affidabilità dei sistemi industriali. Comprendendo le metriche PCOLA/SOQ, selezionando la giusta strategia di fixture e aderendo a rigorose regole DFT, si garantisce che ogni PLC che lascia la linea sia pronto per la dura realtà del reparto di produzione.

Per portare avanti il vostro progetto PLC, APTPCB raccomanda una revisione DFM completa prima di finalizzare il layout. Quando richiedete un preventivo, fornite:

- File Gerber (incluso un layer dedicato ai punti di test, se disponibile).

- BOM (Bill of Materials) con i codici articolo del produttore.

- Netlist (formato IPC-356).

- Schemi (PDF) per riferimento di debug.

- Requisiti di Test Specifici (es. "È necessario testare il 100% dei circuiti dei relè di sicurezza").

Test di alta qualità sono la polizza assicurativa per la reputazione del vostro marchio. Iniziate il vostro percorso di validazione con i dati giusti e il partner giusto.