Investire nel Design for Manufacturability (DFM) e nel Design for Testability (DFT) è una scelta strategica che sposta il controllo qualità da una logica reattiva di correzione a una logica preventiva di eliminazione del difetto prima che compaia. Per buyer e product manager, capire come ridurre i difetti PCBA con DFM e DFT è uno dei modi più efficaci per abbassare il costo totale e accelerare il time-to-market. Questa guida raccoglie le specifiche tecniche e i criteri decisionali utili per allineare il progetto elettronico alle reali capacità produttive.

Punti salienti

- Prevenzione proattiva: il DFM intercetta prima della produzione i problemi di layout che generano ponti di saldatura, tombstoning e void.

- Copertura di test: il DFT fa sì che, se un difetto si presenta, venga rilevato con ICT o test funzionale invece di arrivare sul campo.

- Riduzione dei costi: correggere un difetto nella fase di progettazione costa circa 10x meno che farlo in assemblaggio e circa 100x meno che farlo dopo la consegna.

- Allineamento con il fornitore: specifiche chiare su stencil e profili di reflow sono essenziali per componenti complessi come BGA e QFN.

Punti chiave

Prima di entrare nei dettagli tecnici, questa tabella riassume come DFM e DFT incidano direttamente su costi e affidabilità del prodotto.

| Feature | DFM (Design for Manufacturability) | DFT (Design for Testability) |

|---|---|---|

| Obiettivo principale | Garantire che il prodotto possa essere costruito con continuità e resa elevata. | Garantire che il prodotto possa essere verificato in modo rapido e accurato. |

| Focus sul difetto | Previene l’insorgenza di difetti, ad esempio ponti di saldatura. | Rileva i difetti che si verificano comunque, ad esempio circuiti aperti. |

| Output chiave | Geometrie pad ottimizzate, thermal relief, spaziature tra componenti. | Test point, accesso JTAG, scan chain. |

| Driver del ROI | First Pass Yield (FPY) più alto, meno rilavorazioni. | Tasso di guasto sul campo più basso, diagnosi più rapida. |

Come ridurre i difetti PCBA con DFM e DFT: ambito, contesto decisionale e criteri di successo

La riduzione dei difetti non inizia in linea, ma già in fase di schema e layout. Quando un buyer chiede come ridurre i difetti PCBA con DFM e DFT, deve capire che sta acquistando capacità di processo, non una semplice scheda commodity.

Contesto decisionale

I buyer devono spesso bilanciare più tempo di ingegneria all’inizio contro maggiore velocità nella produzione a valle. Saltare le revisioni DFM per accelerare un prototipo porta spesso a schede difficili da assemblare o a tassi di scarto elevati in produzione di volume. Il corretto livello di controllo dipende dalla complessità della PCBA. Una scheda semplice con passivi di grandi dimensioni può richiedere poco DFM, mentre una scheda HDI con BGA richiede un’analisi rigorosa.

Criteri di successo

Per capire se DFM e DFT stanno funzionando, conviene monitorare almeno questi indicatori:

- First Pass Yield (FPY): percentuale di schede che superano tutti i test senza rilavorazione. Per i prodotti maturi, 98%+ è un obiettivo comune.

- Copertura di test: percentuale di net e componenti raggiungibili dal collaudo automatico. Un DFT ben impostato punta a 90%+.

- Tasso di falsi scarti: frequenza con cui schede buone vengono respinte per limiti di test errati o fixture instabili.

- Engineering Change Orders (ECO): una riduzione degli ECO legati all’assemblaggio segnala che il DFM sta dando risultati.

Specifiche da definire in anticipo

| Parameter | Recommended value / option | Why it matters | How to verify |

|---|---|---|---|

| Layer count | 4–8 (tipico), di più se necessario | Influisce su costo, resa e margine di sbroglio | Stackup + report DFM |

| Min trace/space | 4/4 mil (tipico) | Incide su resa e lead time | DRC + capacità produttiva |

| Via strategy | Through vias vs VIPPO vs microvia | Influisce sull’affidabilità dell’assemblaggio | Microsezione + criteri IPC |

| Surface finish | ENIG/OSP/HASL | Influisce su saldabilità e planarità | COC + test di saldabilità |

| Solder mask | Verde opaco (default) | Migliora leggibilità AOI e riduce il rischio di ponti | Prova AOI + registrazione mask |

| Test | Flying probe / ICT / FCT | Compromesso tra copertura e costo | Coverage report + piano fixture |

| Acceptance class | IPC Class 2 / 3 | Definisce i limiti di difetto accettabili | Note a disegno + report di ispezione |

| Lead time | Standard vs expedited | Influisce sul rischio di pianificazione | Offerta + conferma capacità |

Per rendere DFM e DFT realmente efficaci, alcuni requisiti devono comparire in modo esplicito nel data package. Quando il dato non è chiaro, il reparto produttivo colma il vuoto con supposizioni, e lì nascono molti difetti.

1. Requisiti dati per il DFM

Fornite al contract manufacturer (CM) molto più dei soli file Gerber.

- Selezione della classe IPC: specificate chiaramente se la scheda deve essere costruita secondo IPC-A-610 Class 2 o Class 3. Questa scelta determina criteri di volume di saldatura e di allineamento.

- Footprint dei componenti: richiedete la verifica dei footprint rispetto alla Bill of Materials (BOM). Le discrepanze tra componente reale e land pattern sono tra le cause più comuni di problemi DFM.

- Strategia di pannellizzazione: definite il panel array. Una pannellizzazione scorretta può generare fratture da stress nei condensatori ceramici durante il depaneling.

- Ponti di solder mask: specificate una distanza minima di solder mask tra i pad, tipicamente 4 mil, per evitare ponti di saldatura sugli IC a passo fine.

2. Requisiti dati per il DFT

Il DFT viene spesso affrontato troppo tardi, con il risultato di fixture bed of nails costosi che non riescono nemmeno a raggiungere le net critiche.

- Accessibilità dei test point: imponete che tutte le net critiche abbiano un test point sul lato inferiore del PCB. In questo modo si rende possibile un In-Circuit Test (ICT) monofaccia, molto più economico.

- Clearance dei test point: definite una distanza minima, per esempio 50 mil, tra test point e componenti alti per evitare collisioni o danni alle sonde.

- JTAG/Boundary Scan: sulle schede digitali complesse assicuratevi che la chain JTAG sia instradata e accessibile. Così si possono testare le connessioni tra chip senza contatto fisico diretto.

- Netlist: fornite sempre una netlist IPC-356. Permette al produttore di confrontare la connettività dei Gerber con quella dello schema.

Risorse correlate

Rischi chiave: cause radice, rilevazione precoce e prevenzione

Capire i difetti tipici aiuta a dare priorità corretta alle revisioni DFM. I casi più critici si concentrano spesso sotto componenti bottom-terminated come QFN (Quad Flat No-lead) e BGA.

1. Void nei componenti QFN e BGA

I void sono sacche d’aria intrappolate nel giunto di saldatura. Un livello eccessivo di void riduce la conducibilità termica e la robustezza meccanica.

- Rischio: surriscaldamento di QFN di potenza a causa di un trasferimento termico insufficiente attraverso una saldatura con molti void.

- Prevenzione (DFM): applicate le qfn reflow best practices to reduce voids. Significa suddividere in finestre l’apertura di pasta sul thermal pad. Invece di stampare un grande blocco di pasta che intrappola i gas, si stampa una griglia di piccoli quadrati con copertura intorno al 50-70%, creando percorsi di sfogo per i volatili durante il reflow.

2. Difetti di saldatura BGA: ponti e opens

I BGA sono impegnativi perché i giunti sono nascosti.

- Rischio: difetti Head-in-Pillow (HiP), in cui la sfera poggia sulla pasta ma non coalesca correttamente.

- Prevenzione (DFM/processo): serve un controllo rigoroso secondo bga voiding control: stencil, reflow, and x-ray criteria.

- Stencil: usate stencil elettrolucidati con aperture trapezoidali per migliorare il rilascio della pasta.

- Reflow: ottimizzate la zona di soak. Se il flux si esaurisce troppo presto, l’ossidazione impedisce il corretto wetting.

- Criteri ai raggi X: definite limiti chiari di accettazione. In IPC Class 2, i void devono tipicamente restare sotto il 25% dell’area della sfera.

3. Tombstoning

Questo difetto si verifica quando un piccolo componente passivo si solleva su un’estremità durante il reflow.

- Causa radice: forze di bagnatura sbilanciate, spesso perché un pad è collegato a un grande piano di massa che agisce da dissipatore, mentre l’altro è connesso a una pista sottile.

- Prevenzione (DFM): usate thermal relief sui pad di massa in modo che entrambi i pad raggiungano la temperatura di reflow nello stesso momento.

4. Shadowing

Nella saldatura a onda o selettiva, i componenti grandi possono schermare quelli piccoli e impedire alla lega di raggiungerli correttamente.

- Prevenzione (DFM): mantenete regole di spaziatura specifiche in funzione della direzione di avanzamento nella macchina di saldatura.

Validazione e accettazione: test e criteri di superamento

| Test / Check | Method | Pass criteria (example) | Evidence |

|---|---|---|---|

| Continuità elettrica | Flying probe / fixture | 100% delle net testate, nessun open o short | Report E-test |

| Dimensioni critiche | Misurazione | Conforme alle tolleranze di disegno | Registro ispezione |

| Integrità di metallizzazione / riempimento | Microsezione | Nessun void o cricca oltre i limiti IPC | Foto microsezione |

| Saldabilità | Test di bagnabilità | Bagnatura accettabile, nessun dewetting | Report di saldabilità |

| Warpage | Misura di planarità | Entro specifica, ad es. ≤0,75% | Registro warpage |

| Validazione funzionale | FCT | Tutti i casi superati, log archiviato | Log FCT |

Come si dimostra che DFM e DFT hanno avuto successo? È necessario stabilire un piano di validazione coerente con gli obiettivi di assemblaggio NPI.

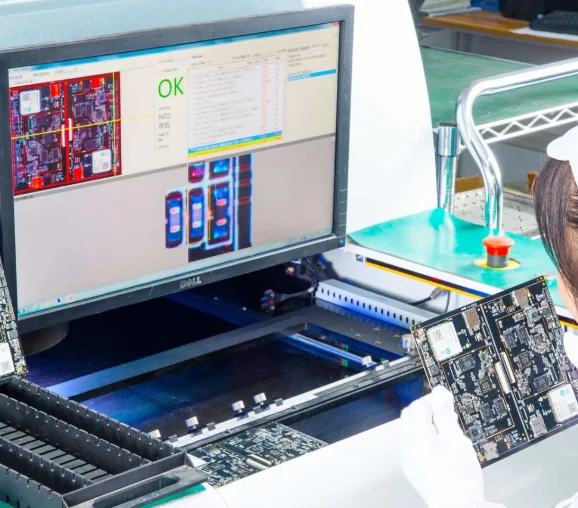

Automated Optical Inspection (AOI)

L’AOI è la prima linea di difesa. Le telecamere verificano presenza del componente, polarità, skew e qualità della saldatura.

- Criteri di superamento: nessun componente mancante, marcature di polarità allineate, filetti di saldatura conformi ai criteri IPC.

- Limite: l’AOI non può vedere sotto BGA e QFN.

X-Ray Inspection (Axi)

L’ispezione a raggi X è essenziale per validare BGA e QFN.

- Criteri di superamento: devono essere rispettate le regole di bga voiding control: stencil, reflow, and x-ray criteria. Void <25%, forma della sfera coerente, assenza di ponti.

- Applicazione: ispezione al 100% sui prototipi, a campione nella produzione di massa.

- Per approfondire: Ispezione a raggi X

In-Circuit Test (ICT) e Flying Probe

È qui che il DFT mostra il proprio valore.

- ICT: usa un fixture bed of nails per testare simultaneamente tutte le net. È rapido, ma comporta un costo elevato di attrezzatura. Richiede quindi test point definiti in fase DFT.

- Flying Probe: usa bracci robotizzati per sondare i punti senza fixture. È più lento, ma ideale per i prototipi.

- Criteri di superamento: tutti i valori passivi entro tolleranza e nessun short o open sulle net attive.

Functional Circuit Test (FCT)

È l’ultimo passaggio di validazione. La scheda viene alimentata e deve svolgere la sua funzione reale.

- Criteri di superamento: il dispositivo si avvia, il firmware si carica e le porte I/O rispondono correttamente.

Checklist di qualificazione fornitore: RFQ, audit e tracciabilità

Quando scegliete un partner che vi aiuti a ridurre i difetti PCBA con DFM e DFT, usate questa checklist.

1. Capacità ingegneristiche

- Il fornitore esegue una revisione DFM obbligatoria prima del tooling?

- Fornisce un report DFM dettagliato, e non solo un pass/fail, evidenziando rischi come acid trap o sliver?

- È in grado di suggerire footprint alternativi per migliorare la resa?

- Consultate le Linee guida DFM per il livello atteso.

2. Controllo di processo

- Ha SPI inline? La SPI previene una quota molto rilevante dei difetti di pasta e saldatura.

- Dispone di ispezione a raggi X interna?

- Sa applicare le qfn reflow best practices to reduce voids, per esempio con vacuum reflow o ottimizzazione del profilo?

3. Tracciabilità e sistema qualità

- Il sito è certificato ISO 9001 o IATF 16949?

- Offre tracciabilità a livello componente, collegando lotti specifici a numeri seriali specifici?

- Verificate il loro Sistema qualità.

Come scegliere il giusto livello di DFM e DFT: compromessi e regole decisionali

Non tutte le schede richiedono la stessa intensità di DFM e DFT. Le regole qui sotto aiutano a bilanciare costo e rischio.

Scenario A: elettronica consumer semplice, basso costo e alto volume

- Strategia: concentrarsi sul DFM per massimizzare la resa e ridurre il tempo ciclo.

- DFT: minimo. Fare affidamento su AOI e campionamento funzionale.

- Compromesso: accettare un tasso di guasto sul campo leggermente più alto per mantenere basso il costo unitario.

Scenario B: medicale o automotive, alta affidabilità e volume medio

- Strategia: DFM e DFT spinti.

- DFT: 100% ICT e 100% test funzionale.

- Compromesso: costi NRE più alti per fixture e programmazione test, ma tassi di guasto sul campo prossimi allo zero.

- Punto specifico: rispetto rigoroso di bga voiding control: stencil, reflow, and x-ray criteria.

Scenario C: prototipazione rapida

- Strategia: DFM "leggero". Correggere solo gli showstopper che impediscono l’assemblaggio.

- DFT: flying probe senza costi di fixture.

- Compromesso: tempo di test per unità maggiore, ma consegna più rapida.

FAQ: costi, lead time, file DFM, materiali e test

1. L’aggiunta di requisiti DFM/DFT fa salire il prezzo del preventivo? Sì, inizialmente. Il tempo di ingegneria e i fixture di test come NRE aumentano il costo iniziale. Tuttavia, spesso il costo totale di progetto si abbassa grazie a migliore resa e minori rilavorazioni.

2. Quanto allunga il lead time una revisione DFM? In genere 1-2 giorni. Una revisione DFM seria avviene prima dell’ordine materiali. Questo piccolo ritardo evita settimane perse più avanti per problemi di producibilità scoperti tardi.

3. Il DFM può correggere un circuito progettato male? No. Il DFM garantisce che la scheda possa essere costruita, non che funzioni correttamente. Se lo schema contiene errori logici, la scheda sarà costruita bene ma fallirà a livello funzionale.

4. Qual è la differenza tra DFM e DFA? Il DFM si riferisce di solito alla producibilità del PCB, come incisione e foratura. Il DFA riguarda l’assemblaggio dei componenti, quindi saldatura e distanze. In pratica, spesso DFM viene usato come termine ombrello per entrambi.

5. Serve l’ICT se ho già un test funzionale? Idealmente sì. L’ICT indica quale componente o quale net è in errore. Il test funzionale di solito dice solo che la scheda non funziona. Per diagnosi e riparazione, l’ICT è molto più efficiente.

6. In che modo i materiali influenzano il DFM? La scelta del materiale, ad esempio High Tg FR4, determina come la scheda si espande durante il reflow. Un CTE non allineato tra componente e scheda è una causa importante di fatica della saldatura.

7. Qual è il modo migliore per comunicare le note DFM? Inserite un file Read Me o un PDF nello zip Gerber. Elencate in modo esplicito requisiti speciali come "Do not X-out arrays" o "Mask plug vias at U1".

Richiedere un preventivo o una revisione DFM: cosa inviare

Volete ottimizzare la vostra PCBA per la produzione di massa? Inviate il vostro data package per una revisione DFM completa.

Checklist per la richiesta di offerta:

- File Gerber (RS-274X): strati rame, solder mask, serigrafia, forature e strati pasta.

- Bill of Materials (BOM): file Excel con Manufacturer Part Numbers (MPN) e reference designator.

- File centroid (Pick and Place): coordinate X-Y e dati di rotazione.

- Assembly drawing: PDF con posizione dei componenti e marcature di polarità.

- Requisiti di test: descrizione della copertura desiderata, ad esempio ICT, FCT o burn-in.

Glossario: termini chiave

| Term | Meaning | Why it matters in practice |

|---|---|---|

| DFM | Design for Manufacturability: regole di layout per ridurre i difetti. | Evita rilavorazioni, ritardi e costi nascosti. |

| AOI | Automated Optical Inspection per individuare difetti di saldatura e assemblaggio. | Migliora la copertura e intercetta derive precoci. |

| ICT | In-Circuit Test per verificare opens, shorts e valori elettrici. | Test strutturale rapido per produzioni di volume. |

| FCT | Functional Circuit Test con scheda alimentata e comportamento verificato. | Valida la funzione reale sotto carico. |

| Flying Probe | Test elettrico senza fixture con sonde mobili. | Adatto a prototipi e volumi bassi o medi. |

| Netlist | Definizione di connettività per confrontare il design con il PCB prodotto. | Individua opens e shorts prima dell’assemblaggio. |

| Stackup | Costruzione degli strati con core, prepreg, rame e spessore. | Influenza impedenza, warpage e affidabilità. |

| Impedance | Comportamento controllato delle tracce per segnali RF o high-speed, ad es. 50Ω. | Evita riflessioni e problemi di integrità del segnale. |

| ENIG | Finitura superficiale con nichel chimico e oro a immersione. | Bilancia saldabilità e planarità; va controllato lo spessore del nichel. |

| OSP | Organic Solderability Preservative come finitura superficiale. | Economico, ma più sensibile a manipolazione e reflow multipli. |

Conclusione: passi successivi

Capire come ridurre i difetti PCBA con DFM e DFT significa investire nella durata del prodotto e nella reputazione del marchio. Quando definite con precisione specifiche di stencil, profili di reflow e accessibilità al test, trasformate un processo opaco in un processo controllabile e prevedibile.

Coinvolgete il partner produttivo fin dalle prime fasi di progetto. Una revisione condivisa delle qfn reflow best practices to reduce voids e di bga voiding control: stencil, reflow, and x-ray criteria consente di risparmiare tempo e capitale. Date priorità alla trasparenza del data package, validate con rigore e scegliete un fornitore che consideri la qualità una responsabilità condivisa.