La tecnologia al carburo di silicio (SiC) ha rivoluzionato l'elettronica di potenza con velocità di commutazione più elevate e maggiore efficienza, ma questi vantaggi introducono gravi sfide di layout. L'implementazione delle corrette migliori pratiche per i PCB dei gate driver degli inverter SiC è l'unico modo per prevenire guasti catastrofici causati da induttanza parassita, ringing e interferenze elettromagnetiche (EMI). A differenza dei tradizionali IGBT, i MOSFET SiC commutano a velocità dV/dt estremamente elevate, il che significa che anche pochi nanohenry di induttanza parassita possono causare sovratensioni che distruggono il dispositivo o corrompono il segnale di gate.

Presso APTPCB (APTPCB PCB Factory), vediamo molti progetti fallire non a causa dello schema, ma perché il layout fisico ha ignorato la fisica unica dei semiconduttori a banda larga. Questa guida fornisce una checklist completa, intervalli di specifiche e passaggi per la risoluzione dei problemi per garantire che il design del PCB del gate driver del vostro inverter SiC sia robusto, producibile e affidabile.

Risposta Rapida (30 secondi)

Per gli ingegneri che necessitano di indicazioni immediate sulle migliori pratiche per i PCB dei gate driver degli inverter SiC, concentratevi innanzitutto sulla minimizzazione dell'area del loop.

- Minimizzare l'induttanza del loop di gate: Posizionare il gate driver il più vicino fisicamente possibile al MOSFET SiC. La lunghezza totale della traccia dovrebbe idealmente essere inferiore a 20 mm.

- Utilizzare connessioni Kelvin Source: Separare sempre il percorso della sorgente di alimentazione dal percorso di ritorno del gate drive per evitare che l'induttanza di sorgente comune rallenti la commutazione o causi falsi inneschi.

- Ottimizzare i condensatori di disaccoppiamento: Posizionare condensatori ceramici a basso ESL (C0G/NP0) direttamente sui pin di alimentazione del driver.

- Controllare l'immunità ai transitori di modo comune (CMTI): Assicurarsi che la barriera di isolamento (optocoppiatore o isolatore digitale) abbia un rating CMTI >100 kV/µs e minimizzare la capacità di accoppiamento attraverso il gap di isolamento.

- Strategia di impilamento degli strati: Utilizzare uno stack a 4 o 6 strati con un piano di massa solido immediatamente adiacente allo strato del segnale per schermare dal rumore.

- Distanza di isolamento per alta tensione: Gli inverter SiC spesso operano a 800V+; assicurarsi che le distanze di fuga e di isolamento soddisfino gli standard IEC 60664-1 (tipicamente >8mm per isolamento rinforzato).

Quando applicare (e quando non applicare) le migliori pratiche per i PCB dei driver gate per inverter SiC

Comprendere quando applicare rigorosamente questi standard aiuta a bilanciare costi e prestazioni.

Quando applicare rigorosamente queste migliori pratiche:

- Sistemi di propulsione EV ad alta tensione: Sistemi che operano con architetture di batteria a 400V o 800V dove il dV/dt supera i 50 V/ns.

- Commutazione ad alta frequenza: Convertitori che operano sopra i 50 kHz dove le perdite di commutazione dominano e la risonanza parassita è più probabile.

- Progetti a elevata densità di potenza: Inverter compatti dove la gestione termica e la prossimità dei componenti aumentano il rischio di crosstalk.

- Applicazioni critiche per la sicurezza: Inverter di trazione automobilistici o robotica industriale dove un errore di accensione del gate potrebbe causare la distruzione dell'hardware o pericoli per la sicurezza.

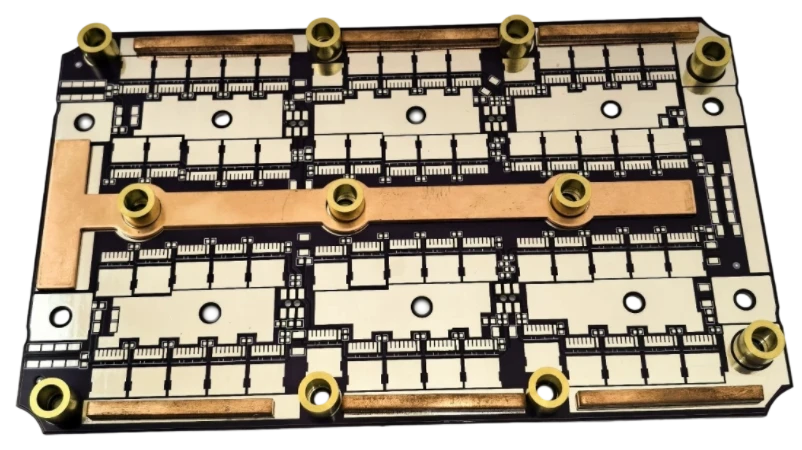

- Assemblaggio PCB del driver di gate per inverter SiC: Quando il processo di assemblaggio coinvolge die nudi sensibili o componenti a montaggio superficiale densamente impacchettati che richiedono un controllo preciso della pasta saldante.

Quando le pratiche PCB standard potrebbero essere sufficienti (e queste regole sono eccessive):

- MOSFET in silicio a bassa tensione: Se si utilizzano FET in silicio standard da 24V o 48V con velocità di commutazione lente, le regole di layout standard sono solitamente sufficienti.

- Azionamenti IGBT a bassa frequenza: Gli azionamenti motore legacy che commutano a <5 kHz sono meno sensibili all'induttanza parassita rispetto al SiC.

- Elettronica di consumo sensibile ai costi: Adattatori a bassa potenza dove i guadagni di efficienza dal SiC non giustificano l'aumento del costo di fabbricazione del PCB per materiali specializzati.

- Prototipazione su breadboard: Sebbene non raccomandato per l'alimentazione, il test logico iniziale a bassa tensione non richiede il controllo dell'impedenza (anche se non rifletterà le prestazioni reali).

Regole e specifiche

Seguendo il contesto dell'applicazione, devono essere definite regole parametriche specifiche per guidare il processo di layout. La seguente tabella illustra le specifiche critiche per le migliori pratiche PCB del driver di gate per inverter SiC.

| Regola | Valore/Intervallo consigliato | Perché è importante | Come verificare | Se ignorato |

|---|---|---|---|---|

| Lunghezza della traccia del gate | < 20 mm (Max) | Riduce l'induttanza parassita ($L_g$) che causa il ringing. | Misurare nello strumento di layout CAD. | Oscillazione del gate, potenziale distruzione del MOSFET. |

| Larghezza della Traccia del Gate | > 20 mil (0,5 mm) | Riduce resistenza e induttanza; gestisce correnti di picco (spesso >5A). | Controllare i vincoli di larghezza della traccia. | Commutazione lenta, tracce surriscaldate. |

| Area del Loop del Gate | Minimizzare (Accoppiamento stretto) | I loop grandi agiscono come antenne per EMI e aumentano l'induttanza. | Ispezione visiva; eseguire tracce sovrapposte su strati adiacenti. | EMI elevata, accensione falsa (effetto Miller). |

| Distanza di Creepaggio dell'Isolamento | > 8 mm (per sistemi a 800V) | Previene l'arco elettrico attraverso la barriera di isolamento. | DRC (Design Rule Check) nel CAD. | Rottura dielettrica, guasto di sicurezza. |

| Valutazione CMTI | > 100 kV/µs | I SiC commutano velocemente; i componenti con CMTI basso avranno glitch durante le transizioni. | Controllare il datasheet del componente. | Perdita di controllo del gate durante la commutazione. |

| Distanza del Condensatore di Decoupling | < 2 mm dal pin | Fornisce corrente istantanea per la commutazione; stabilizza VDD. | Controllo visivo del posizionamento. | Calo di VDD, comportamento erratico del driver. |

| Induttanza del Via | Minimizzare (Usare più via) | I via singoli aggiungono ~1nH; più via in parallelo riducono questo. | Contare i via sui percorsi ad alta corrente. | Impedenza del percorso aumentata, ringing. |

| Spaziatura della Traccia di Desaturazione | > 0,5 mm di separazione | La rilevazione di desaturazione è sensibile all'accoppiamento del rumore. | Regole di clearance DRC. | Falso intervento di guasto. |

| Piano di Massa | Solido, Ininterrotto | Fornisce percorso di ritorno e schermatura. | Rivedere i file Gerber per le divisioni. | Rimbalzo di massa, perdita di integrità del segnale. |

| Peso del Rame | 2 oz o superiore | Gestisce correnti continue elevate e favorisce la dissipazione termica. | Specificare nelle note di fabbricazione. | Punti caldi termici, fusione delle tracce. |

| Tg del Materiale | > 170°C (Tg elevata) | Il SiC si riscalda; l'FR4 standard potrebbe delaminarsi. | Controllare la scheda tecnica del materiale (es. Isola 370HR). | Delaminazione del PCB, crepe nei fori metallizzati. |

| Simmetria | Corrispondenza lato Alto/Basso | L'asimmetria causa sfasamento temporale e stress non uniforme. | Misurare le lunghezze dei percorsi per il ponte H. | Rischio di shoot-through, carico termico non uniforme. |

Fasi di implementazione

Una volta comprese le specifiche, il progetto deve essere eseguito metodicamente. Ecco il flusso di lavoro passo-passo per l'implementazione delle migliori pratiche per i PCB dei gate driver di inverter SiC.

- Strategia di posizionamento dei componenti

- Azione: Posizionare prima i MOSFET SiC e gli IC del gate driver.

- Parametro chiave: Distanza < 20mm.

- Controllo di accettazione: Verificare che il pin di uscita del driver sia rivolto direttamente verso il pin del gate del MOSFET per evitare tracce tortuose.

- Instradamento della sorgente Kelvin

- Azione: Instradare la traccia di ritorno del gate direttamente al pin della sorgente del MOSFET, separata dal piano di massa di potenza principale.

- Parametro chiave: Il punto di connessione Kelvin deve essere sul pad.

- Controllo di accettazione: Assicurarsi che la "Sorgente di Potenza" e la "Sorgente del Driver" non condividano un percorso fino al pin del MOSFET.

- Ottimizzazione del loop del gate

- Azione: Instradare le tracce di Gate e Ritorno su strati adiacenti (es. Strato 1 e Strato 2) esattamente uno sopra l'altro.

- Parametro Chiave: Induttanza dell'anello < 10 nH.

- Controllo di Accettazione: Utilizzare un visualizzatore PCB o uno strumento 3D per visualizzare l'area dell'anello; dovrebbe apparire come una linea, non un cerchio.

- Minimizzazione dell'Anello di Potenza

- Azione: Posizionare il condensatore di collegamento DC il più vicino possibile al mezzo ponte per minimizzare l'anello di commutazione.

- Parametro Chiave: Induttanza del bus < 20 nH.

- Controllo di Accettazione: Verificare che le piastre del bus positive e negative si sovrappongano pesantemente per annullare i campi magnetici.

- Progettazione della Barriera di Isolamento

- Azione: Creare una chiara zona "keep-out" sotto i componenti di isolamento (optocoppie/trasformatori). Rimuovere tutto il rame degli strati interni in questa zona.

- Parametro Chiave: Distanza di fuga > 8mm (dipendente dal sistema).

- Controllo di Accettazione: Eseguire un DRC ad Alta Tensione per assicurarsi che nessun rame invada lo spazio di isolamento.

- Layout del Condensatore di Decoupling

- Azione: Posizionare i condensatori ceramici C0G/NP0 immediatamente sui pin VDD/VEE del driver.

- Parametro Chiave: Lunghezza della traccia al condensatore < 2mm.

- Controllo di Accettazione: Assicurarsi che i via che collegano i condensatori a massa siano raddoppiati o triplicati per ridurre l'induttanza.

- Cucitura di Via Termici

- Azione: Posizionare array di via termici sotto i pad esposti del driver e dei MOSFET.

- Parametro Chiave: Diametro del via 0.3mm, passo 0.6mm.

- Verifica di accettazione: Verificare che l'apertura della maschera di saldatura consenta la dissipazione del calore ma impedisca la risalita della saldatura (potrebbe essere necessaria la tenting o la plugging).

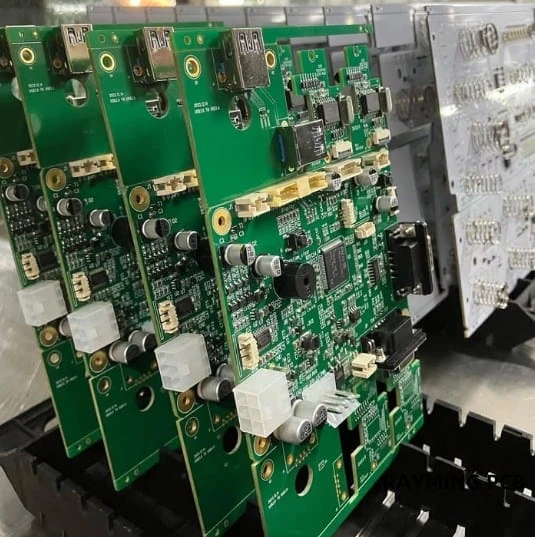

- Revisione DFM per l'assemblaggio

- Azione: Controllare la spaziatura dei componenti per il pick-and-place automatizzato, specialmente per schede con rame pesante.

- Parametro chiave: Spaziatura minima dei componenti.

- Verifica di accettazione: Consultare le linee guida DFM per assicurarsi che il design sia producibile su larga scala.

Modalità di guasto e risoluzione dei problemi

Anche con un processo di progettazione rigoroso, possono sorgere problemi durante i test. La risoluzione dei problemi delle migliori pratiche per i PCB dei gate driver di inverter SiC richiede l'identificazione di sintomi specifici che indicano difetti di layout.

Sintomo: Overshoot eccessivo sulla tensione di gate

- Causa: Elevata induttanza parassita nel loop del gate.

- Controllo: Misurare la lunghezza della traccia dal driver al gate. Controllare la presenza di via nel percorso del gate.

- Soluzione: Accorciare le tracce; rimuovere i via se possibile. Aggiungere una perlina di ferrite o aumentare leggermente la resistenza di gate ($R_g$) (compromesso con la velocità di commutazione).

- Prevenzione: Utilizzare il routing stripline o microstrip con un piano di massa immediatamente sottostante.

Sintomo: Accensione falsa (effetto Miller)

- Causa: Accoppiamento dV/dt elevato attraverso la capacità di Miller ($C_{gd}$) che aumenta la tensione di gate.

- Controllo: Cercare picchi di tensione sul gate del dispositivo SPENTO quando il dispositivo ACCESO commuta.

- Soluzione: Implementare un Active Miller Clamp o utilizzare una tensione di spegnimento negativa (es. -5V).

Prevenzione: Mantenere l'impedenza del percorso di spegnimento del gate estremamente bassa.

Sintomo: Latch-Up o Reset del Driver

- Causa: Violazione dell'immunità ai transitori di modo comune (CMTI) o rimbalzo di massa.

- Controllo: Verificare il grado di isolamento del driver. Controllare la differenza di potenziale di massa tra il lato logico e quello di potenza.

- Soluzione: Aggiungere induttori di modo comune; migliorare la capacità di isolamento.

- Prevenzione: Selezionare driver di gate con CMTI > 100 kV/µs.

Sintomo: Surriscaldamento del MOSFET (Statico)

- Causa: Tensione di gate che non raggiunge la piena saturazione (es. 15V o 18V) o percorso termico scadente.

- Controllo: Misurare $V_{gs}$ al pin. Controllare la continuità del via termico.

- Soluzione: Aumentare la larghezza della traccia per l'alimentazione al driver; migliorare il fissaggio del dissipatore.

- Prevenzione: Utilizzare rame pesante (2oz+) e substrati termici ad alte prestazioni.

Sintomo: Fallimento del Test EMI/EMC

- Causa: Grandi anelli di commutazione di potenza che agiscono come antenne.

- Controllo: Analizzare l'area fisica dell'anello da DC+ a DC- includendo l'interruttore.

- Soluzione: Aggiungere circuiti snubber (RC o RCD); migliorare la schermatura.

- Prevenzione: Design con busbar laminare o piani di potenza PCB sovrapposti.

Sintomo: Rottura Dielettrica (Scarica ad Arco)

- Causa: Distanza di fuga/spazio insufficiente per l'altitudine operativa o il grado di inquinamento.

- Controllo: Ispezionare il PCB per tracce di carbonio o bruciature attraverso gli spazi di isolamento.

Correzione: Fresare fessure (intagli) nel PCB per aumentare la distanza di fuga.

Prevenzione: Seguire rigorosamente le tabelle IEC 60664-1 durante il layout.

Decisioni di progettazione

La risoluzione dei problemi spesso riconduce a scelte di progettazione fondamentali fatte all'inizio del progetto.

Selezione dello Stackup dei Livelli Per gli inverter SiC, una scheda standard a 2 strati è raramente sufficiente a causa della necessità di bassa induttanza.

- Stackup a 4 Livelli: Segnale / Massa / Alimentazione / Segnale. Questo è il minimo raccomandato. Il piano di massa interno agisce da schermo e riduce l'induttanza di loop per le tracce dello strato superiore.

- Stackup a 6 Livelli: Consente strati di schermatura dedicati e un migliore isolamento tra la logica ad alta tensione e quella a bassa tensione.

Selezione del Materiale L'FR4 standard (Tg 130-140°C) potrebbe non resistere al ciclo termico delle applicazioni SiC ad alta potenza.

- FR4 ad alto Tg: Materiali come Isola 370HR (Tg 180°C) sono raccomandati per l'affidabilità.

- Rame Pesante: L'uso di rame da 2oz, 3oz o anche 4oz aiuta con la diffusione termica e la riduzione della resistenza delle tracce ad alta corrente.

Topologia del Gate Driver

- Isolato vs. Non Isolato: Gli inverter ad alta tensione richiedono invariabilmente isolamento galvanico (ottico, capacitivo o magnetico).

- Alimentazione Bipolare: L'uso di +15V/-5V è una decisione di progettazione standard per prevenire l'accensione involontaria, richiedendo specifiche considerazioni di layout dell'alimentazione sul PCB.

Domande frequenti (FAQ)

D: Qual è la regola più critica per il layout del gate driver SiC? A: Minimizzare l'induttanza del loop di gate è la cosa più critica.

- Mantenere le tracce corte (<20mm).

- Far passare le tracce di gate e di ritorno parallele e vicine tra loro.

- Evitare i via nel percorso del gate.

D: Ho davvero bisogno di una tensione di gate negativa per il SiC? R: Sebbene alcuni FET SiC possano funzionare a 0V spenti, una tensione negativa (da -3V a -5V) è altamente raccomandata.

- Fornisce un margine di sicurezza contro l'accensione per effetto Miller.

- Accelera i tempi di spegnimento.

D: Posso usare FR4 standard per PCB di inverter SiC? R: Dipende dalla temperatura e dalla tensione.

- Per prototipi o potenze inferiori, l'FR4 standard va bene.

- Per alta densità di potenza o applicazioni automobilistiche, utilizzare materiali ad alto Tg per prevenire guasti termici.

D: Come calcolo la distanza di fuga richiesta? R: Fare riferimento a standard come IEC 60664-1.

- Determinare la tensione di lavoro (es. 800V).

- Determinare il grado di inquinamento (solitamente 2 per sigillato, 3 per aperto).

- Selezionare il gruppo di materiali (valore CTI).

D: Perché il CMTI è importante per il SiC? R: Gli interruttori SiC hanno transitori di tensione molto veloci (dV/dt elevato).

- I driver con CMTI basso interpretano questo rumore come un segnale.

- Ciò causa glitch o perdita di sincronizzazione.

D: Come influisce la larghezza della traccia sul gate driver? R: Le tracce sottili hanno maggiore induttanza e resistenza.

- Ciò limita la corrente di picco che il driver può spingere/tirare.

- Rallenta la commutazione, aumentando le perdite di commutazione.

D: Devo usare una perlina sul gate? R: Una perlina di ferrite può sopprimere il ringing ad alta frequenza.

- Aggiunge resistenza alle alte frequenze senza influenzare la pilotaggio in DC.

- Posizionarlo vicino al pin del gate.

D: Qual è il vantaggio delle connessioni Kelvin source? R: Bypassano l'induttanza di sorgente comune.

- Il loop del gate non rileva la caduta di tensione causata dalla corrente di carico principale.

- Ciò si traduce in una commutazione più pulita e veloce.

D: Come verifico il controllo dell'impedenza sulle tracce del gate? R: Utilizzare un calcolatore di impedenza durante la progettazione.

- Definire lo stackup e la costante dielettrica.

- Regolare la larghezza della traccia per corrispondere all'impedenza target (anche se la minimizzazione dell'induttanza è solitamente prioritaria rispetto all'adeguamento dell'impedenza in brevi percorsi).

D: Qual è il tempo di consegna per la produzione di PCB di grado SiC? R: Varia in base alla complessità e alla disponibilità del materiale.

- Schede High Tg standard: 3-5 giorni.

- Rame pesante o substrati specializzati: 7-10 giorni.

Pagine e strumenti correlati

Per assistervi ulteriormente con le migliori pratiche per i PCB dei driver di gate per inverter SiC, utilizzate queste risorse:

- Calcolatore di impedenza PCB: Essenziale per calcolare la larghezza e la spaziatura delle tracce per gestire induttanza e impedenza.

- Linee guida DFM: Assicuratevi che il vostro layout soddisfi i vincoli di produzione per evitare costose riprogettazioni.

- Richiedi un preventivo: Pronti per la produzione? Caricate i vostri file Gerber per una rapida stima dei costi.

Glossario (termini chiave)

| Termine | Definizione | Rilevanza per PCB SiC |

|---|---|---|

| :--- | :--- | :--- |

| SiC (Carburo di Silicio) | Un materiale semiconduttore a bandgap ampio che consente tensioni più elevate e commutazioni più veloci rispetto al Silicio. | La tecnologia fondamentale che richiede regole di layout PCB specializzate. |

| dV/dt | Il tasso di variazione della tensione rispetto al tempo. | Un dV/dt elevato nel SiC crea rumore e richiede driver con CMTI elevato. |

| Induttanza Parassita | Induttanza indesiderata inerente alle tracce PCB e ai terminali dei componenti. | Il nemico principale della commutazione veloce; causa ringing e overshoot. |

| Effetto Miller | Un fenomeno in cui la capacità ($C_{gd}$) accoppia la tensione al gate, potenzialmente accendendolo. | Richiede un pilotaggio di gate negativo o Miller clamps nel design PCB. |

| Connessione Kelvin | Una tecnica di misurazione a 4 fili applicata al routing PCB per separare i percorsi di forza e di rilevamento. | Fondamentale per isolare il percorso di ritorno del gate dai percorsi di potenza ad alta corrente. |

| CMTI | Immunità ai Transitori di Modo Comune; la capacità di un isolatore di rifiutare rumore transitorio veloce. | Deve essere elevato (>100 kV/µs) per prevenire la corruzione del driver. |

| Desaturazione (Desat) | Un metodo di protezione che rileva se il MOSFET è in stato di cortocircuito. | Richiede un routing attento delle tracce di rilevamento per evitare falsi interventi. |

| Area di Loop | L'area fisica racchiusa da un percorso di corrente e il suo ritorno. | Deve essere minimizzata per ridurre EMI e induttanza. |

| Distanza di fuga | La distanza più breve tra due parti conduttive lungo la superficie dell'isolamento. | Fondamentale per l'isolamento di sicurezza ad alta tensione. |

| Distanza in aria | La distanza più breve tra due parti conduttive attraverso l'aria. | Previene l'arco elettrico nei progetti ad alta tensione. |

| Resistore di gate ($R_g$) | Un resistore posto in serie con il gate per controllare la velocità di commutazione e smorzare il ringing. | Il posizionamento e la selezione del valore sono parametri chiave di regolazione. |

| C0G/NP0 | Un tipo di dielettrico per condensatori ceramici ad alta stabilità. | Raccomandato per il disaccoppiamento e la temporizzazione in ambienti termici difficili. |

Conclusionee

L'implementazione delle migliori pratiche per i PCB dei driver di gate degli inverter SiC non riguarda solo il seguire una lista di controllo; si tratta di rispettare la fisica della commutazione ad alta velocità e alta tensione. Riducendo al minimo l'induttanza di loop, garantendo un isolamento robusto e selezionando i materiali giusti, è possibile sbloccare il pieno potenziale di efficienza della tecnologia al Carburo di Silicio senza sacrificare l'affidabilità.

Sia che stiate prototipando un nuovo inverter di trazione per veicoli elettrici o ottimizzando un alimentatore industriale, il layout è la base del vostro successo. APTPCB è specializzata nella produzione di PCB ad alte prestazioni che soddisfano queste rigorose esigenze. Se avete il vostro progetto pronto o avete bisogno di consigli sulla selezione dei materiali per il vostro prossimo progetto SiC, contattateci per una valutazione di produzione.