Punti chiave

- Ambito della definizione: il layout di un PCB di controllo per inverter trifase riguarda la disposizione fisica di gate driver, microcontrollori e circuiti di misura mantenendo una rigorosa separazione dall’elettronica di potenza ad alta tensione.

- Metrica critica: l’induttanza di anello nel percorso di pilotaggio gate e il singolo fattore piu importante per efficienza di commutazione e interferenze elettromagnetiche (EMI).

- L’isolamento e essenziale: distanze corrette di creepage e clearance tra lato alta tensione (DC link/IGBT) e lato bassa tensione (MCU/DSP) sono irrinunciabili per la sicurezza.

- Gestione termica: anche le schede di controllo richiedono strategie termiche, soprattutto per i gate driver IC che pilotano carichi capacitivi elevati.

- Validazione: la simulazione non basta; occorrono double pulse test e termografia per verificare fisicamente il layout.

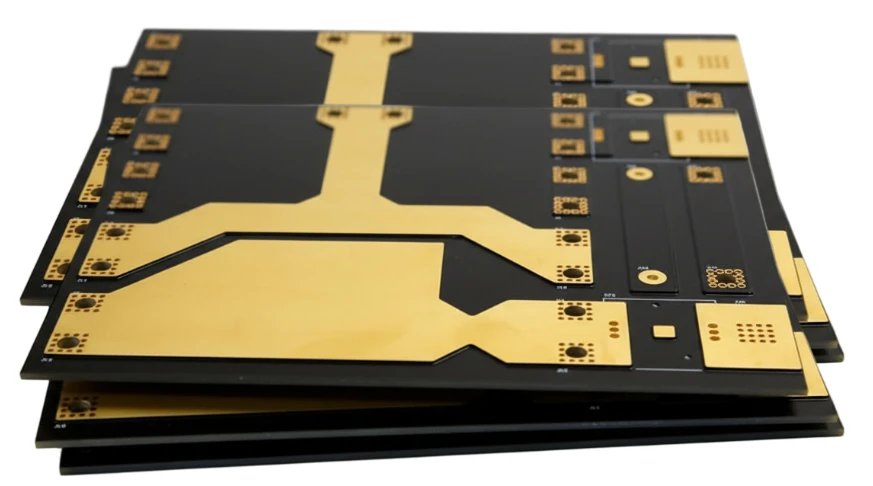

- Prontezza alla produzione: il DFM deve considerare requisiti di rame pesante e simmetria del stackup per evitare imbarcamenti.

Cosa significa davvero “PCB di controllo per inverter trifase” (ambito e confini)

Il termine layout PCB di controllo per inverter trifase indica la specifica disciplina ingegneristica che progetta il circuito stampato incaricato di gestire la commutazione di un inverter di potenza trifase. Mentre lo stadio di potenza gestisce la corrente principale, spesso nell’ordine di centinaia di ampere, il layout di controllo rappresenta il cervello e il sistema nervoso del sistema. Traduce la logica digitale, cioe i segnali PWM, in tensioni reali di pilotaggio gate e legge al tempo stesso i feedback analogici di corrente, tensione e temperatura.

Questa attivita di layout e particolare perche si colloca all’incrocio tra segnali digitali delicati ed eventi di commutazione ad alta tensione molto aggressivi. Un layout scarso non porta solo a una scheda poco funzionale; molto spesso provoca il guasto catastrofico dei moduli di potenza a causa di falsi trigger o sovratensioni.

In APTPCB (APTPCB PCB Factory) vediamo spesso progetti che in simulazione funzionano alla perfezione ma falliscono sul campo a causa di induttanze parassite nascoste nel layout del PCB. Questa guida copre il percorso che va dall’uscita del microcontrollore (MCU), attraversa la barriera di isolamento, arriva al gate driver e infine raggiunge l’interfaccia con gli interruttori di potenza, che si tratti di IGBT, MOSFET o dispositivi SiC/GaN.

Metriche che contano (come valutare la qualita)

Per capire se un layout PCB di controllo per inverter trifase e robusto bisogna misurare parametri fisici ed elettrici molto concreti. Sono queste metriche a distinguere un prototipo da una scheda pronta per la produzione.

| Metrica | Perche conta | Intervallo tipico o fattori influenti | Come misurare |

|---|---|---|---|

| Induttanza del gate loop | Un’induttanza elevata causa ringing, overshoot e commutazione piu lenta. | Obiettivo: < 10 nH. Influenzata da lunghezza pista e prossimita del ritorno. | Simulazione Q3D Extractor o osservazione dell’overshoot V_ds. |

| Common Mode Transient Immunity (CMTI) | Indica se l’isolatore resiste a rapide variazioni di tensione (dV/dt) senza corruzione dei dati. | > 50 kV/µs per Si; > 100 kV/µs per SiC/GaN. | Test con generatore di impulsi attraverso la barriera di isolamento. |

| Distanza di creepage | Evita tracciamento elettrico sulla superficie del PCB in presenza di umidita e inquinamento. | Dipende dalla tensione, per esempio 8 mm per sistemi a 400 V in pollution degree 2. | Misura fisica con calibro o verifica regole CAD. |

| Distanza di clearance | Evita scariche in aria tra reti di alta e bassa tensione. | Definita da IPC-2221 o IEC 60664-1. | Design Rule Check (DRC) in CAD. |

| Resistenza termica (Rth) | Garantisce che gate driver e regolatori non si surriscaldino durante la commutazione ad alta frequenza. | Dipende da spessore del rame e vias termici. | Termocamera sotto carico. |

| Rapporto segnale-rumore (SNR) | Critico per il feedback di misura di corrente verso le linee ADC. Il rumore provoca ripple di coppia nei motori. | Obiettivo: > 60 dB. Influenzato dalla separazione dei piani di massa. | Analisi con oscilloscopio delle linee analogiche di feedback. |

Scelte di progetto in base allo scenario (compromessi)

Applicazioni diverse richiedono approcci molto diversi nel design di un PCB di controllo per inverter trifase. Di seguito i casi piu comuni con i relativi compromessi.

1. Azionamenti motore a bassa tensione (12V - 48V)

- Contesto: utensili a batteria, e-bike, robotica.

- Compromesso: il vincolo principale e lo spazio.

- Indicazione: spesso e possibile integrare potenza e controllo su un unico PCB. Usare tecnologia Heavy Copper PCB per gestire la corrente in poco spazio. I requisiti di isolamento sono meno severi, quindi il posizionamento dei componenti puo essere piu compatto.

2. Azionamenti AC industriali (400V - 690V)

- Contesto: automazione industriale, pompe, ventilatori.

- Compromesso: affidabilita e sicurezza contano piu dell’ingombro.

- Indicazione: aderire rigorosamente a IEC 61800-5-1. Utilizzare una scheda di controllo dedicata separata dallo stadio di potenza, collegata tramite header o pin press-fit. Dare priorita a larghe fessure di creepage.

3. Inverter di trazione EV (alta densita di potenza)

- Contesto: trazione principale dei veicoli elettrici.

- Compromesso: vibrazione elevata e cicli termici estremi.

- Indicazione: usare materiali automotive-grade. Il layout deve sopportare dV/dt elevato, in particolare con SiC. Spesso servono substrati High Thermal PCB o design con cuore metallico per lo stadio driver, cosi da scaricare il calore nel sistema di raffreddamento.

4. Inverter solari (grid-tied)

- Contesto: conversione di energia fotovoltaica.

- Compromesso: efficienza e durata utile di oltre 20 anni.

- Indicazione: minimizzare le perdite nel gate drive per aumentare l’efficienza complessiva. Il layout deve considerare tensioni elevate del bus DC, fino a 1500 V, richiedendo barriere di isolamento importanti e talvolta conformal coating.

5. Driver GaN/SiC ad alta frequenza

- Contesto: alimentatori server, caricabatterie compatti.

- Compromesso: velocita di commutazione estremamente elevate contro EMI.

- Indicazione: l’induttanza di anello deve essere quasi nulla. Il driver deve essere posto fisicamente il piu vicino possibile all’interruttore. Spesso occorrono tecniche HDI per posizionare i driver direttamente sotto o sopra gli switch.

6. Elettrodomestici sensibili al costo

- Contesto: lavatrici, unita HVAC.

- Compromesso: costo contro prestazioni.

- Indicazione: le schede a uno o due strati sono comuni per contenere i costi. Questo rende difficile instradare bene i percorsi di ritorno. I progettisti devono applicare con estrema cura tecniche di massa a stella per evitare l’accoppiamento di rumore anche senza avere piani di massa completi.

Checkpoint di implementazione (dal progetto alla produzione)

Passare dallo schema elettrico alla scheda fisica richiede un processo disciplinato. Usare questa checklist per verificare che il proprio PCB di controllo per inverter trifase sia pronto per la produzione presso APTPCB.

Definizione del stackup:

- Raccomandazione: usare almeno 4 strati per inverter industriali (Segnale-Massa-Potenza-Segnale).

- Rischio: le schede a 2 strati spesso falliscono i test EMI per via di ritorni interrotti.

- Accettazione: verificare profili di impedenza e simmetria degli strati.

Posizionamento dei gate driver:

- Raccomandazione: posizionare i driver entro 10 mm dai pin del modulo di potenza o dalle gate dei MOSFET.

- Rischio: piste lunghe agiscono come antenne e aumentano l’induttanza.

- Accettazione: ispezione visiva della distanza.

Connessione Kelvin per la misura di corrente:

- Raccomandazione: instradare molto vicine le coppie differenziali delle resistenze di shunt.

- Rischio: il rumore di commutazione raccolto nel loop di feedback rende instabile il controllo.

- Accettazione: verificare il routing differenziale nel CAD.

Larghezza della barriera di isolamento:

- Raccomandazione: fresare una slot fisica sotto optoisolatori o isolatori digitali se la tensione supera 400 V.

- Rischio: carbonizzazione progressiva del PCB con conseguente cortocircuito.

- Accettazione: controllare i file Gerber per confermare i dati di fresatura.

Instradamento della protezione DESAT:

- Raccomandazione: mantenere la traccia DESAT corta e lontana da nodi ad alto dV/dt.

- Rischio: intervento falso della protezione da corto circuito.

- Accettazione: rivedere l’accoppiamento di rumore sul pin DESAT in simulazione.

Separazione dei piani di massa:

- Raccomandazione: separare chiaramente AGND, DGND e PGND e unirli in un solo punto tramite Net Tie.

- Rischio: i loop di massa iniettano rumore di potenza nel MCU.

- Accettazione: evidenziare le reti di massa nel CAD per verificare la separazione.

Decoupling dell’alimentazione:

- Raccomandazione: collocare condensatori a basso ESR immediatamente sui pin di alimentazione del gate driver.

- Rischio: droop di tensione durante il picco di corrente di carica della gate.

- Accettazione: verificare che i condensatori siano, quando possibile, sullo stesso strato dell’IC.

Revisione DFM:

- Raccomandazione: inviare i dati a un controllo DFM Guideline prima dell’ordine.

- Rischio: forature non producibili o acid trap.

- Accettazione: report di approvazione del fornitore.

Errori comuni (e approccio corretto)

Anche ingegneri esperti commettono errori nel design di PCB di controllo per inverter trifase. Questi sono i problemi che incontriamo piu spesso.

- Errore: far passare le piste di gate drive attraverso vias.

- Correzione: ogni via aggiunge circa 1,2 nH di induttanza. Mantenere il percorso di carica e scarica della gate ad alta corrente sul layer superiore, evitando cambi di strato quando possibile.

- Errore: ignorare il percorso del Miller Clamp.

- Correzione: il percorso che evita l’accensione parassita dovuta all’effetto Miller e importante quanto il percorso di turn-on. Deve quindi essere corto e largo.

- Errore: posizionare il sensore di temperatura lontano dal punto caldo.

- Correzione: i sensori NTC/PTC devono essere accoppiati termicamente al package dell’IGBT/MOSFET o alla parte piu calda del PCB, non semplicemente “vicino”.

- Errore: trascurare il bilanciamento del rame.

- Correzione: grandi aree di rame su un lato e poco rame sull’altro causano imbarcamento in reflow. Utilizzare copper thieving o pattern di bilanciamento per compensare.

- Errore: instradare segnali sensibili sotto il modulo di potenza.

- Correzione: non instradare mai linee ADC o di comunicazione su layer direttamente sotto i semiconduttori di potenza in commutazione. L’accoppiamento capacitivo iniettera rumore.

- Errore: serigrafia insufficiente.

- Correzione: marcare chiaramente le zone ad alta tensione. E un requisito di sicurezza per il personale di assemblaggio e collaudo.

FAQ

D: Quanti strati sono consigliati per un PCB di controllo di inverter trifase? R: Per azionamenti semplici a bassa tensione possono bastare 2 strati. Per drive industriali oltre 400 V, 4 strati sono lo standard per avere piani di massa solidi. Gli inverter EV complessi spesso usano 6 o piu strati.

D: Devo usare un piano di massa sotto il trasformatore o il coupler di isolamento? R: Assolutamente no. Bisogna rimuovere tutto il rame da tutti gli strati sotto i componenti della barriera di isolamento per mantenere creepage e clearance.

D: Quale peso di rame devo specificare? R: Per i segnali di controllo basta il classico 1 oz (35µm). Se pero la scheda trasporta anche la corrente principale, possono servire standard Industrial Control PCB con rame da 2 oz o 3 oz.

D: Come riduco le EMI nel layout? R: Ridurre al minimo l’area di anello dei percorsi con alto di/dt, in particolare gate drive loop e DC link loop. Usare un piano di massa continuo per la logica di controllo. Se gli obiettivi di efficienza lo permettono, rallentare i fronti di commutazione tramite resistori di gate.

D: Posso usare materiale FR4 per inverter ad alta tensione? R: Si. L’FR4 standard e adatto alla maggior parte degli inverter industriali fino a 1000 V, a condizione che il layout rispetti le regole di creepage. Per temperature continue molto alte, oltre 130°C, e consigliato un FR4 ad alto Tg.

D: Qual e il modo migliore per testare il layout prima della piena potenza? R: Iniziare con il double pulse test a tensioni piu basse. In questo modo si possono verificare le caratteristiche di commutazione e il ringing del gate driver senza rischiare l’intero stadio di potenza.

Pagine e strumenti correlati

- Heavy Copper PCB: essenziale quando la scheda di controllo gestisce anche una distribuzione di potenza significativa.

- Industrial Control PCB: capacita produttive specifiche per elettronica di controllo industriale robusta e ad alta affidabilita.

- DFM Guidelines: controllare il layout rispetto ai vincoli di fabbricazione prima dell’invio.

- Power & Energy PCB: soluzioni per inverter solari, eolici e grid-tied.

Glossario (termini chiave)

| Termine | Definizione |

|---|---|

| DC Link | La sorgente di tensione continua, spesso un banco di condensatori, che alimenta l’inverter. |

| IGBT | Insulated Gate Bipolar Transistor. Interruttore di potenza comune negli inverter ad alta tensione. |

| MOSFET | Metal-Oxide-Semiconductor Field-Effect Transistor. Utilizzato per inverter a tensione piu bassa o frequenza piu alta. |

| Gate Driver | IC che amplifica segnali logici a bassa potenza in impulsi di corrente elevata per pilotare le gate di IGBT/MOSFET. |

| Dead Time | Breve pausa tra lo spegnimento di un transistor e l’accensione dell’altro nello stesso ramo per evitare cortocircuiti. |

| PWM | Pulse Width Modulation. Metodo usato per codificare livelli analogici in impulsi digitali. |

| dV/dt | Velocita di variazione della tensione. Un dV/dt elevato puo accoppiare rumore attraverso le barriere di isolamento. |

| dI/dt | Velocita di variazione della corrente. Un dI/dt elevato genera picchi di tensione sulle induttanze parassite. |

| Connessione Kelvin | Metodo di misura a 4 fili usato per rilevare la tensione ai capi di un componente, come uno shunt, senza includere la caduta di tensione dei conduttori di potenza. |

| Creepage | La distanza piu breve tra due parti conduttive lungo la superficie dell’isolante. |

| Clearance | La distanza piu breve tra due parti conduttive attraverso l’aria. |

| EMI | Electromagnetic Interference. Rumore generato dalla commutazione che influenza altra elettronica. |

| EMC | Electromagnetic Compatibility. Capacita del dispositivo di funzionare senza causare ne subire EMI. |

Conclusione (prossimi passi)

Padroneggiare il layout PCB di controllo per inverter trifase significa bilanciare teoria elettrica, norme di sicurezza e vincoli fisici di fabbricazione. Un layout ben eseguito protegge il cervello digitale sensibile dalla forza della potenza e assicura efficienza e affidabilita.

Quando si e pronti a passare dal progetto al prototipo, APTPCB puo supportare il lavoro. Per ottenere un preventivo accurato e una revisione DFM completa, e utile fornire:

- File Gerber in formato RS-274X.

- Dettagli del stackup come peso del rame e spessore dielettrico.

- Specifiche del materiale come classe Tg e valore CTI per alta tensione.

- Requisiti speciali come fresatura di slot di isolamento, rame pesante o colori specifici della solder mask per migliorare il contrasto.

Se questi dettagli sono chiari, la produzione procede piu rapidamente e possiamo realizzare una scheda capace di soddisfare i requisiti severi dell’elettronica di potenza.