Advanced Engineering Guide

La realta ingegneristica della produzione di PCB ad alto numero di strati

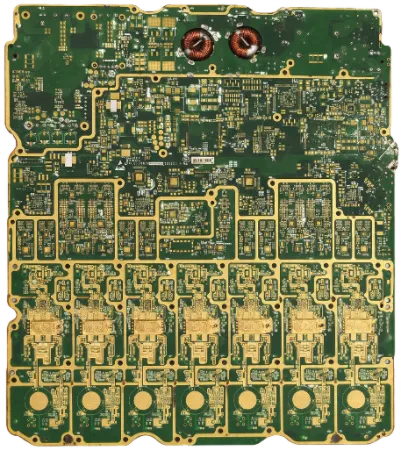

Progettare un backplane a 32 strati o una motherboard AI a 24 layer in un software ECAD e un complesso puzzle di routing, ma produrlo e una battaglia contro fisica, chimica e termodinamica. Con l'aumentare del numero di layer, il margine di errore si riduce in modo esponenziale. In APTPCB collaboriamo con hardware engineer senior di tutto il mondo per portare questi design estremi dal dominio digitale alla realta fisica. Di seguito trovi un'analisi approfondita degli ostacoli ingegneristici della fabbricazione ad alto numero di strati e di come li risolviamo.

1. La tirannia della registrazione e dello scaling dimensionale

La piu grande minaccia per una scheda ad alto numero di strati e il failure di registrazione. Un PCB viene costruito pressando layer alternati di core completamente curati e prepreg non curati sotto calore estremo e pressione idraulica. Durante questo processo di laminazione, i materiali si espandono e, quando la resina cura e si raffredda, si ritirano. Questo scaling dimensionale e anisotropo: si ritira in modo diverso nelle direzioni X e Y del tessuto in fibra di vetro.

In una scheda a 4 strati, un lieve spostamento puo essere assorbito facilmente dall'annular ring, cioe il pad in rame che circonda un foro forato. In una scheda a 40 strati, se i layer interni si spostano in modo incoerente, una punta meccanica che attraversa la scheda uscira inevitabilmente fuori dal pad di rame sulla Layer 25, interrompendo la connessione o causando un cortocircuito fatale verso un ground plane vicino.

La soluzione APTPCB: i nostri ingegneri CAM applicano fattori di scaling non lineari all'artwork di ogni singolo layer e prevedono matematicamente il tasso di ritiro in base alla densita di rame di quello specifico layer. Durante il layup utilizziamo sistemi di X-Ray induction bonding per allineare fisicamente i layer interni tra loro prima del ciclo di pressatura, garantendo una precisione di registrazione layer-to-layer di ±1.5 mil.

2. Metallizzazione ad alto aspect ratio: la sfida capillare

Con l'aumentare del numero di layer, la scheda diventa piu spessa. Una scheda a 32 strati puo facilmente raggiungere 5.0 mm (200 mil) di spessore. Se devi forare un via da 10 mil (0.25 mm) attraverso quella scheda, crei un tubo capillare microscopico con aspect ratio 20:1.

I sistemi standard di elettroplaccatura DC si basano sulla dinamica dei fluidi per far circolare bagni chimici ricchi di rame attraverso i fori. In un via 20:1 il fluido al centro del barrel ristagna. Gli ioni di rame si esauriscono e il processo di metallizzazione si interrompe, producendo un via con rame spesso in superficie ma pericolosamente sottile, o addirittura assente, al centro. Sotto il calore estremo del SMT reflow o del wave soldering, l'espansione lungo l'asse Z della scheda strappera facilmente quel barrel di rame sottile, causando circuiti aperti intermittenti notoriamente difficili da debuggare.

La soluzione APTPCB: per schede che superano un aspect ratio di 10:1 impieghiamo il Periodic Reverse Pulse Plating. Invece di una corrente continua costante, il sistema impulsa rapidamente la corrente in avanti e poi la inverte brevemente. L'impulso inverso agisce come una "pompa" elettrica, rimuovendo la chimica esaurita e trascinando fluido fresco ricco di rame fino al centro del via. Questo garantisce una parete del barrel uniforme e spessa, capace di sopravvivere a molteplici cicli di reflow lead-free.

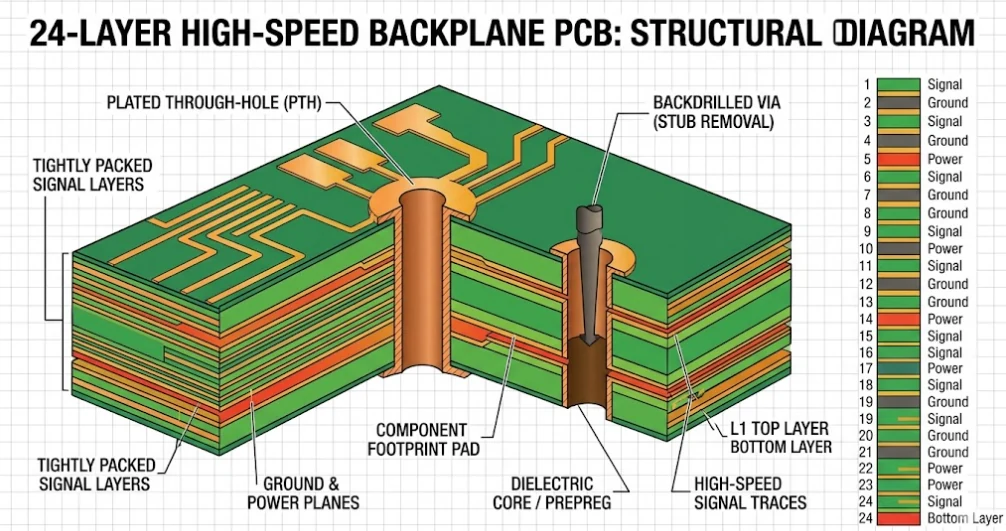

3. Eliminare la risonanza del segnale con backdrilling di precisione

Nelle architetture digitali high-speed, come PCIe Gen5, 100G/400G Ethernet e 112G PAM4, la geometria fisica del via diventa un componente RF attivo. Immagina un segnale che viaggia dalla Layer 1 alla Layer 5 in un backplane a 24 layer. Il segnale esce correttamente alla Layer 5, ma il barrel di rame residuo del via, che continua dalla Layer 6 fino alla Layer 24, agisce come un'antenna non terminata, cioe un "via stub". Questo stub riflette energia elettromagnetica nel canale, genera interferenza distruttiva e chiude il diagramma a occhio.

La soluzione APTPCB: per recuperare l'integrita del segnale utilizziamo il Controlled-Depth Backdrilling. Grazie a macchine di foratura CNC avanzate, dotate di tecnologia di surface sensing conduttivo, la punta entra dal lato inferiore della scheda (Layer 24) e rimuove lo stub di rame indesiderato, fermandosi con precisione prima di colpire il layer di segnale attivo (Layer 5). Raggiungiamo regolarmente precisioni di profondita di ±50μm, lasciando uno stub residuo innocuo inferiore a 8-10 mil e liberando cosi il canale dalle risonanze distruttive.

4. Gestione dell'impedenza in architetture spesse

In una scheda a 6 strati, una trace single-ended da 50Ω potrebbe richiedere una larghezza di 6 mil. In una scheda a 32 strati, poiche e necessario usare prepreg ultra-sottili, ad esempio da 2 mil, per mantenere gestibile lo spessore totale della scheda, la distanza tra la trace di segnale e il suo piano di riferimento si riduce drasticamente. Per mantenere gli stessi 50Ω, la larghezza della trace deve ridursi proporzionalmente, spesso fino a 2.5 o 3 mil.

Incidere una trace da 3 mil con tolleranza di impedenza ±5% richiede una padronanza chimica assoluta. La soluzione APTPCB: utilizziamo Laser Direct Imaging (LDI) per ottenere precisione di esposizione sub-mil, abbinata a linee di incisione assistite dal vuoto che estraggono l'acido tra trace molto ravvicinate per prevenire l'undercut. Modelliamo ogni struttura di impedenza in Polar Si9000 e verifichiamo fisicamente il risultato tramite coupon TDR su ogni pannello di produzione.