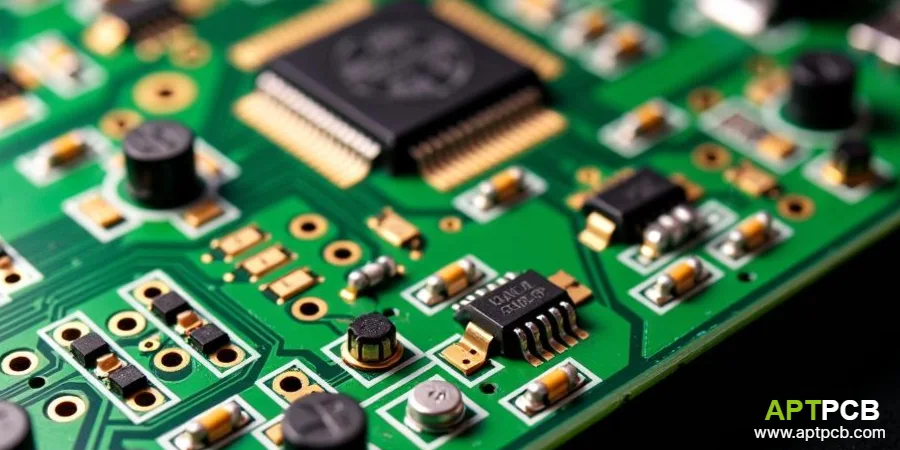

Le telecamere di visione artificiale acquisiscono immagini per ispezione automatizzata, guida e misura con frequenze di fotogramma che vanno da pochi Hz a diverse migliaia di frame al secondo. Il PCB deve collegare i sensori di immagine, elaborare e trasferire gigabyte di dati al secondo e reagire a trigger esterni con precisione al microsecondo, il tutto entro i vincoli termici e meccanici di custodie compatte.

Questa guida riassume le scelte di progettazione PCB che determinano prestazioni e affidabilità delle telecamere di visione artificiale negli ambienti industriali.

In questa guida

- Progettazione dell’interfaccia del sensore di immagine

- Architettura del percorso dati ad alta velocità

- Trigger e sincronizzazione

- Gestione dell’alimentazione per sensori

- Gestione termica in custodie compatte

- Implementazione dell’interfaccia industriale

Progettazione dell’interfaccia del sensore di immagine

I sensori di immagine CMOS trasmettono dati tramite interfacce LVDS parallele, MIPI CSI-2 o Sub-LVDS a velocità che possono raggiungere diversi gigabit al secondo. L’interfaccia PCB deve preservare l’integrità del segnale dal sensore all’FPGA o al processore mediante routing a impedenza controllata e corrispondenza delle lunghezze molto rigorosa.

Le interfacce sensore LVDS usano più coppie differenziali per trasportare clock e dati a velocità da 200 Mbps a 1 Gbps per corsia. Lo skew tra corsie dati e clock influisce direttamente sull’affidabilità di acquisizione; i requisiti tipici limitano lo skew corsia-corsia a 0,1 UI (intervallo unitario), che in pratica corrisponde a pochi millimetri di differenza di lunghezza sulle piste ad alta velocità.

Le interfacce MIPI CSI-2 forniscono collegamenti standardizzati ad ampia banda, ma richiedono particolare attenzione al controllo dell’impedenza e alla terminazione. Le buone pratiche PCB per queste interfacce comprendono routing a impedenza controllata, transizioni via ben progettate e continuità del percorso di ritorno.

Requisiti dell’interfaccia del sensore

- Controllo dell’impedenza: 100 Ω differenziale per LVDS; 85-100 Ω differenziale per MIPI CSI-2 in base alla versione della specifica.

- Corrispondenza delle lunghezze: Matching intra-coppia entro 2 mil; matching corsia-corsia secondo i requisiti di temporizzazione del sensore.

- Piani di riferimento: Piani di riferimento continui sotto le piste ad alta velocità; transizioni via controllate.

- Terminazione: Terminazione on-die comune nei sensori; terminazione esterna se richiesta dalla specifica dell’interfaccia.

- Filtraggio dell’alimentazione: Separare le alimentazioni analogiche e digitali del sensore con filtraggio adeguato.

- Montaggio del sensore: Allineamento controllato tra sensore e scheda per garantire precisione ottica.

Architettura del percorso dati ad alta velocità

I dati immagine scorrono dal sensore, attraversano l’elaborazione FPGA e raggiungono l’interfaccia di uscita a velocità sostenute di diversi gigabit al secondo. Un sensore da 5 megapixel a 100 fps con profondità di 10 bit genera 5 Gbps di dati continui. I percorsi dati sul PCB devono sostenere questa banda senza introdurre problemi termici né compromettere l’integrità del segnale.

La scelta dell’FPGA deve bilanciare larghezza di banda I/O, risorse di elaborazione e consumo energetico. I ricetrasmettitori seriali ad alta velocità, da 5 a 10 Gbps per canale, supportano uscite Camera Link, CoaXPress o 10GigE. Lo stackup PCB multistrato deve supportare più interfacce ad alta velocità gestendo il crosstalk e mantenendo il controllo dell’impedenza.

Le interfacce di memoria per i frame buffer aggiungono ulteriore routing ad alta velocità. Le interfacce DDR3/DDR4 richiedono attenzione particolare al timing, mentre opzioni più recenti come HyperRAM o LPDDR4x possono semplificare il routing mantenendo banda sufficiente per molte applicazioni.

Progettazione del percorso dati

- Pianificazione I/O FPGA: Raggruppare le interfacce correlate nello stesso bank FPGA; pianificare le alimentazioni secondo i requisiti di ciascun bank.

- Interfaccia di memoria: I vincoli di timing DDR guidano l’assegnazione dei layer PCB e le regole di routing.

- Routing ad alta velocità: Microstrip sul top layer; stripline sui layer interni con accoppiamento controllato.

- Transizioni via: Via back-drilled o via ciechi/interrati per minimizzare gli stub sui segnali multigigabit.

- Integrità dell’alimentazione: La rete PDN deve supportare le richieste di corrente transitoria di FPGA e memoria.

- Budget di crosstalk: Spaziatura e schermatura devono mantenere il crosstalk sotto i margini di rumore dell’interfaccia.

Trigger e sincronizzazione

Le applicazioni di visione artificiale richiedono spesso una temporizzazione precisa tra acquisizione dell’immagine ed eventi esterni, come luci stroboscopiche, posizione del pezzo o comandi del motion controller. La telecamera deve rispondere agli ingressi trigger con una latenza minima nota e può dover sincronizzare più telecamere per imaging stereo o multi-view.

I circuiti di ingresso trigger devono respingere il rumore elettrico tipico degli ambienti di fabbrica mantenendo al tempo stesso una risposta rapida. L’isolamento tramite optoisolatore protegge l’elettronica della telecamera, ma aggiunge ritardo di propagazione; gli isolatori digitali ad alta velocità offrono una risposta più rapida quando l’isolamento è necessario. Il filtraggio in ingresso deve lasciar passare i fronti di trigger validi e respingere il rumore.

La sincronizzazione dei frame tra più telecamere utilizza distribuzione hardware del trigger oppure IEEE 1588/PTP. Per mantenere clock puliti ed escape brevi attorno a PHY e connettori a passo fine, molti progetti traggono vantaggio dalla fabbricazione di PCB HDI.

Progettazione del sistema di trigger

- Caratteristiche di ingresso: Intervallo di ingresso tipico 5-24 V per compatibilità industriale; polarità del fronte configurabile.

- Debounce: Debounce hardware o firmware per eliminare il rimbalzo dei contatti senza ritardi eccessivi.

- Specifica di latenza: Latenza trigger-esposizione documentata con specifica di jitter.

- Opzioni di isolamento: Optoisolatore o isolatore digitale per protezione dai loop di massa.

- Uscita strobo: Uscita strobo sincronizzata con offset temporale programmabile.

- Sincronizzazione multi-camera: Distribuzione hardware del trigger o correlazione timestamp PTP.

Gestione dell’alimentazione per sensori

Le alimentazioni del sensore di immagine influiscono direttamente sulla qualità dell’immagine. Il rumore sulle linee analogiche appare come rumore a pattern fisso nelle immagini acquisite; il ripple di alimentazione a determinate frequenze crea artefatti a bande visibili. La distribuzione di potenza sul PCB deve fornire alimentazioni pulite e stabili per raggiungere le specifiche del sensore.

I sensori di immagine di grandi dimensioni consumano 1-3 W, generando riscaldamento localizzato che influisce su corrente di buio e rumore. I requisiti di power sequencing imposti dal produttore devono essere seguiti con precisione; una sequenza errata può danneggiare il sensore o provocare latch-up. La progettazione dell’elettronica di potenza deve quindi soddisfare sia i requisiti di qualità dell’alimentazione sia quelli di sequenziamento.

Le telecamere Power-over-Ethernet (PoE) ricavano l’alimentazione operativa direttamente dal collegamento Ethernet, eliminando un cablaggio di alimentazione separato. Il PCB deve includere un’interfaccia PoE PD (powered device) con conversione CC-CC isolata per soddisfare i requisiti di alimentazione del sensore.

Progettazione dell’alimentazione per sensori di immagine

- Rumore di alimentazione: Le linee analogiche richiedono <10 mVpp di ripple; per telecamere scientifiche valgono specifiche ancora più severe.

- LDO vs switching: Gli LDO offrono rumore più basso; lo switching è accettabile con filtraggio adeguato.

- Sequenziamento: Sequenziamento conforme alla scheda tecnica del sensore; sequenziamento supervisionato per requisiti complessi.

- Capacità bulk: Capacità sufficiente per sostenere la corrente transitoria durante la lettura del sensore.

- Coordinamento termico: La posizione della dissipazione di potenza influenza l’ambiente termico del sensore.

- Integrazione PoE: Interfaccia IEEE 802.3af/at PD con conversione CC-CC isolata per telecamere PoE.

Gestione termica in custodie compatte

Le telecamere di visione artificiale racchiudono elettronica con dissipazione significativa, tipicamente 10-25 W per una telecamera industriale, in custodie compatte che possono non avere ventilazione. La progettazione termica del PCB deve convogliare il calore verso le superfici della custodia per dissiparlo, mantenendo al tempo stesso la temperatura del sensore entro i limiti operativi.

La temperatura del sensore di immagine influisce direttamente sulle prestazioni di rumore. La corrente di buio raddoppia circa ogni 6-8 °C, aumentando il fondo di rumore a temperature elevate. Le applicazioni critiche possono richiedere raffreddamento attivo tramite TEC per mantenere costante la temperatura del sensore; il PCB deve quindi supportare alimentazione del TEC e monitoraggio termico.

La progettazione termica del PCB deve bilanciare le esigenze di diffusione del calore con l’integrità del segnale ad alta velocità. Piani di rame più pesanti migliorano la conduttività termica, ma possono alterare l’impedenza controllata; solo uno stackup ben studiato permette di soddisfare insieme i requisiti termici ed elettrici.

Approcci di progettazione termica

- Diffusione termica: I piani di rame conducono il calore dalle fonti localizzate verso le aree di contatto con la custodia.

- Interfaccia termica: Pad termici o gap filler trasferiscono calore dal PCB alla custodia.

- Posizionamento dei componenti: I componenti caldi devono essere collocati lungo percorsi termici efficaci; i circuiti sensibili vanno mantenuti in zone più fredde.

- Percorso termico del sensore: Percorso termico dedicato dal sensore alla custodia, eventualmente tramite supporto metallico.

- Supporto TEC: Circuiti di pilotaggio TEC e monitoraggio della temperatura per sensori raffreddati.

- Considerazione del flusso d’aria: Nelle telecamere ventilate, il posizionamento dei componenti deve tenere conto del flusso d’aria.

Implementazione dell’interfaccia industriale

Le telecamere di visione artificiale si collegano ai sistemi host tramite interfacce GigE Vision, Camera Link, CoaXPress o USB3 Vision. Ciascuna di queste interfacce impone requisiti PCB specifici in termini di integrità del segnale, scelta dei connettori e distribuzione della potenza.

Le telecamere GigE Vision utilizzano un PHY Ethernet standard con magnetics e connettori di grado industriale. Connettori M12 o RJ45 con bloccaggio meccanico e ritenzione del cavo devono resistere a vibrazioni e trazione sul cablaggio. Il layout di PHY e trasformatore segue le regole della fabbricazione di PCB ad alta velocità per garantire integrità del segnale ed EMC.

Le telecamere CoaXPress trasmettono video ad ampia banda su cavo coassiale fornendo allo stesso tempo potenza sul medesimo cavo. L’interfaccia PCB comprende un serializzatore ad alta velocità, un driver coassiale e la circuiteria di estrazione della potenza PoCXP.

Implementazione dell'interfaccia

- GigE Vision: PHY Ethernet industriale; connettori M12 o RJ45 bloccabili; isolamento 1500 Vrms.

- Camera Link: Interfaccia LVDS parallela; connettori MDR26 o SDR26; equalizzazione del cavo per tratte lunghe.

- CoaXPress: SERDES ad alta velocità; connettore e driver coassiali; estrazione di potenza per PoCXP.

- USB3 Vision: Controller USB 3.0; connettori USB con bloccaggio a vite per ritenzione industriale.

- Interfaccia GPIO: I/O digitale isolato per ingresso trigger e uscita strobo.

- Interfaccia di configurazione: Interfaccia seriale per configurazione della telecamera e aggiornamento firmware.

Riepilogo

La progettazione PCB per telecamere di visione artificiale integra interfacce sensore ad alta velocità, percorsi dati gigabit, temporizzazione precisa e gestione termica in sistemi compatti che devono operare in modo affidabile negli ambienti industriali. La combinazione di sfide legate a integrità del segnale, qualità dell’alimentazione e limiti termici in volumi ridotti crea una complessità progettuale che richiede ingegneria coordinata tra più discipline. Il successo dipende dalla capacità di tradurre i requisiti di qualità dell’immagine in specifiche PCB e tolleranze di produzione realistiche.