Le main board delle Smart TV integrano elaborazione applicativa, scaling e processing video, molteplici interfacce ad alta velocita come HDMI, USB ed Ethernet, connettivita wireless e sistemi audio su schede che devono rispettare obiettivi di costo molto aggressivi offrendo al tempo stesso un'esperienza visiva premium. Le sfide di progettazione del PCB spaziano dalle interfacce HDMI 2.1 ad altissima velocita, con 48 Gbps aggregati, fino alle interfacce di pilotaggio dei grandi pannelli e all'integrazione dell'alimentazione.

Questa guida affronta gli aspetti specificamente PCB del design Smart TV: la suddivisione tra main board e T-CON, i requisiti di routing del SoC video, l'integrita del segnale HDMI 2.1, il progetto dell'interfaccia verso il pannello, l'architettura della potenza e il bilanciamento tra qualita e ottimizzazione dei costi di produzione che e fondamentale nei prodotti televisivi.

Design Checklist (Fast Pass)

- Partizionare presto: definire main board vs. T-CON vs. PSU board e bloccare in anticipo interconnessione e scelta del connettore.

- Posizionare HDMI vicino: mantenere corte le tratte HDMI 2.1 FRL; prevedere da subito footprint per ESD, CMC e retimer.

- Trattare la DDR come un sistema: stackup, impedenza, matching delle lunghezze, piani di riferimento e percorsi di ritorno vanno progettati insieme.

- Progettare PDN e termica insieme: rame, array di via e diffusione termica verso il telaio fanno parte del vero power design.

- Usare il DFM per il costo: evitare HDI dove non serve; ottimizzare sfruttamento del pannello e accesso al test.

In This Guide

- Architettura della scheda TV: partizione tra main board e T-CON

- Requisiti di routing del SoC di video processing

- Implementazione dell'interfaccia ad alta velocita HDMI 2.1

- Progettazione dell'interfaccia di timing del pannello

- Integrazione dell'alimentazione e considerazioni termiche

- Produzione ottimizzata nei costi per i prodotti TV

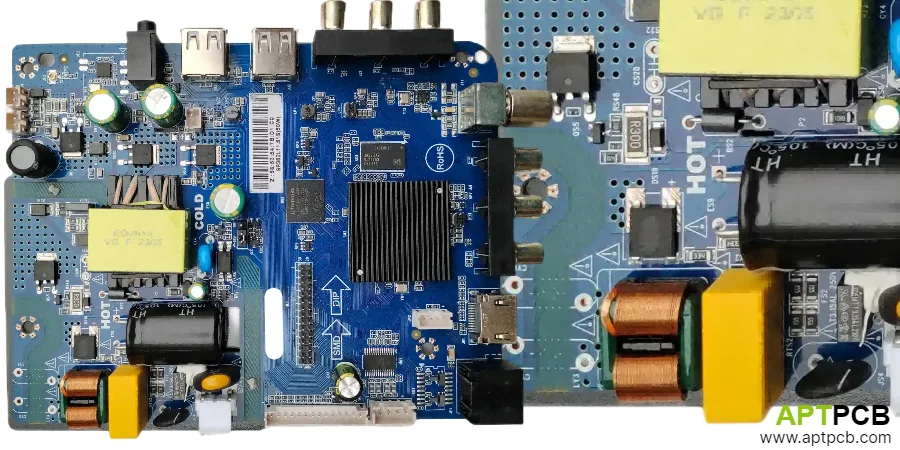

TV Board Architecture: Main Board and T-CON Partitioning

L'elettronica di una Smart TV e normalmente distribuita su piu PCB: la main board gestisce elaborazione applicativa, connettivita e ingresso ed elaborazione video; la scheda T-CON, timing controller, gestisce il pilotaggio del pannello e l'ottimizzazione dell'immagine; la scheda di alimentazione fornisce invece i diversi rail di tensione. Questa suddivisione risponde sia a esigenze funzionali sia a logiche di supply chain, perche pannelli diversi richiedono T-CON diversi, mentre le main board vengono spesso standardizzate su piu linee prodotto.

L'interfaccia tra main board e T-CON trasporta video gia completamente elaborato fino a risoluzioni 8K. Questo impone o interfacce parallele a banda estremamente elevata, con LVDS che richiede decine di coppie, oppure protocolli seriali come V-by-One ed eDP, che riducono il numero di conduttori ma richiedono integrita del segnale multi-gigabit. Questa interfaccia board-to-board determina spesso il limite superiore delle prestazioni video dell'intero sistema.

Board Partitioning Considerations

- Perimetro della main board: SoC, memoria, ricevitori HDMI, interfacce USB ed Ethernet, moduli WiFi e Bluetooth, elaborazione audio e interfacce verso T-CON e schede di alimentazione.

- Livello di integrazione del T-CON: Alcuni pannelli integrano il T-CON direttamente nel pannello, altri usano una scheda T-CON separata; questo cambia i requisiti di interfaccia della main board.

- Selezione dell'interfaccia: E la specifica del pannello a guidare la scelta. Molti design 4K60 usano V-by-One HS con circa 8 lane nella classe di circa 3-4 Gbps per lane; l'8K richiede in genere piu lane, velocita superiori o un'altra interfaccia.

- Tipi di connettore: Le interfacce ad alta velocita richiedono connettori specializzati che mantengano il matching di impedenza; i cavi flat limitano la banda e vanno gestiti con attenzione.

- Distribuzione di potenza: La main board puo alimentare il T-CON, aumentando cosi la gestione di corrente sulla scheda principale, oppure il T-CON puo ricevere alimentazione direttamente dalla PSU board.

- Layout fisico: La main board viene montata di solito nella parte inferiore posteriore dello schermo; i vincoli termici richiedono distanza dal pannello e percorsi di ventilazione adeguati.

Capire l'architettura di sistema aiuta a prendere decisioni di partizionamento PCB che impattano direttamente sia le prestazioni elettriche sia l'efficienza produttiva.

Video Processing SoC Routing Requirements

I SoC per Smart TV integrano una complessita notevole: processori applicativi quad-core o octa-core, decoder video dedicati per piu codec a risoluzione 4K o 8K, motori display con scaling e miglioramento immagine e numerose interfacce. Questi dispositivi altamente integrati arrivano in package BGA grandi, spesso con 500 fino a oltre 1000 pin, e pitch fini da 0,4 a 0,65 mm. Il routing deve quindi garantire prestazioni elevate senza compromettere la producibilita.

Le interfacce di memoria sono particolarmente critiche. DDR4 o LPDDR4/5 lavorano a velocita che richiedono matching accurato delle lunghezze e controllo dell'impedenza. A differenza degli smartphone, dove la memoria e spesso in package-on-package, nei TV il SoC usa di solito memoria discreta, quindi l'intero problema di integrita del segnale si sposta sul routing di scheda.

SoC Routing Guidelines

- Strategia di fanout del BGA: I BGA a passo fine richiedono via-in-pad o fanout dog-bone; i via passanti limitano i canali di routing, quindi i blind via possono essere utili nei package piu densi.

- Routing della memoria: DDR4 a 2666-3200 MT/s richiede matching di lunghezza entro ogni byte lane pari a ±5 mm, matching DQS-DQ di ±10 mm e impedenza coerente.

- Requisiti sui piani di riferimento: I segnali di memoria e le interfacce veloci richiedono reference plane continui; bisogna evitare piste di potenza o via nelle aree di piano sotto i segnali critici.

- Strategia di decoupling: I pin di alimentazione del SoC richiedono decoupling locale, per esempio 100 nF su ciascun cluster di pin, piu capacita bulk da 10 a 100 uF nelle vicinanze. I condensatori vanno posizionati il piu vicino possibile ai pin.

- Accesso JTAG e debug: Interfacce di debug come JTAG e UART devono restare accessibili per sviluppo e test di produzione; occorre prevedere test point o header in posizioni adeguate.

- Progetto termico: La dissipazione del SoC, tipicamente 5-15 W, richiede via termici sotto il package e sufficiente distribuzione di rame verso i punti di contatto con dissipatore o telaio.

Il routing dei SoC video trae beneficio da tecniche di high-speed PCB design per assicurare margini adeguati alle interfacce di memoria e display.

HDMI 2.1 High-Speed Interface Implementation

HDMI 2.1 e una delle specifiche di interfaccia consumer piu impegnative. Con 12 Gbps per lane su quattro lane dati, quindi 48 Gbps aggregati, supporta 8K a 60 Hz oppure 4K a 120 Hz con HDR. Il routing tra il ricevitore HDMI e il connettore deve preservare l'integrita del segnale a frequenze in cui la lunghezza d'onda diventa paragonabile alla lunghezza delle tracce, rendendo indispensabile una rigorosa disciplina di transmission line.

Le vecchie versioni HDMI 1.4 e 2.0, fino a 18 Gbps aggregati, usavano segnalazione differenziale con terminazione in sorgente e tolleranze d'impedenza piu moderate. HDMI 2.1 FRL, Fixed Rate Link, alza in modo netto il livello: 100 ohm differenziali (±10%), lunghezze strettamente abbinate dentro ogni coppia differenziale e controllo di insertion loss e return loss sull'intero canale, cioe connettore, PCB e cavo.

HDMI 2.1 Routing Requirements

- Controllo d'impedenza: 100 ohm differenziali ±10%; coppie differenziali strettamente accoppiate riducono l'EMI e mantengono il common-mode rejection.

- Perdita di canale: A 12 Gbps per lane il margine di perdita si esaurisce rapidamente. Le tracce vanno tenute corte; se questo non e possibile, conviene valutare laminati low-loss e/o redriver o retimer.

- Vincoli di lunghezza: Le tracce HDMI vanno mantenute il piu corte possibile; restare sotto 50 mm riduce perdita e accumulo di skew, quindi e importante collocare il connettore vicino al receiver IC.

- Scelta del layer: E preferibile instradare HDMI su layer adiacenti a solid ground plane; il microstrip su layer esterni e accettabile se l'EMI e gestita, mentre la stripline garantisce una schermatura migliore.

- Transizioni tramite via: Se possibile vanno evitate. Quando sono inevitabili, bisogna minimizzare gli stub, per esempio con backdrill dove ha senso, e mantenere continuita nei piani di riferimento.

- Protezione ESD: Le porte HDMI richiedono protezione ESD. Il posizionamento del dispositivo influisce direttamente sull'integrita del segnale, quindi servono TVS a bassa capacita, sotto 0,3 pF, poste a ridosso del connettore.

Per HDMI 2.1 puo essere necessaria una simulazione di signal integrity per verificare che il routing mantenga margini di conformita adeguati, soprattutto con tracce lunghe o con FR-4 standard.

Panel Timing Interface Design

L'interfaccia tra main board, o T-CON, e pannello LCD o OLED trasporta dati video a velocita imposte dal pixel clock e dalla profondita colore. Un pannello 4K a 60 Hz con colore a 10 bit richiede circa 17 Gbps di dati video, veicolati tramite LVDS, V-by-One o interfacce proprietarie in funzione del produttore del pannello e della risoluzione.

V-by-One HS domina le implementazioni attuali dei TV 4K. Usa meno lane rispetto a LVDS, tipicamente 8 coppie invece di 16-32 coppie, ma a velocita superiori, in genere 3,6-4,0 Gbps per lane. Il numero ridotto di lane semplifica il routing, ma aumenta i requisiti di integrita del segnale per ogni singola lane. I collegamenti flex verso il pannello introducono inoltre discontinuita di impedenza che devono essere gestite con la scelta del connettore e con il design di terminazione sul PCB.

Panel Interface Implementation

- Scelta del protocollo: La specifica del pannello detta l'interfaccia. V-by-One HS e comune sulla maggior parte dei pannelli 4K; LVDS resta diffuso alle risoluzioni inferiori; alcuni pannelli 8K usano interfacce proprietarie ad alta velocita.

- Configurazione delle lane: V-by-One HS usa tipicamente 8 lane per 4K 60 Hz a 10 bit; il numero cresce con risoluzione, refresh rate e profondita colore.

- Interfaccia del connettore: I connettori verso il pannello devono mantenere il matching di impedenza; il cavo flex tra scheda e pannello introduce perdita e skew che limitano il bit rate massimo raggiungibile.

- Clock di riferimento: Le interfacce pannello richiedono clock di riferimento stabili; scelta di quarzo o oscillatore, filtraggio dell'alimentazione e isolamento del routing influenzano il jitter.

- Design di terminazione: La terminazione on-chip e lo standard per i ricevitori V-by-One; bisogna comunque verificare i requisiti di terminazione in ingresso del pannello e l'impedenza di uscita della sorgente.

- Considerazioni EMI: I segnali del pannello possono irradiare dai cavi flex; grounding corretto del connettore, schermatura del cavo e distanza dai circuiti sensibili riducono l'impatto EMI.

La progettazione dell'interfaccia pannello richiede stretto coordinamento con il fornitore del pannello per verificare timing, livelli di tensione e compatibilita dei connettori.

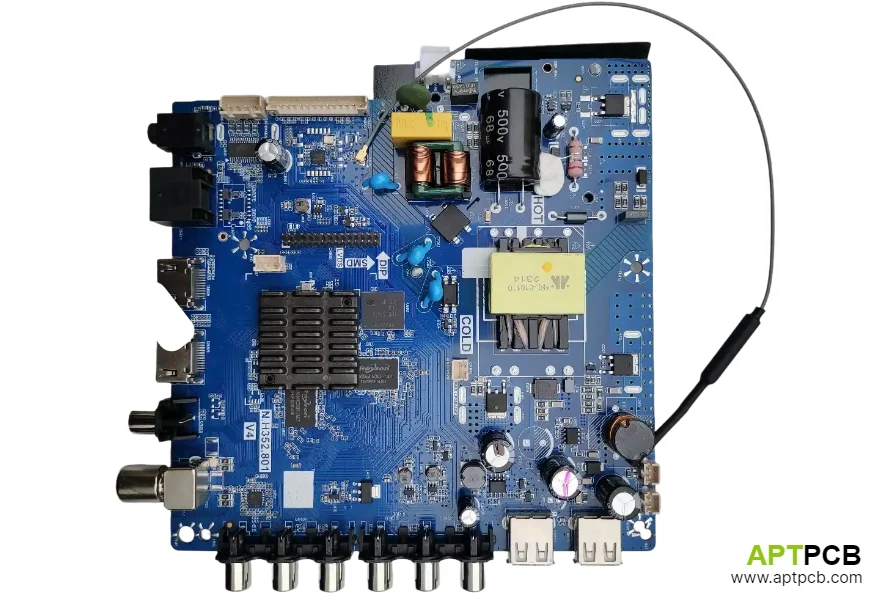

Power Supply Integration and Thermal Considerations

Le main board delle Smart TV ricevono tipicamente 5 V o 12 V dalla scheda di alimentazione e generano localmente i rail necessari per il SoC, di solito 0,9-1,1 V per il core piu tensioni I/O, per la memoria, circa 1,2 V in DDR4 o LPDDR4, e per altri sottosistemi. Il power delivery network deve supportare i transitori di corrente del SoC mantenendo la regolazione di tensione entro tolleranze strette, tipicamente ±3 % sui rail core.

La gestione termica di una main board TV e diversa da quella dei dispositivi portatili. L'area di scheda piu ampia aiuta la diffusione del calore, ma un telaio chiuso e la preferenza per funzionamento fanless limitano il raffreddamento. Il PCB agisce quindi sia da substrato meccanico sia da heat spreader primario, con il calore che viene trasferito al telaio metallico tramite thermal interface materials.

Power and Thermal Design

- Efficienza DC-DC: I convertitori buck multiphase per il SoC raggiungono oltre il 90 % di efficienza; la scelta di induttori e MOSFET influisce sia sul rendimento sia sul comportamento termico.

- Sequenziamento delle tensioni: Il SoC richiede una specifica sequenza di accensione, tipicamente core, poi I/O e infine memoria. Un sequencing controller o un PMIC integrato assicura il corretto timing.

- Rete di decoupling: Il PDN del SoC richiede capacita bulk, come MLCC, polimerici o elettrolitici, oltre a ceramici a media e alta frequenza distribuiti sulla rete.

- Copertura di rame: Conviene massimizzare i copper pour sugli inner layer sotto SoC e stadi di conversione; rame da 1 oz o 2 oz sui power layer migliora sia la portata di corrente sia la diffusione termica.

- Array di via termici: Array densi di via sotto il SoC e i MOSFET di potenza conducono il calore agli strati interni e alla superficie opposta; i via riempiti evitano il risucchio della saldatura in assembly.

- Interfaccia col dissipatore: Le aree termiche della main board si accoppiano al telaio tramite thermal interface materials; rame piano e continuo offre un'interfaccia termica uniforme ed e meglio evitare rilievi dovuti ai via nell'area di contatto.

L'interazione tra alimentazione e termica richiede comprensione sia dei principi dell'elettronica di potenza sia delle strategie di thermal management dell'elettronica consumer.

Cost-Optimized Manufacturing for Television Products

I prodotti televisivi operano sotto una pressione estrema sui costi. Il mercato si aspetta TV 4K di grande formato a prezzi che impongono una forte ottimizzazione lungo tutto il progetto. Il costo del PCB pesa in modo significativo sul BOM totale, quindi selezione dei materiali, numero di layer e utilizzo del pannello sono scelte di progetto cruciali. La qualita pero non puo essere sacrificata, perche i costi di garanzia dovuti a guasti sul campo superano rapidamente i risparmi di produzione.

Trovare il giusto equilibrio tra costo e qualita richiede decisioni attente: usare materiali standard dove le prestazioni lo consentono, ridurre il numero di layer senza compromettere la funzionalita, ottimizzare il contorno scheda per sfruttare meglio il pannello e progettare pensando al rendimento di fabbricazione. Coinvolgere presto il partner produttivo aiuta a individuare opportunita di risparmio che preservano la qualita.

Cost Optimization Strategies

- Scelta dei materiali: FR-4 standard con Tg 140-150 C e sufficiente per la maggior parte delle applicazioni TV; materiali ad alta velocita solo dove HDMI 2.1 o altre interfacce critiche li richiedano davvero.

- Riduzione dei layer: Una costruzione a 6 layer si adatta a molte main board TV; 4 layer possono bastare in design meno complessi con routing particolarmente curato.

- Utilizzo del pannello: Schede rettangolari con dimensioni standardizzate sfruttano meglio il pannello produttivo; forme custom riducono l'utilizzo e aumentano il costo unitario.

- Ottimizzazione dei via: I via passanti costano molto meno di blind e buried via; conviene quindi progettare through-hole dove possibile e riservare le strutture HDI alle aree davvero necessarie.

- Finitura superficiale: HASL resta l'opzione piu economica per componenti through-hole o a passo largo; ENIG offre una superficie piana per il fine-pitch ma costa di piu.

- Copertura di test: Un design for test con test point accessibili riduce i costi delle attrezzature e migliora l'individuazione dei difetti; il flying-probe e adatto a volumi moderati.

Le partnership per produzione PCB in volume permettono di ottimizzare i costi tramite efficienza di processo e prezzi di volume mantenendo i controlli di qualita.

Technical Summary

La progettazione del PCB di una Smart TV deve bilanciare requisiti avanzati di integrita del segnale, come HDMI 2.1 e le interfacce pannello ad alta velocita, con gli obiettivi di costo molto aggressivi tipici dei prodotti TV consumer. Il successo dipende da decisioni architetturali solide, come partizionamento delle schede, scelta delle interfacce e specifica dei materiali, che consentano di raggiungere le prestazioni richieste senza gonfiare il costo totale di sistema.

Tra le decisioni tecniche piu importanti rientrano la strategia di implementazione HDMI, con effetti su lunghezza delle tracce, materiali e gestione EMI, la compatibilita dell'interfaccia pannello, cioe protocollo e connettore, l'architettura della distribuzione di potenza in termini di efficienza e risposta ai transitori, e la soluzione termica, in cui il PCB partecipa direttamente al raffreddamento del sistema.

La scelta del partner produttivo deve considerare sia la capacita tecnica, come routing ad alta velocita e qualita dei multilayer, sia la competitivita di costo. I volumi tipici del mercato TV giustificano spesso ottimizzazioni produttive che non sarebbero sostenibili su prodotti a basso volume. Anche con una forte pressione sul costo, i sistemi qualita restano indispensabili, perche i costi di garanzia da difetti di fabbricazione superano rapidamente il risparmio ottenuto in produzione.