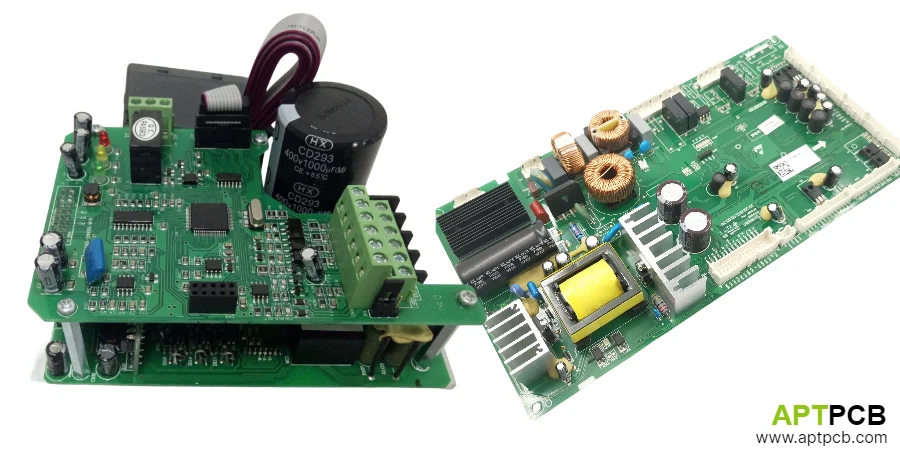

I variatori di frequenza convertono una sorgente CA a frequenza fissa in un'uscita a frequenza e tensione variabili, cosi da controllare con precisione la velocita del motore. Il PCB deve gestire potenze nell'ordine dei kilowatt attraverso stadi di commutazione ad alta tensione e, nello stesso tempo, preservare l'integrita del segnale necessaria a un controllo accurato. Tutto questo deve avvenire entro limiti EMC che evitino interferenze sulle apparecchiature circostanti.

Questa guida tratta gli aspetti di progettazione a livello PCB che determinano affidabilita, efficienza e compatibilita elettromagnetica di un VFD in ambito industriale.

In questa guida

- Layout dello stadio di potenza e isolamento

- Progettazione del circuito gate driver

- Misura di corrente e tensione

- Architettura di filtraggio EMC

- Gestione termica per l'elettronica di potenza

- Integrazione dell'interfaccia di controllo

Layout dello stadio di potenza e isolamento

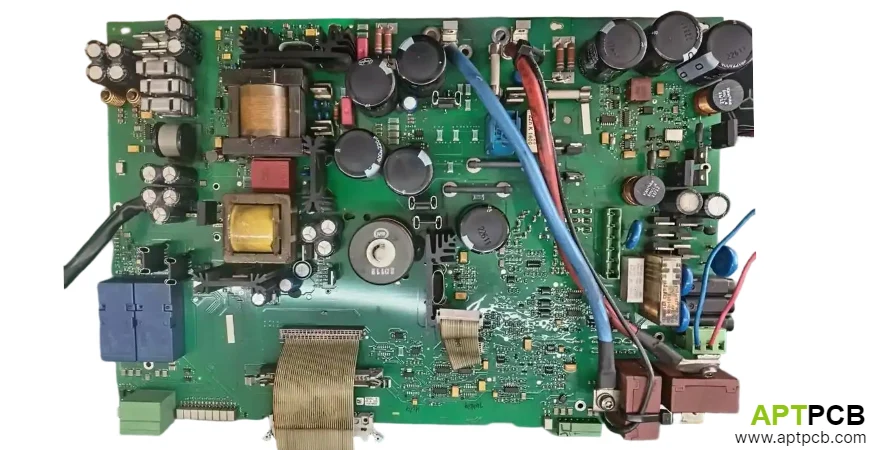

Gli stadi di potenza di un VFD commutano centinaia di volt a frequenze di qualche kilohertz tramite ponti IGBT o MOSFET. Il layout del PCB influenza direttamente perdite di commutazione, stress di tensione e generazione di disturbi. Un layout poco curato puo aumentare le perdite del 20 % o oltre e provocare problemi EMC che richiedono una riprogettazione costosa.

L'induttanza del loop di potenza e uno dei parametri piu critici. Ogni nanohenry di induttanza crea picchi di tensione durante la commutazione di corrente, secondo V = L × di/dt. Se un IGBT commuta a 5-10 kA/μs, anche 50 nH di induttanza parassita possono generare overshoot di 250-500 V, aumentando lo stress sui componenti e peggiorando il comportamento EMC.

Anche la costruzione in rame pesante necessaria per gestire la potenza condiziona le opzioni di layout. Un rame da 3-6 oz modifica le caratteristiche di incisione e le dimensioni minime producibili. Le regole di progetto devono quindi tenere conto dei vincoli produttivi riducendo comunque al minimo le aree di loop.

Principi di layout dello stadio di potenza

- Minimizzare i loop: I condensatori del bus DC vanno posizionati a ridosso dei moduli IGBT con collegamenti molto corti.

- Bus laminati: Piani di rame sovrapposti per DC+ e DC- aiutano a ridurre l'induttanza di distribuzione.

- Integrazione degli snubber: Gli snubber RC o RCD devono stare sui terminali del modulo IGBT e non lontano sul PCB.

- Barriere di isolamento: Lo stadio di potenza ad alta tensione deve restare separato dai circuiti di controllo con adeguate distanze di fuga.

- Espansione termica: I piani in rame pesante possono richiedere attenzione al disallineamento di CTE rispetto al substrato.

- Condivisione della corrente: Gli stadi di uscita in parallelo richiedono percorsi a impedenza simmetrica per condividere correttamente la corrente.

Progettazione del circuito gate driver

I gate driver trasformano i segnali di comando in impulsi di corrente elevata necessari per commutare rapidamente gli IGBT. Il circuito deve fornire un pilotaggio di gate rapido e pulito mantenendo l'isolamento tra la massa di controllo e lo stadio di potenza ad alta tensione.

I requisiti di isolamento dipendono dalla topologia di potenza. Negli inverter trifase, i driver high-side fanno riferimento a nodi di fase che oscillano sull'intera tensione del bus DC. L'isolamento deve quindi sostenere sia la tensione di lavoro continua sia i transitori di commutazione. Nei progetti moderni veloci questo richiede spesso isolatori con CMTI superiore a 50 kV/μs.

Anche il PCB stackup ha un ruolo importante. I segnali di gate hanno fronti rapidi che possono accoppiarsi capacitivamente attraverso le barriere di isolamento. Un layout corretto riduce questi accoppiamenti parassiti e al tempo stesso rispetta le distanze di sicurezza.

Requisiti di layout del gate driver

- Miller clamp: Una polarizzazione negativa del gate o un Miller clamp aiutano a evitare accensioni spurie dovute al coupling dV/dt.

- Connessione Kelvin source: Un ritorno di gate separato dal percorso di potenza riduce l'impatto dell'induttanza parassita sul pilotaggio.

- Alimentazione bootstrap: Il condensatore bootstrap e il diodo devono essere dimensionati per garantire sufficiente carica di gate anche nelle condizioni peggiori.

- Allineamento dei tempi di propagazione: I ritardi tra high-side e low-side devono restare molto vicini per evitare shoot-through.

- Spaziature di isolamento: Le distanze di fuga e isolamento devono seguire IEC 60664-1 in base a tensione di lavoro e transitori.

- Posizionamento delle resistenze di gate: Le resistenze di gate vanno poste il piu vicino possibile al modulo IGBT per smorzare bene le oscillazioni.

Misura di corrente e tensione

Misure accurate di corrente e tensione permettono agli algoritmi di controllo vettoriale di migliorare rendimento e risposta dinamica del motore. Il PCB deve trasportare questi segnali analogici sensibili in un ambiente elettricamente ostile senza compromettere la precisione di misura.

La misura della corrente si basa spesso su sensori Hall oppure su shunt con amplificatori isolati. Gli shunt offrono di solito maggiore precisione e banda passante, ma richiedono amplificatori in grado di sopportare la tensione di modo comune del bus DC e i relativi transitori. I sensori Hall forniscono isolamento intrinseco, ma introducono errori di guadagno e offset.

La misura della tensione del bus DC viene normalmente realizzata con divisori resistivi a retroazione isolata oppure con sensori isolati dedicati. Il circuito deve respingere il contenuto ad alta frequenza della PWM e seguire con precisione le variazioni del bus durante frenatura rigenerativa o transitori di carico. Un buon condizionamento analogico richiede attenzione a filtraggio e riferimenti di massa.

Regole di progetto per il sensing

- Posizionamento degli shunt: Gli shunt si collocano spesso sul ramo DC- per una misura semplice; tre shunt consentono la ricostruzione delle tre fasi.

- Filtraggio del rumore: Filtri RC sui segnali di misura attenuano il rumore di commutazione senza ridurre troppo la banda utile del controllo. Sono comuni frequenze di taglio tra 1 e 10 kHz.

- Routing differenziale: I segnali di misura dovrebbero essere instradati come coppie differenziali con piani di riferimento per migliorare il rigetto del rumore di modo comune.

- Riferimento ADC: Una tensione di riferimento stabile e poco rumorosa e fondamentale per mantenere la precisione delle conversioni.

- Timing di campionamento: L'ADC deve campionare in sincronia con la PWM, nelle finestre stabili e non durante i fronti di commutazione.

- Predisposizione alla calibrazione: Punti di test e coefficienti di calibrazione facilitano l'aggiustamento di guadagno e offset in produzione.

Architettura di filtraggio EMC

Un VFD produce emissioni condotte e irradiate significative a causa della PWM di potenza. Il filtraggio EMC deve attenuarle fino ai limiti normativi e, contemporaneamente, sopportare le tensioni e correnti del circuito di potenza. I componenti del filtro portano la corrente di carico completa e devono resistere anche alle condizioni di guasto.

Il filtraggio in ingresso riduce le emissioni condotte lato rete. Le induttanze di modo comune insieme ai condensatori X e Y attenuano i disturbi nella banda 150 kHz-30 MHz prevista dalle norme industriali. La frequenza di taglio deve essere abbastanza bassa per filtrare bene, ma non cosi bassa da creare risonanze indesiderate con l'impedenza d'ingresso.

Il filtraggio di uscita, tramite filtri dV/dt o sinusoidali, protegge l'isolamento del motore e riduce le correnti nei cuscinetti. Questi filtri portano tutta la corrente motore alla frequenza PWM e dissipano una potenza non trascurabile. Il PCB termico deve tenere conto di queste perdite.

Implementazione dei filtri EMC

- Dimensionamento delle induttanze di modo comune: Induttanza e corrente di saturazione devono essere coerenti con gli obiettivi di emissione condotta.

- Tenuta in tensione dei condensatori: I condensatori X e Y devono essere scelti per i transitori previsti e con le corrette approvazioni di sicurezza.

- Smorzamento delle risonanze: Resistenze di smorzamento impediscono al filtro di amplificare determinate frequenze.

- Terminazione delle schermature: Le schermature dei cavi di ingresso vanno collegate al contenitore del filtro e non al piano di massa del PCB.

- Controllo del dV/dt in uscita: Induttanze o filtri dV/dt devono limitare la rapidita di salita della tensione ai morsetti motore sotto 500 V/μs per cavi oltre 10 m.

- Architettura di messa a terra: I circuiti di controllo richiedono un riferimento di massa a punto singolo separato dai ritorni di potenza ad alta corrente.

Gestione termica per l'elettronica di potenza

Gli stadi di potenza di un VFD dissipano una quantita importante di calore dovuta alle perdite di conduzione e commutazione. Un azionamento da 10 kW con efficienza del 97 % dissipa ancora 300 W all'interno. Questa potenza si concentra nei semiconduttori di potenza, che devono restare sotto i limiti di temperatura di giunzione per garantire affidabilita.

I semiconduttori di potenza vengono montati su dissipatori o piastre fredde tramite materiali di interfaccia termica. Il disegno termico del PCB deve trasferire il calore dagli encapsulati alle superfici di montaggio con la minore resistenza possibile. I substrati PCB a nucleo metallico consentono il montaggio diretto di package ottimizzati termicamente con resistenze inferiori a 0,5 °C/W.

Anche i gate driver richiedono attenzione termica. La potenza dissipata dai relativi IC cresce con la carica di gate e con la frequenza di commutazione. Un driver che lavora a 10 kHz puo dissipare 1-2 W, e questo calore va evacuato tramite il PCB o percorsi termici dedicati.

Approcci di progetto termico

- Montaggio dei semiconduttori: Il montaggio diretto sul dissipatore tramite materiale di interfaccia termica e spesso la scelta migliore, lasciando al PCB il ruolo principale di supporto segnali.

- Array di vias termiche: Quando il PCB contribuisce allo smaltimento termico, array di vias sotto i dispositivi riducono la resistenza verso piani interni e aree di rame.

- Scelta del peso di rame: Nelle sezioni di potenza 3-6 oz di rame aiutano sia la portata di corrente sia la diffusione termica.

- Coordinamento con il flusso d'aria: Il posizionamento dei componenti deve seguire il reale andamento del flusso se si usa raffreddamento forzato.

- Monitoraggio temperatura: Sensori NTC su dissipatore e semiconduttori supportano una protezione termica affidabile.

- Verifica del derating: Il progetto termico deve essere controllato alla massima temperatura ambiente con margine per invecchiamento.

Integrazione dell'interfaccia di controllo

Il sistema di controllo di un VFD deve comunicare con reti di automazione, interfacce operatore e funzioni di sicurezza. Il PCB deve supportare queste interfacce mantenendo l'isolamento rispetto allo stadio di potenza ad alta tensione e una buona immunita ai disturbi generati dalla commutazione.

Protocolli industriali come PROFINET, EtherCAT o Modbus TCP richiedono interfacce Ethernet isolate con transceiver di grado industriale. I protocolli seriali piu datati richiedono invece transceiver RS-485 con protezione industriale da sovratensione. Le buone pratiche di PCB per controllo industriale sono fondamentali per comunicazioni robuste in fabbrica.

Gli I/O digitali per start, stop, riferimento velocita e stato richiedono di solito compatibilita 24 VDC e isolamento dai livelli logici interni. Gli ingressi analogici accettano spesso segnali 0-10 V o 4-20 mA per la consigna di velocita. Questi segnali a basso livello sono particolarmente sensibili ai disturbi captati dai circuiti di potenza vicini.

Progetto dell'interfaccia di controllo

- Isolamento Ethernet: Serve almeno 1500 Vrms di isolamento, con corretto posizionamento dei trasformatori e separazioni di massa secondo il PHY.

- Protezione degli ingressi analogici: Gli ingressi analogici devono includere protezione ESD, protezione da sovratensione e filtraggio contro il rumore.

- Isolamento degli I/O digitali: I segnali di campo dovrebbero passare verso la logica interna tramite optoisolatori o isolatori digitali.

- Safe Torque Off: La funzione STO richiede ingressi di sicurezza dedicati con appropriato isolamento e monitoraggio.

- Interfaccia encoder: Ingressi encoder differenziali con terminazione e filtraggio migliorano l'immunita ai disturbi.

- Messa a terra delle comunicazioni: La massa di rete dovrebbe riferirsi al telaio e non al piano di massa della scheda di controllo.

Riepilogo

La progettazione di PCB VFD unisce elettronica di potenza, tecnologia dei gate driver, misure di precisione e gestione EMC in un sistema che deve lavorare in modo affidabile in ambienti industriali severi. Alte tensioni, fronti rapidi e dissipazioni elevate impongono una progettazione coordinata tra aspetti elettrici, termici e meccanici. Il risultato dipende dalla comprensione delle interazioni tra layout di potenza, qualita del gate drive, accuratezza delle misure e comportamento EMC.