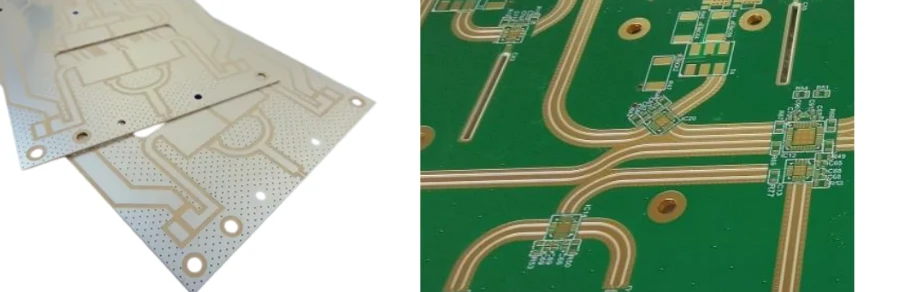

Diseñar una PCB de celda pequeña 5G requiere navegar por una compleja intersección de integridad de señal de alta frecuencia, gestión térmica compacta y capacidad de fabricación. A diferencia de las estaciones base macro tradicionales, las celdas pequeñas (incluidas las celdas Femto, Pico y Micro) operan en entornos restringidos donde la disipación de calor y la pérdida de señal son puntos críticos de falla. APTPCB (Fábrica de PCB APTPCB) se especializa en la fabricación de estas placas de alto rendimiento, asegurando que se cumplan las estrictas especificaciones de RF tanto para implementaciones Sub-6GHz como mmWave.

Respuesta Rápida (30 segundos)

Para una construcción exitosa de una PCB de celda pequeña 5G, los ingenieros deben priorizar los materiales de baja pérdida y la eficiencia térmica.

- Selección de Materiales: Utilice laminados de alta frecuencia (Rogers, Taconic o Panasonic Megtron 6/7) con Df < 0.003 y Dk estable en amplios rangos de frecuencia.

- Estrategia de Apilamiento (Stackup): Implemente apilamientos híbridos (FR4 + material de alta frecuencia) para equilibrar el costo y el rendimiento de RF.

- Gestión Térmica: Integre monedas de cobre, capas de cobre pesado (2oz+) o densas matrices de vías térmicas debajo de los componentes del PA (Amplificador de Potencia).

- Control de Impedancia: Mantenga una tolerancia estricta de ±5% o ±7% en las líneas de RF; la tolerancia estándar de ±10% a menudo es insuficiente para 5G mmWave.

- Acabado Superficial: Prefiera ENIG o ENEPIG para asegurar superficies planas para componentes de paso fino y unión de cables (wire bonding), evitando HASL debido a la irregularidad.

- Mitigación de PIM: Minimizar la intermodulación pasiva utilizando lámina de cobre de bajo perfil (VLP/HVLP) y limitando la máscara de soldadura sobre las trazas de alta frecuencia.

Cuándo aplicar la PCB de celda pequeña 5G (y cuándo no)

Comprender el escenario de implementación específico es crucial antes de finalizar la arquitectura de la PCB. Las celdas pequeñas cierran la brecha entre las enormes macro torres y los dispositivos de usuario final.

Cuándo usar la tecnología de PCB de celda pequeña 5G:

- Áreas urbanas de alta densidad: Cuando la capacidad de la red necesita ser aumentada en estadios, centros comerciales o centros urbanos donde la infraestructura de PCB de macro celda 5G no puede penetrar o manejar la carga.

- Implementación de ondas milimétricas (mmWave): Para aplicaciones de corto alcance y alto ancho de banda (24 GHz y superiores) que requieren sustratos especializados para minimizar la atenuación de la señal.

- Cobertura interior: Entornos empresariales que requieren unidades dedicadas de PCB de femtocelda 5G o PCB de picocelda 5G para asegurar una señal consistente a través de las paredes.

- Relleno de huecos: Para eliminar zonas muertas en el borde del área de cobertura de una macro celda.

- Aplicaciones de baja latencia: Configuraciones de IoT Industrial (IIoT) donde el procesamiento necesita ocurrir más cerca del usuario (Computación en el Borde).

Cuándo podría no ser la opción correcta:

- Cobertura rural de área amplia: Una PCB de macro celda 5G estándar es más rentable para cubrir grandes áreas geográficas escasamente pobladas.

- Solo IoT de baja frecuencia: Si el dispositivo solo transmite paquetes de datos esporádicos en frecuencias NB-IoT o LoRaWAN (sub-1GHz) sin requisitos de alto rendimiento, las placas FR4 estándar son suficientes.

- Electrónica de consumo de costo extremadamente bajo: Los materiales necesarios para las celdas pequeñas 5G (PTFE, hidrocarburos rellenos de cerámica) son significativamente más caros que el vidrio epoxi estándar.

- Repetidores pasivos: Si el dispositivo no procesa señales sino que solo las refleja, una pila de PCB activa completa puede ser innecesaria.

Reglas y especificaciones

Para garantizar la fiabilidad de una PCB de celda pequeña 5G, se deben cumplir reglas de diseño específicas. Desviarse de estos valores a menudo conduce a la degradación de la señal o a fallas térmicas.

| Regla | Valor/Rango recomendado | Por qué es importante | Cómo verificar | Si se ignora |

|---|---|---|---|---|

| Constante Dieléctrica (Dk) | 3.0 – 3.5 (Estable) | Un Dk más bajo reduce el retardo de propagación de la señal; la estabilidad asegura una impedancia consistente en todas las frecuencias. | Revisar la hoja de datos frente a los gráficos de frecuencia. | Errores de temporización de la señal y desajustes de impedancia. |

| Factor de Disipación (Df) | < 0.003 @ 10GHz | Minimiza la pérdida de señal (pérdida de inserción), lo cual es crítico para la eficiencia energética en celdas pequeñas. | Pruebas con Analizador de Red Vectorial (VNA) en cupones. | Alta atenuación de la señal; rango reducido; sobrecalentamiento. |

| Rugosidad del Cobre | < 2 µm (VLP/HVLP) | El efecto pelicular a frecuencias 5G fuerza la corriente a la superficie; el cobre rugoso aumenta la resistencia y la pérdida. | Análisis SEM o verificación de la hoja de especificaciones. | Mayor pérdida de inserción y distorsión de fase. |

| Tolerancia de Impedancia | ±5% (RF), ±10% (Digital) | Ajusta las líneas de transmisión a la fuente/carga para evitar reflexiones (VSWR). | Calculadora de Impedancia y pruebas TDR. | Alta pérdida de retorno; reflexión de señal; tasas de datos reducidas. |

| Conductividad Térmica | > 0.5 W/mK (Dieléctrico) | Las celdas pequeñas están cerradas; la propia PCB debe disipar el calor de los componentes activos. | Software de simulación térmica (CFD). | Sobrecalentamiento de componentes; estrangulamiento; fallo del dispositivo. |

| Relación de Aspecto de Vía | < 8:1 (Pasante), < 0.8:1 (Micro) | Asegura un chapado y conectividad fiables en placas HDI de alto número de capas. | Análisis de sección transversal (microsección). | Circuitos abiertos; grietas en el barril durante el reflujo; vías poco fiables. |

| Red de Máscara de Soldadura | > 3 mil (0.076mm) | Evita puentes de soldadura entre almohadillas de paso fino comunes en módulos RF. | Verificación DFM en software CAM. | Cortocircuitos durante el ensamblaje; menor rendimiento. |

| Resistencia al Pelado | > 0.8 N/mm | Los materiales de alta frecuencia (PTFE) a menudo tienen poca adhesión; crítico para la fiabilidad. | Prueba de pelado según IPC-TM-650. | Levantamiento de almohadillas durante el retrabajo o ciclos térmicos; delaminación. |

| Registro de Capas | ± 3 mil | La desalineación afecta el acoplamiento entre capas en estructuras de RF (p. ej., líneas acopladas de lado ancho). | Inspección por rayos X. | Rendimiento de RF impredecible; variación de impedancia. |

| Absorción de Humedad | < 0.1% | El agua es polar y absorbe energía de RF; una alta absorción cambia Dk/Df. | Pruebas en cámara ambiental. | Deriva del rendimiento en ambientes húmedos; delaminación. |

Pasos de implementación

Pasar de las especificaciones a una placa física requiere un flujo de trabajo disciplinado. Seguir estos pasos asegura que la PCB de Celda Pequeña 5G cumpla con los requisitos eléctricos y mecánicos.

Definir Bandas de Frecuencia y Arquitectura

- Acción: Determinar si el diseño es Sub-6GHz, mmWave, o ambos.

- Parámetro Clave: Frecuencia de Operación (p. ej., 3.5 GHz vs. 28 GHz).

- Verificación de Aceptación: Diagrama de bloques confirmado con el equipo de ingeniería de RF.

Selección de Material y Diseño de Apilamiento

- Acción: Seleccionar un laminado basado en el presupuesto de pérdidas. Para mmWave, elija materiales Rogers o Taconic. Para Sub-6GHz sensible al costo, considere Megtron 6.

- Parámetro Clave: Valor de Df y CTE (Coeficiente de Expansión Térmica).

- Verificación de Aceptación: La simulación del apilamiento muestra que los objetivos de impedancia son alcanzables con espesores de preimpregnado estándar.

Planificación de la Estrategia Térmica

- Acción: Identificar componentes de alta potencia (PA, FPGA) y planificar las rutas de disipación de calor. Decidir entre vías térmicas, monedas de cobre o PCB con respaldo metálico.

- Parámetro Clave: Resistencia térmica de unión a ambiente.

- Verificación de Aceptación: La simulación térmica confirma que la temperatura máxima de unión se mantiene por debajo de 100°C (o el límite del componente).

Diseño y Enrutamiento RF

- Acción: Enrutar las líneas de RF primero. Mantener las trazas cortas y directas. Evitar curvas de 90 grados; usar enrutamiento de 45 grados o curvo para minimizar las reflexiones.

- Parámetro Clave: Ancho y espacio de la traza (calculado para 50Ω).

- Verificación de Aceptación: El DRC (Design Rule Check) pasa para el espaciado mínimo y el ancho de la traza.

Conexión a Tierra y Blindaje

- Acción: Colocar vías de costura a lo largo de las trazas de RF (cercado de vías) para contener los campos. Asegurarse de que los planos de tierra sólidos no estén rotos debajo de las líneas de RF.

- Parámetro Clave: Espaciado de las vías (< λ/20 de la frecuencia más alta).

- Verificación de Aceptación: No se encuentran discontinuidades en la ruta de retorno en la simulación.

DFM y Prototipado

- Acción: Realizar una verificación de las directrices DFM para asegurar que el diseño sea fabricable por APTPCB.

- Parámetro Clave: Tamaño mínimo de perforación, anillo anular y pista/espacio.

- Verificación de Aceptación: Informe CAM limpio sin violaciones críticas de fabricación.

Fabricación y Pruebas

- Acción: Enviar archivos Gerber para la fabricación. Solicitar informes TDR (Reflectometría en el Dominio del Tiempo).

- Parámetro clave: Verificación de la tolerancia de impedancia.

- Verificación de aceptación: Las placas físicas pasan la inspección visual y las pruebas de impedancia TDR.

Modos de fallo y resolución de problemas

Incluso con un diseño riguroso, pueden surgir problemas durante las pruebas o la implementación. Aquí se explica cómo solucionar fallos comunes en las PCB de celdas pequeñas 5G.

1. Alta pérdida de inserción (atenuación de la señal)

- Síntoma: La intensidad de la señal es menor de lo calculado en la salida; rango reducido.

- Causas: Material incorrecto (Df alto), lámina de cobre rugosa, máscara de soldadura sobre trazas de RF.

- Verificaciones: Verificar los datos del lote de material; comprobar si la máscara de soldadura se eliminó de las líneas de RF (la máscara de soldadura añade pérdida).

- Solución: Rediseñar con cobre VLP o material de Df más bajo; eliminar la máscara de soldadura de las trazas de alta velocidad.

- Prevención: Especificar "Apertura de máscara de soldadura" sobre las trazas de RF en las notas de fabricación.

2. Intermodulación pasiva (PIM)

- Síntoma: El nivel de ruido aumenta; interferencia en las bandas de recepción; rendimiento de datos reducido.

- Causas: Materiales ferromagnéticos (níquel) en la trayectoria de la señal, malas uniones de soldadura, conectores oxidados, cobre rugoso.

- Verificaciones: Pruebas de PIM; inspeccionar el acabado superficial (ENIG puede causar PIM debido al níquel; la plata o OSP son mejores para RF pura).

- Solución: Cambiar el acabado superficial a Plata por Inmersión u OSP; mejorar la calidad de la soldadura.

- Prevención: Evitar acabados a base de níquel en líneas de RF de alta potencia; usar conectores clasificados para PIM.

3. Apagado térmico / Sobrecalentamiento

- Síntoma: El dispositivo se reinicia aleatoriamente o reduce su rendimiento después de minutos de operación.

- Causas: Vías térmicas insuficientes, calor atrapado en las capas internas, contacto deficiente con el disipador de calor.

- Verificaciones: Imágenes con cámara térmica; inspeccionar la aplicación de pasta térmica; verificar el espesor del chapado de las vías.

- Solución: Añadir un disipador de calor externo; mejorar el flujo de aire.

- Prevención: Diseñar con monedas de cobre incrustadas o aumentar significativamente la densidad de vías térmicas debajo de los PA.

4. Desajuste de impedancia (VSWR alto)

- Síntoma: Reflexión de la señal, pérdida de potencia, posible daño al transmisor.

- Causas: Variaciones de grabado, altura de apilamiento incorrecta, variación del espesor dieléctrico.

- Verificaciones: Medición TDR; análisis de sección transversal del ancho de la pista.

- Solución: Ajuste de redes de adaptación (si es posible); de lo contrario, descarte de la placa.

- Prevención: Solicitar cupones de impedancia en el panel; especificar una tolerancia estricta de ±5%.

5. Delaminación durante el reflujo

- Síntoma: Burbujeo o separación de capas después del ensamblaje.

- Causas: Humedad atrapada en la PCB; desajuste de CTE entre materiales híbridos (p. ej., PTFE y FR4).

- Verificaciones: Registros de horneado; tablas de compatibilidad de materiales.

- Solución: Ninguna para las placas afectadas.

- Prevención: Hornear las placas antes del ensamblaje; usar materiales de alta Tg; asegurar que los materiales híbridos tengan un CTE en el eje Z compatible.

6. Fallo de vía (circuito abierto)

- Síntoma: Conectividad intermitente, especialmente después de ciclos térmicos.

- Causas: Agrietamiento del barril debido a la expansión del eje Z; mala calidad del chapado.

- Verificaciones: Análisis de microsección; prueba de continuidad.

- Solución: Ninguna.

- Prevención: Utilizar materiales con bajo CTE en el eje Z; asegurar que la relación de aspecto esté dentro de los límites de fabricación (p. ej., < 8:1).

Decisiones de diseño

La resolución de problemas a menudo revela que la causa raíz reside en las decisiones de diseño tempranas. Al planificar una PCB para Small Cell 5G, los ingenieros se enfrentan a varias compensaciones críticas.

Apilamiento híbrido vs. homogéneo

- Decisión: ¿Debería toda la placa ser de material de alta frecuencia, o solo las capas exteriores?

- Impacto: Una placa de PTFE homogénea ofrece el mejor rendimiento eléctrico, pero es mecánicamente blanda, difícil de procesar y cara. Un apilamiento híbrido (PTFE exterior / FR4 interior) reduce el costo y mejora la rigidez, pero introduce riesgos de desajuste de CTE.

- Recomendación: Para diseños de PCB para Micro Cell 5G donde el costo es un factor, utilice un enfoque híbrido. Para unidades de ondas milimétricas de ultra alto rendimiento, puede ser necesario un enfoque homogéneo o de unión por fusión multicapa.

HDI vs. Agujero pasante

- Decisión: ¿Utilizar interconexión de alta densidad (HDI) con microvías o agujeros pasantes estándar?

- Impacto: Los chipsets 5G (BGA) a menudo tienen pasos finos (0,4 mm o menos) que requieren HDI. HDI mejora la integridad de la señal al reducir los talones de vía, pero aumenta el costo.

- Recomendación: HDI es casi obligatorio para los diseños modernos de PCB para Small Cell 5G para acomodar la ruptura de BGA y minimizar la capacitancia parasitaria. Selección de Acabado Superficial

- Decisión: ¿ENIG, ENEPIG, Plata por Inmersión u OSP?

- Impacto: ENIG es robusto pero el Níquel es magnético y puede causar PIM. La Plata por Inmersión es excelente para RF pero se empaña fácilmente. OSP es económico y bueno para RF pero tiene una vida útil corta.

- Recomendación: Utilice Plata por Inmersión o ENEPIG para placas 5G de alta frecuencia para equilibrar la soldabilidad y el rendimiento de RF.

Preguntas Frecuentes

P1: ¿Cuál es la principal diferencia entre una PCB de celda pequeña 5G y una PCB de macrocelda? R: La diferencia principal es la escala y la potencia. Los diseños de PCB de celda pequeña 5G son compactos, de menor potencia y a menudo requieren una integración de mayor densidad (HDI) en comparación con la configuración modular grande y de alta potencia de una PCB de macrocelda 5G.

P2: ¿Por qué son populares las configuraciones de apilamiento híbridas para las celdas pequeñas 5G? R: Equilibran el costo y el rendimiento.

- Las capas de RF utilizan materiales costosos de baja pérdida (Rogers/Taconic).

- Las capas digitales/de potencia utilizan FR4 estándar.

- Esto reduce el costo total del material mientras se mantiene la integridad de la señal.

P3: ¿Puedo usar FR4 estándar para PCBs de celda pequeña 5G? R: Generalmente, no, especialmente para la ruta de RF.

- El FR4 estándar tiene un Df (pérdida) alto y un Dk inestable en frecuencias 5G.

- Puede usarse para la sección de control digital o las capas de distribución de energía en una configuración de apilamiento híbrida.

P4: ¿Cuál es el tiempo de entrega para la fabricación de estas PCBs? R: Los tiempos de entrega suelen ser más largos que los de las placas estándar debido a la disponibilidad de materiales.

- FR4 estándar: 3-5 días.

- Materiales híbridos/RF: 10-15 días (dependiendo del stock de materiales Rogers/Panasonic).

P5: ¿Cómo gestiono el calor en un encapsulado tan pequeño? R: Se requiere un diseño térmico agresivo.

- Utilice monedas de cobre (metal incrustado).

- Utilice PCBs de núcleo metálico (MCPCB) para las etapas de potencia.

- Maximice los arreglos de vías térmicas.

P6: ¿Cuál es la diferencia entre las PCBs de celda Femto, Pico y Micro? R: Difieren principalmente en la potencia de salida y el rango de cobertura.

- PCB de celda Femto 5G: Menor potencia (hogar/oficina), factor de forma más pequeño.

- PCB de celda Pico 5G: Potencia media (empresa/público interior), ligeramente más grande.

- PCB de celda Micro 5G: Mayor potencia (urbano exterior), robustecida, la más grande de las celdas pequeñas.

P7: ¿Por qué es una preocupación la PIM (Intermodulación Pasiva)? R: La PIM crea interferencias que bloquean las velocidades de subida.

- Actúa como autointerferencia.

- Crítico en 5G donde el ancho de banda se maximiza.

P8: ¿Necesito perforación posterior para las PCBs de celdas pequeñas 5G? R: Sí, si se utilizan vías pasantes para señales de alta velocidad.

- La perforación posterior elimina el trozo de vía no utilizado.

- Los trozos actúan como antenas/filtros que degradan la calidad de la señal a altas frecuencias.

P9: ¿Cuál es el tipo de lámina de cobre preferido? R: VLP (Perfil Muy Bajo) o HVLP (Perfil Hiper Muy Bajo).

- El cobre más liso reduce las pérdidas por efecto pelicular.

- Esencial para la eficiencia de ondas milimétricas (mmWave).

P10: ¿Cómo verifica APTPCB el control de impedancia? R: Utilizamos TDR (Reflectometría en el Dominio del Tiempo) en cupones de prueba incluidos en el panel de producción.

- Medimos la impedancia real en comparación con el objetivo de diseño.

- Los informes se proporcionan con el envío.

P11: ¿Se requiere la tecnología de vías ciegas y enterradas? R: A menudo, sí.

- Para ahorrar espacio en celdas pequeñas compactas.

- Para mejorar la integridad de la señal acortando los talones de las vías.

P12: ¿Cuál es el impacto en el costo de usar material Rogers? R: Los materiales Rogers pueden costar de 3 a 10 veces más que el FR4.

- Por eso se utilizan apilamientos híbridos para minimizar el volumen de material costoso.

Páginas y herramientas relacionadas

- Datos de materiales: Materiales de PCB Rogers

- Herramienta de diseño: Calculadora de impedancia

- Verificaciones de fabricación: Directrices DFM

Glosario (términos clave)

| Término | Definición | Contexto en PCB de celda pequeña 5G |

|---|---|---|

| mmWave | Onda milimétrica (24 GHz - 100 GHz). | Requiere materiales de pérdida ultrabaja y tolerancias estrictas. |

| Sub-6GHz | Frecuencias por debajo de 6 GHz. | La capa de "cobertura" de 5G; menos exigente que mmWave pero más difícil que 4G. |

| PIM | Intermodulación pasiva. | Distorsión de la señal causada por no linealidades en componentes pasivos (conectores, trazas). |

| Dk (Constante Dieléctrica) | Medida de la capacidad de un material para almacenar energía eléctrica. | Afecta la impedancia y la velocidad de propagación de la señal. |

| Df (Factor de Disipación) | Medida de cuánta energía se pierde como calor en el material. | Un Df más bajo es crítico para la eficiencia 5G. |

| CTE | Coeficiente de Expansión Térmica. | Cuánto se expande el material con el calor; la falta de coincidencia causa delaminación. |

| MIMO | Múltiple Entrada Múltiple Salida. | Uso de múltiples antenas; aumenta la complejidad de la PCB y la densidad de enrutamiento. |

| Beamforming | Conformación de haces. | Enfocar la señal hacia un usuario específico. |

| Backhaul | Retorno. | La conexión desde la celda pequeña a la red central. |

| Small Cell | Celda Pequeña. | Puntos de acceso inalámbricos de baja potencia (Femto, Pico, Micro). |

| Hybrid Stackup | Apilamiento Híbrido. | Combinación de diferentes materiales laminados. |

Conclusión

Diseñar una PCB de Celda Pequeña 5G es un acto de equilibrio entre el rendimiento de alta frecuencia, la resistencia térmica y la viabilidad de fabricación. Ya sea que esté construyendo una PCB de Femtocelda 5G para uso en interiores o una robusta PCB de Microcelda 5G para densificación en exteriores, las reglas de la física con respecto a Dk, Df y la disipación térmica siguen siendo absolutas.

Al adherirse a las especificaciones descritas anteriormente —específicamente en cuanto a la selección de materiales, apilamientos híbridos y mitigación de PIM— los ingenieros pueden evitar costosos rediseños y fallas en el campo. APTPCB apoya este proceso desde el prototipo hasta la producción en masa, ofreciendo los materiales especializados y la experiencia en DFM requeridos para las redes de próxima generación. Para una revisión detallada de su apilamiento específico o para obtener precios precisos en laminados de alta frecuencia, solicite una cotización hoy mismo.