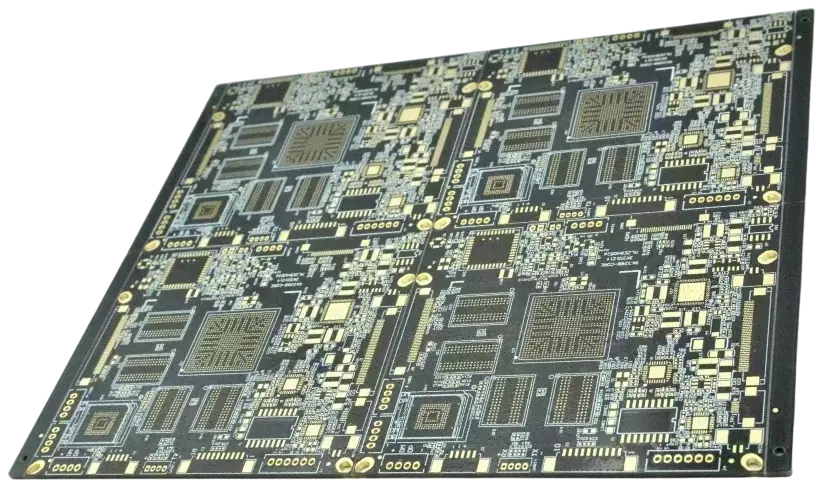

AI-Native PCB: definición, alcance y a quién va dirigida esta guía

El término AI-Native PCB se refiere a las placas de circuito impreso de alto rendimiento específicamente diseñadas para soportar ecosistemas de hardware de Inteligencia Artificial, incluyendo servidores de entrenamiento, aceleradores de inferencia y nodos de computación perimetral. A diferencia de la electrónica estándar, estas placas deben manejar simultáneamente un procesamiento masivo de datos, cargas térmicas extremas y una latencia de señal ultrabaja. A medida que la infraestructura de IA converge con las telecomunicaciones, los requisitos para estas placas a menudo se superponen con los de la infraestructura de alta frecuencia, como los módulos 5G AAU PCB (Unidad de Antena Activa) y 5G ADC PCB (Convertidor Analógico-Digital), creando un desafío de fabricación complejo que exige una precisión más allá de los estándares IPC Class 2.

Este manual está diseñado para ingenieros de hardware, gerentes de NPI y responsables de compras que están haciendo la transición de la electrónica digital estándar al hardware de computación de alto rendimiento (HPC). Elimina el ruido de marketing para centrarse en las realidades físicas de la fabricación: selección de materiales, integridad del apilamiento y los pasos de validación específicos necesarios para prevenir fallos en campo en costosos clústeres de IA. En APTPCB (APTPCB PCB Factory), hemos observado que la causa principal de los retrasos en los proyectos de este sector no es la capacidad de diseño, sino una desalineación entre la intención del diseño y la realidad de la fabricación. Esta guía sirve como un marco de toma de decisiones para cerrar esa brecha, asegurando que sus especificaciones se traduzcan en hardware confiable.

Cuándo usar PCB nativos de IA (y cuándo un enfoque estándar es mejor)

Comprender el alcance definido anteriormente nos permite determinar exactamente cuándo el costo y la complejidad de un PCB nativo de IA están justificados frente a cuándo un diseño estándar de alta velocidad es suficiente.

Utilice un enfoque nativo de IA cuando:

- Las velocidades de señal superan los 56 Gbps PAM4: El FR4 estándar no puede soportar la integridad de la señal requerida para las interconexiones de IA modernas sin una atenuación masiva.

- El número de capas supera las 18: Los aceleradores de IA a menudo requieren un enrutamiento de alta densidad y planos de potencia extensos que las prensas de laminación estándar no pueden alinear con precisión sin herramientas especializadas.

- La densidad térmica es crítica: Si su GPU o TPU genera calor que requiere compatibilidad con refrigeración líquida o por inmersión, los materiales estándar de la máscara de soldadura y del sustrato pueden degradarse.

- Integración con infraestructura 5G: Los diseños que incorporan tecnología 5G AAU PCB para IA de borde requieren capacidades de señal mixta (RF + Digital) que exigen apilamientos híbridos.

Quédese con un PCB estándar de alta velocidad cuando:

- Dispositivos IoT Edge: La inferencia simple en microcontroladores (por ejemplo, reconocimiento de voz) rara vez necesita materiales exóticos; el FR4 estándar con impedancia controlada suele ser suficiente.

- Interfaces heredadas: Si la placa maneja principalmente PCIe Gen 3 o inferior, el costo adicional por materiales de ultra baja pérdida de grado IA es innecesario.

- Solo prototipado lógico: Si está validando la lógica a bajas velocidades antes de escalar a velocidad completa, los materiales estándar pueden ahorrar costos significativos durante las primeras revisiones.

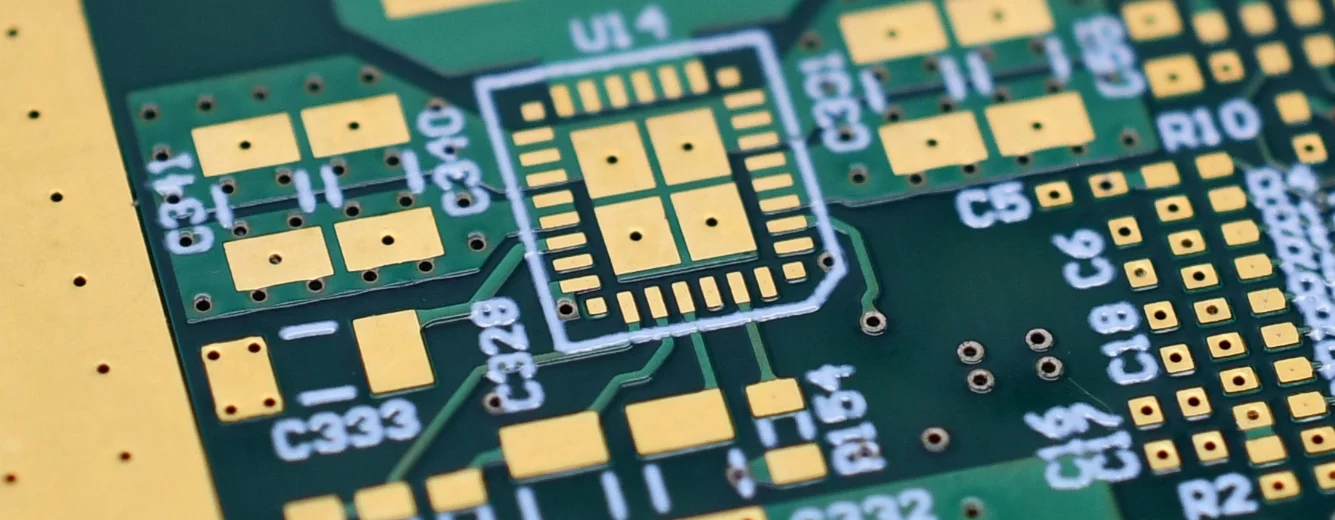

Especificaciones de PCB nativos de IA (materiales, apilamiento, tolerancias)

Una vez que haya determinado que su proyecto requiere un PCB nativo de IA, el siguiente paso es definir las especificaciones rígidas que regirán el proceso de fabricación.

- Materiales base (laminados):

- Requisito: Los materiales de ultra baja pérdida no son negociables.

- Objetivo: Df (Factor de Disipación) < 0,002 @ 10GHz; Dk (Constante Dieléctrica) < 3,6.

- Ejemplos: Panasonic Megtron 7/8, Isola Tachyon 100G o la serie Rogers RO3000 para secciones de RF híbridas.

- Rugosidad de la lámina de cobre:

- Requisito: Cobre HVLP (Hyper Very Low Profile) o HVLP2.

- Objetivo: Rugosidad de la superficie (Rz) < 1,5 µm para minimizar las pérdidas por efecto pelicular a altas frecuencias.

- Número de capas y apilamiento:

- Rango: Típicamente de 20 a 40+ capas para placas de grado servidor.

- Estructura: Múltiples ciclos de laminación (3+); a menudo requiere HDI (interconexión de alta densidad) "any-layer" o ELIC (interconexión en cada capa).

- Perforación y Vías:

- Taladro posterior: Obligatorio para capas de señal de alta velocidad para eliminar los talones de vía.

- Tolerancia: La tolerancia de profundidad del taladro posterior debe controlarse dentro de ±0,05 mm a ±0,10 mm para preservar la integridad de la señal sin cortar las capas internas.

- Relación de aspecto: Se requiere una capacidad de chapado de alta relación de aspecto (15:1 a 20:1) para placas gruesas (3,0 mm+).

- Control de impedancia:

- Tolerancia: Control estricto de ±5% o ±7% (el estándar es ±10%) en pares de un solo extremo y diferenciales.

- Pruebas: Pruebas TDR (reflectometría en el dominio del tiempo) al 100% en cupones y placas de producción.

- Acabado superficial:

- Preferido: ENIG (níquel químico oro de inmersión) o ENEPIG para soporte de unión de cables.

- Alternativa: Plata de inmersión para una menor pérdida de inserción, aunque la vida útil es más corta.

- Fiabilidad térmica:

- Tg (Temperatura de transición vítrea): > 180°C (Tg alta).

- Td (Temperatura de descomposición): > 350°C para soportar múltiples ciclos de reflujo durante el ensamblaje de grandes componentes BGA.

- Precisión de registro:

- Objetivo: Registro capa a capa dentro de ±2-3 mils (50-75µm) para asegurar que las almohadillas se alineen con las vías en pilas de alta capa.

- Limpieza:

- Contaminación iónica: < 0,65µg/cm² equivalente a NaCl, crítico para prevenir la migración electroquímica en entornos de centros de datos de alta tensión.

Riesgos de fabricación de PCB nativos de IA (causas raíz y prevención)

Con las especificaciones definidas, el enfoque se desplaza a la mitigación de los modos de fallo específicos asociados con la fabricación de diseños de PCB nativos de IA de alto rendimiento.

- Crecimiento de filamentos anódicos conductivos (CAF)

- Causa raíz: Polarización de alta tensión entre vías muy espaciadas combinada con la absorción de humedad en el sistema de resina.

- Detección: Pruebas CAF (más de 1000 horas a alta temperatura/humedad).

- Prevención: Usar materiales resistentes a CAF (tejido de vidrio extendido) y maximizar el espaciado entre vías siempre que sea posible.

- Cráteres en las almohadillas

- Causa raíz: Los materiales laminados quebradizos (comunes en materiales de alta velocidad) se fracturan bajo el estrés mecánico de la gran expansión térmica de los BGA.

- Detección: Microscopía acústica o pruebas de tinte y desprendimiento durante la validación.

- Prevención: Usar laminados reforzados con resina y unión en las esquinas/relleno inferior en BGAs grandes.

- Pérdida de integridad de la señal debido a la variación de grabado

- Causa raíz: El sobregrabado o subgrabado de trazas trapezoidales cambia el perfil de impedancia.

- Detección: Análisis de sección transversal y pruebas TDR.

- Prevención: Especificar factores de "compensación de grabado" en la ingeniería CAM y usar equipos de grabado al vacío.

- Delaminación durante el reflujo

- Causa principal: La humedad atrapada en placas gruesas se vaporiza durante las temperaturas de reflujo sin plomo (260°C).

- Detección: SAM (Microscopía Acústica de Barrido) después de la simulación de reflujo.

- Prevención: Estrictos protocolos de horneado (4-8 horas) antes del ensamblaje y embalaje con barrera de humedad (MBB).

- Residuo de talón de taladro trasero

- Causa principal: El desgaste de la broca o un cálculo erróneo de la profundidad deja un pequeño talón conductor.

- Detección: Inspección por rayos X o análisis TDR específico en busca de anomalías de reflexión.

- Prevención: Comprobaciones ópticas automatizadas de la broca y verificación por rayos X del primer artículo.

- Alabeo / Arqueamiento y Torsión

- Causa principal: Distribución asimétrica del cobre o apilamiento desequilibrado en placas de gran formato.

- Detección: Medición por Moiré de sombra.

- Prevención: vertido de cobre estrictamente equilibrado en todas las capas; uso de materiales de bajo CTE.

- Vacíos de chapado en vías de alta relación de aspecto

- Causa principal: La solución de chapado no circula eficazmente en orificios profundos y estrechos (por ejemplo, placa de 3 mm de espesor con vías de 0,2 mm).

- Detección: Seccionamiento transversal y pruebas de choque térmico.

- Prevención: Tecnología de chapado por pulsos y límites de diseño de la relación de aspecto (mantener por debajo de 15:1 si es posible).

- Discontinuidad de impedancia en las transiciones de capa

- Causa principal: Desalineación entre la almohadilla de la vía y la holgura del plano de referencia.

- Detección: Pruebas VNA (Analizador de Red Vectorial).

- Prevención: Imágenes directas por láser (LDI) para capas internas para asegurar una alineación precisa.

Validación y aceptación de PCB nativas de IA (pruebas y criterios de aprobación)

Para asegurar que los riesgos anteriores se gestionen, se debe ejecutar un plan de validación robusto antes de la producción en masa de cualquier PCB nativa de IA.

- Prueba de estrés de interconexión (IST):

- Objetivo: Verificar la fiabilidad de las vías bajo ciclos térmicos.

- Método: Someter los cupones a ciclos repetidos desde temperatura ambiente hasta 150°C (o más).

- Aceptación: Ningún aumento de resistencia > 10% después de 500 ciclos.

- Verificación de la integridad de la señal (parámetros S):

- Objetivo: Confirmar que la pérdida de inserción y la pérdida de retorno cumplen con los modelos de simulación.

- Método: Medición VNA hasta 28GHz o 56GHz.

- Aceptación: Desviación de la pérdida de inserción < 1dB/pulgada de la simulación; Pérdida de retorno < -15dB.

- Prueba Hipot (alto potencial):

- Objetivo: Asegurar el aislamiento entre los rieles de alimentación de alto voltaje (común en el suministro de energía para servidores de IA).

- Método: Aplicar alto voltaje (por ejemplo, 500V-1000V) entre redes.

- Aceptación: Corriente de fuga < 1mA; sin ruptura.

- Prueba de choque térmico:

- Objetivo: Probar la fuerza de unión del material y la integridad del chapado de las vías.

- Método: Transferencia líquido-líquido de -55°C a +125°C.

- Aceptación: Sin delaminación, ampollas o circuitos abiertos después de 100 ciclos.

- Prueba de soldabilidad:

- Objetivo: Asegurar que el acabado superficial acepte la soldadura correctamente.

- Método: IPC J-STD-003 (Dip and Look o Balanza de Humectación).

- Aceptación: > 95% de cobertura; tiempo de humectación < 2 segundos.

- Prueba de Contaminación Iónica (ROSE):

- Objetivo: Verificar la limpieza de la placa.

- Método: IPC-TM-650 2.3.25.

- Aceptación: < 1,56 µg/cm² equivalente de NaCl (a menudo más estricto para IA: < 0,65).

- Resistencia al Pelado del Cobre:

- Objetivo: Verificar la adhesión del cobre al dieléctrico.

- Método: Prueba de pelado mecánico.

- Aceptación: > 0,8 N/mm (o según la especificación de la hoja de datos del material).

- Estabilidad Dimensional:

- Objetivo: Asegurar que la placa encaje en el chasis y se alinee con los zócalos.

- Método: CMM (Máquina de Medición por Coordenadas).

- Aceptación: Tolerancias dentro de ±0,1 mm para el contorno; Alabeo < 0,75%.

Lista de verificación de calificación de proveedores de PCB nativos de IA (RFQ, auditoría, trazabilidad)

Al seleccionar un socio como APTPCB, utilice esta lista de verificación para asegurarse de que la fábrica sea realmente capaz de manejar los requisitos de los PCB nativos de IA en lugar de solo la producción estándar.

Grupo 1: Entradas de RFQ (Lo que debe proporcionar)

- Archivos Gerber X2 o ODB++ completos (preferidos para datos complejos).

- Netlist IPC-356 para verificación de pruebas eléctricas.

- Dibujo detallado del apilamiento que especifique los tipos de material (marca/serie) y el espesor dieléctrico.

- Tabla de impedancia que haga referencia a capas específicas y anchos de traza.

- Plano de perforación que distingue entre orificios pasantes, vías ciegas/enterradas y backdrills.

- Plano de fabricación con notas sobre los requisitos de Clase 3 (si aplica).

- Requisitos de panelización (si el ensamblaje requiere rieles/marcas de referencia específicos).

- Archivo Readme que destaca las redes críticas (por ejemplo, "No modificar el enrutamiento en la Red X").

Grupo 2: Prueba de Capacidad (Lo que el proveedor debe mostrar)

- Lista de equipos: Máquinas de imagen directa láser (LDI) para capas internas.

- Lista de equipos: Líneas de grabado al vacío (para líneas finas < 3 mil).

- Lista de equipos: Máquinas de backdrilling automatizadas con sensor de control de profundidad.

- Experiencia: Estudios de caso o muestras anonimizadas de placas de más de 20 capas.

- Stock de materiales: Prueba de inventario o cadena de suministro directa para materiales Megtron/Rogers.

- Capacidad HDI: Capacidad demostrada para microvías apiladas (por ejemplo, 3+N+3).

Grupo 3: Sistema de Calidad y Trazabilidad

- Certificaciones: ISO 9001 (General), IATF 16949 (si es IA automotriz), UL 94V-0.

- Trazabilidad: ¿Pueden rastrear una placa específica hasta el lote de materia prima y el ciclo de prensa de laminación?

- IQC (Control de Calidad de Entrada): Procedimiento para verificar las propiedades del pre-preg y del material del núcleo.

- AOI (Inspección Óptica Automatizada): ¿Se realiza AOI en cada capa interna?

- Seccionamiento transversal: Frecuencia del análisis de microsecciones por lote de producción.

Grupo 4: Control de Cambios y Entrega

- Política PCN (Product Change Notification): Compromiso de notificar antes de cambiar materiales o subproveedores.

- Proceso EQ (Engineering Question): Cómo manejan las discrepancias de DFM (informe formal vs. correo electrónico).

- Embalaje: Bolsas de barrera contra la humedad (MBB) con tarjetas indicadoras de humedad (HIC) y desecante.

- Logística: Experiencia en el envío internacional de cargas de cobre pesado/envíos de gran peso.

Cómo elegir PCB nativas de IA (compromisos y reglas de decisión)

Cada decisión de ingeniería implica una compensación. Aquí se explica cómo navegar por los conflictos más comunes al especificar arquitecturas de PCB nativas de IA.

- Costo del material vs. Integridad de la señal

- Regla: Si la longitud total de su traza es corta (< 5 pulgadas) y la velocidad es < 25 Gbps, puede usar material "Mid-Loss" (por ejemplo, Isola FR408HR).

- Regla: Si la longitud de la traza es larga o la velocidad es > 25 Gbps, debe elegir material "Ultra-Low Loss" (por ejemplo, Megtron 7). El costo de atenuación de la señal de FR4 requerirá rediseños costosos.

- HDI vs. Agujeros pasantes

- Regla: Si tiene componentes BGA con un paso < 0,65 mm, debe usar HDI (Microvías).

- Regla: Si el paso BGA es > 0,8 mm, quédese con los agujeros pasantes o las vías ciegas simples para reducir el costo de la placa en un 30-50%.

- Backdrilling vs. Vías ciegas

- Regla: Si necesita eliminar stubs en una placa gruesa (3 mm+), el backdrilling es generalmente más rentable que la laminación secuencial (vías ciegas) para una simple eliminación de stubs.

- Regla: Si necesita espacio de enrutamiento en las capas externas por encima de la vía, use Vías Ciegas (Blind Vias).

- Acabado superficial: ENIG vs. OSP

- Regla: Si la fiabilidad y la vida útil son primordiales (Servidor/Centro de datos), elija ENIG.

- Regla: Si la integridad de la señal a frecuencias extremadamente altas (> 50 GHz) es la única prioridad, OSP (Organic Solderability Preservative) no tiene una capa de níquel que cause pérdidas magnéticas, pero el ensamblaje debe realizarse inmediatamente.

- Grosor de la placa vs. Relación de aspecto

- Regla: Si la placa debe ser gruesa (para rigidez/capas), debe aumentar el diámetro de la vía para mantener una relación de aspecto de chapado < 15:1.

- Regla: Si el tamaño de la vía es fijo (pequeño), debe reducir el grosor de la placa o aceptar una mayor pérdida de rendimiento/costo.

Preguntas frecuentes sobre PCB nativos de IA (costo, tiempo de entrega, archivos DFM, materiales, pruebas)

P: ¿Cómo se compara el costo de los PCB nativos de IA con los PCB estándar? R: Espere que los costos sean de 3 a 10 veces más altos que los de las placas FR4 estándar. Esto se debe a materias primas costosas (Megtron/Rogers pueden costar 5 veces el precio de FR4), procesos de bajo rendimiento (HDI, taladrado posterior) y requisitos de prueba extensivos.

P: ¿Cuál es el tiempo de entrega típico para los prototipos de PCB nativos de IA? R: El tiempo de entrega estándar es de 15 a 20 días hábiles debido a los ciclos de laminación secuencial.

- Acelerado: Se puede reducir a 10-12 días con tarifas premium.

- Retraso de material: Siempre verifique el stock de materiales exóticos; el pedido de materiales puede agregar de 2 a 4 semanas si no están en stock. P: ¿Qué archivos DFM específicos se necesitan para el modelado de impedancia de PCB nativos de IA? R: Debe proporcionar un archivo de apilamiento que indique explícitamente la constante dieléctrica (Dk) y el factor de disipación (Df) a la frecuencia de operación (por ejemplo, 10 GHz), no solo el valor de 1 MHz que se encuentra en las hojas de datos genéricas.

P: ¿Podemos mezclar materiales (apilamiento híbrido) para ahorrar costos? R: Sí, esto es común en los diseños de PCB AAU 5G.

- Método: Utilizar material de alta frecuencia costoso para las capas de señal y FR4 más barato para las capas de alimentación/tierra/mecánicas.

- Riesgo: El desajuste del CTE entre materiales puede causar deformaciones; requiere una cuidadosa validación de ingeniería.

P: ¿Cuáles son los criterios de aceptación para la profundidad de retroperforación? R: El estándar de la industria es típicamente "No debe cortar el cobre de la capa objetivo" y "Longitud de stub restante < 10 mils (0,25 mm)". Tolerancias más estrictas (por ejemplo, < 6 mils) aumentan el costo y el riesgo de circuitos abiertos.

P: ¿Cómo se prueba la fiabilidad en las secciones de PCB ADC 5G? R: Más allá de la prueba E estándar, recomendamos pruebas específicas de ruido de fondo y pruebas de intermodulación pasiva (PIM) si el ADC está integrado con líneas de transmisión de RF.

P: ¿Por qué el "thieving" o equilibrado de cobre es crítico para estas placas? R: Las placas de IA suelen ser grandes. La distribución desigual del cobre provoca "alabeo y torsión" durante el reflujo, lo que causa fallos en las uniones de soldadura BGA. Se añade un equilibrado automático de cobre a las áreas vacías para equilibrar el estrés.

P: ¿Necesito especificar IPC Clase 3 para hardware de IA? R: Si bien la Clase IPC 2 es estándar, la mayoría de los propietarios de infraestructuras de IA especifican "Clase IPC 2 con requisitos de chapado de Clase 3" (es decir, cobre más grueso en las vías) para garantizar la fiabilidad a largo plazo sin la carga completa de costos/inspección de la Clase 3.

Recursos para PCB nativos de IA (páginas y herramientas relacionadas)

- Fabricación de PCB de alta velocidad: Profundice en las técnicas de fabricación específicas para la integridad de la señal > 25 Gbps.

- PCB para servidores y centros de datos: Comprenda los estándares de fiabilidad específicos requeridos para entornos operativos 24/7.

- Capacidades de PCB HDI: Aprenda sobre las estructuras de microvías y la laminación secuencial necesarias para chips de IA de alta densidad.

- Calculadora de impedancia: Una herramienta para estimar el ancho y el espaciado de las pistas antes de enviar su apilamiento final.

- Materiales de PCB Panasonic Megtron: Especificaciones para el material de baja pérdida más común utilizado en aceleradores de IA.

- Directrices DFM: Reglas de diseño esenciales para garantizar que su placa de IA sea fabricable a escala.

Solicitar un presupuesto para PCB nativos de IA (revisión DFM + precios)

¿Listo para pasar del diseño a la validación? En APTPCB, proporcionamos una revisión DFM exhaustiva junto con su presupuesto para identificar posibles riesgos de integridad de la señal o de apilamiento antes de que comience la producción.

Para obtener un presupuesto y DFM precisos, por favor, prepare:

- Archivos Gerber/ODB++: Conjunto de datos completo.

- Apilamiento e Impedancia: Número de capas deseado e impedancia objetivo.

- Especificaciones del Material: Requisitos específicos del laminado (por ejemplo, "Megtron 7 o equivalente").

- Volumen: Cantidad de prototipos vs. Objetivos de producción en masa.

Haga clic aquí para solicitar un presupuesto y una revisión DFM

Conclusión: Próximos pasos para PCB AI-Native

El despliegue exitoso de una PCB AI-Native requiere un cambio de mentalidad, de "conectar componentes" a "diseñar un sistema de línea de transmisión". Al definir estrictamente sus especificaciones de materiales, comprender los riesgos de la construcción de múltiples capas y validar la capacidad de su proveedor para manejar el backdrilling y el HDI, puede asegurar la base de hardware en la que confían sus algoritmos de IA. Ya sea que esté construyendo una PCB 5G AAU o un clúster de entrenamiento masivo, la física de la fabricación sigue siendo el guardián final del rendimiento.