La guerra electrónica y las comunicaciones seguras exigen hardware que resista las interferencias intencionadas. Una PCB anti-interferencias no es solo una placa de circuito estándar; es un componente diseñado con precisión para suprimir la interferencia electromagnética (EMI), mantener la integridad de la señal bajo presión y soportar algoritmos de filtrado avanzados. Los ingenieros que diseñan para los sectores de defensa, aeroespacial o industrial de alta seguridad deben adherirse a estrictos protocolos de diseño y materiales para garantizar la resiliencia. APTPCB (Fábrica de PCB APTPCB) se especializa en la fabricación de estas placas de alta fiabilidad, asegurando que las capacidades teóricas anti-interferencias se traduzcan en un rendimiento físico.

PCB anti-interferencias: respuesta rápida (30 segundos)

El diseño de una PCB anti-interferencias robusta requiere centrarse en el aislamiento de la señal y la estabilidad del material.

- Selección de materiales: Utilice laminados de baja pérdida (Rogers, Taconic o Isola) con una constante dieléctrica (Dk) estable en amplios rangos de frecuencia para evitar cambios de fase de la señal.

- Estrategia de conexión a tierra: Implemente un plano de referencia de tierra continuo para cada capa de señal. Utilice "via stitching" (costura de vías) a lo largo de los bordes de la placa y las trazas críticas para crear jaulas de Faraday.

- Control de impedancia: Mantenga tolerancias de impedancia estrictas (típicamente ±5% o ±7%) para minimizar las reflexiones de señal que los inhibidores pueden explotar.

- Aislamiento: Separe físicamente las secciones analógicas (RF) de la lógica digital para evitar que el ruido interno reduzca el umbral de interferencia.

- Blindaje: Integrar huellas para carcasas de blindaje a nivel de placa o utilizar materiales de capacitancia integrada para amortiguar el ruido de alta frecuencia.

- Validación: Verificar el rendimiento mediante pruebas de reflectometría en el dominio del tiempo (TDR) y analizador de redes vectoriales (VNA) durante la fase de prototipo.

Cuándo se aplica la PCB anti-interferencias (y cuándo no)

Comprender el entorno operativo es fundamental antes de comprometerse con los mayores costos de una PCB resistente a interferencias.

Cuándo usar PCB anti-interferencias:

- Sistemas de radar AESA: Los radares de matriz de exploración electrónica activa requieren un control de fase preciso y aislamiento entre miles de módulos de transmisión/recepción.

- Receptores GNSS/GPS: Sistemas de navegación para infraestructuras militares y críticas que deben rechazar las señales de suplantación y de interferencia.

- Radios tácticas seguras: Dispositivos de comunicación que operan en entornos electromagnéticos disputados.

- Subestaciones de alta tensión: Placas de control que deben operar de manera fiable cerca de fuentes masivas de ruido de conmutación.

- Defensa autónoma de drones: UAV que requieren enlaces de control sin compromisos en territorios hostiles.

Cuándo las PCB estándar son suficientes:

- Electrónica de consumo: Los electrodomésticos y juguetes no se enfrentan a amenazas de interferencia intencional.

- Lógica digital de baja velocidad: Los microcontroladores simples que operan por debajo de 50 MHz típicamente no requieren materiales anti-interferencias exóticos.

- Sensores IoT de interior: Los dispositivos en entornos Wi-Fi controlados suelen ser suficientes con FR4 estándar y prácticas básicas de EMI.

- Controles industriales generales: A menos que se coloquen directamente junto a VFD de alta potencia o soldadoras de arco, las placas industriales estándar IPC Clase 2 son adecuadas.

Reglas y especificaciones de PCB anti-interferencias (parámetros clave y límites)

Para lograr una alta supresión de interferencias, el proceso de fabricación debe cumplir con tolerancias estrictas. La siguiente tabla describe las especificaciones críticas para una PCB anti-interferencias eficaz.

| Regla | Valor/Rango recomendado | Por qué es importante | Cómo verificar | Si se ignora |

|---|---|---|---|---|

| Constante dieléctrica (Dk) | 3,0 – 3,5 (Estable ±0,05) | Determina la velocidad de propagación de la señal; la variación causa errores de fase. | Hoja de datos del material y prueba TDR. | El desajuste de fase degrada la precisión de la formación de haces. |

| Factor de disipación (Df) | < 0,002 @ 10 GHz | Minimiza la atenuación de la señal, preservando las señales débiles contra el ruido. | Medición de pérdida de inserción VNA. | La pérdida de señal reduce el alcance efectivo y la sensibilidad. |

| Tolerancia de ancho de pista | ±0,5 mil (±12 µm) | Impacta directamente el control de impedancia. | Análisis de sección transversal (microsección). | El desajuste de impedancia causa reflexiones (VSWR). |

| Paso de costura de vías | < λ/20 de la frecuencia más alta | Crea una jaula de Faraday efectiva para bloquear la EMI lateral. | Inspección visual y revisión de Gerber. | La fuga de RF permite que las señales de interferencia penetren. |

| Rugosidad del cobre | VLP o HVLP (< 2 µm) | Reduce las pérdidas por efecto piel a altas frecuencias. | SEM (Microscopio Electrónico de Barrido). | Pérdida de inserción aumentada en frecuencias mmWave. |

| Registro de capas | ±3 mil (±75 µm) | Asegura la alineación vertical de las estructuras acopladas y las tierras. | Inspección por rayos X. | La desalineación arruina el acoplamiento de banda ancha y la impedancia. |

| Continuidad del plano de tierra | 100% sólido (sin divisiones) | Proporciona una ruta de retorno de baja inductancia. | AOI (Inspección Óptica Automatizada). | Bucles de tierra y alta susceptibilidad a EMI. |

| Pared del orificio pasante chapado (PTH) | > 25 µm de cobre | Asegura una conexión a tierra robusta y fiabilidad térmica. | Análisis de microsección. | Agrietamiento de vías bajo estrés térmico; conexión a tierra intermitente. |

| Malla de máscara de soldadura | > 3 mil (0,075 mm) | Evita puentes de soldadura entre almohadillas de paso fino. | Visual / AOI. | Cortocircuitos en componentes RF de alta densidad. |

| Acabado superficial | ENIG o Plata de inmersión | Proporciona una superficie plana para componentes de paso fino y conductividad por efecto piel. | Fluorescencia de Rayos X (XRF). | Pérdida de señal o malas uniones de soldadura en BGA/QFN. |

Pasos de implementación de PCB anti-interferencias (puntos de control del proceso)

La construcción de una PCB anti-interferencias implica acciones específicas en cada etapa del flujo de trabajo de diseño y fabricación.

- Definir la frecuencia y el perfil de amenaza:

- Acción: Identificar el rango de frecuencia de operación (por ejemplo, banda L, banda X) y los niveles de potencia de interferencia esperados.

- Verificar: Confirmar si el diseño requiere materiales de PCB de alta frecuencia o apilamientos híbridos.

- Seleccionar material del sustrato:

- Acción: Elegir materiales como Rogers RO4350B o RO3003 para las capas de RF, potencialmente uniéndolos con FR4 para las capas digitales para ahorrar costos.

- Verificar: Verificar la compatibilidad del CTE (Coeficiente de Expansión Térmica) entre los materiales híbridos.

- Diseñar el apilamiento:

- Acción: Configurar un apilamiento simétrico con planos de tierra inmediatamente adyacentes a las capas de señal de alta velocidad.

- Verificar: Usar una calculadora de apilamiento de PCB para confirmar los objetivos de impedancia.

- Diseñar trazas críticas (Regla 3W):

- Acción: Enrutar trazas de RF con un espaciado de al menos 3 veces el ancho de la traza (3W) para minimizar la diafonía.

- Verificar: Ejecutar DRC (Design Rule Check) específicamente para el espacio entre trazas.

- Implementar Via Stitching:

- Acción: Colocar vías de tierra a lo largo del perímetro de la placa y alrededor de los bloques de RF sensibles (anillos de guarda).

- Verificar: Asegurarse de que el paso de las vías es lo suficientemente ajustado para bloquear la longitud de onda objetivo.

- Optimizar las rutas de retorno:

- Acción: Asegurarse de que ninguna traza cruce divisiones en el plano de tierra de referencia.

- Verificar: Revisión visual de la capa 2 y la capa 3 (o capas de referencia adyacentes).

- Añadir huellas de blindaje:

- Acción: Diseñar almohadillas de aterrizaje para carcasas de blindaje metálico sobre osciladores sensibles y módulos front-end.

- Verificación: Verificar el espacio libre mecánico para el blindaje en vista 3D.

- Generación de datos de fabricación:

- Acción: Exportar archivos ODB++ o Gerber X2 que contengan tablas de impedancia y especificaciones de materiales.

- Verificación: Incluir un archivo "Read Me" especificando los "requisitos anti-interferencias" y la Clase IPC 3 si es necesario.

Solución de problemas de PCB anti-interferencias (modos de fallo y soluciones)

Incluso con diseños robustos, pueden surgir problemas. Aquí se explica cómo diagnosticar fallos comunes en las implementaciones de PCB anti-interferencias.

- Síntoma: Alta tasa de error de bits (BER) bajo carga.

- Causa: La relación de rechazo de la fuente de alimentación (PSRR) es demasiado baja; el ruido de los rieles de alimentación se acopla a las líneas de RF.

- Verificación: Sondear los rieles de alimentación en busca de rizado; verificar la ubicación de los condensadores de desacoplamiento.

- Solución: Añadir perlas de ferrita y condensadores de bajo ESR cerca de los pines activos; aumentar la capacitancia del plano de alimentación.

- Síntoma: Deriva de la señal o pérdida de bloqueo.

- Causa: Inestabilidad térmica del material dieléctrico (Tcdk alto).

- Verificación: Verificar la temperatura de funcionamiento frente a las especificaciones del material.

- Solución: Cambiar a un material térmicamente estable como la serie Rogers RO4000; mejorar la gestión térmica (disipadores de calor).

- Síntoma: Emisiones espurias inesperadas.

- Causa: Cavidades resonantes formadas entre planos de tierra debido a un insuficiente cosido de vías.

- Verificación: Escaneo con sonda de campo cercano para localizar puntos calientes.

- Solución: Añadir vías de costura "aleatorias" para romper los modos resonantes.

- Síntoma: Pobre aislamiento entre canales (Crosstalk).

- Causa: Las trazas paralelas son demasiado largas o están demasiado cerca.

- Verificación: Revisar el diseño en busca de violaciones de la regla 3W.

- Solución: Separar las trazas con una traza de guarda de tierra; usar señalización diferencial cuando sea posible.

- Síntoma: Desajuste de impedancia (VSWR alto).

- Causa: Sobregrabado durante la fabricación que reduce el ancho de la traza.

- Verificación: Medición TDR y análisis de sección transversal.

- Solución: Ajustar la compensación del ancho de la traza en los archivos CAM; ajustar la tolerancia de grabado en la fábrica.

- Síntoma: Delaminación bajo estrés térmico.

- Causa: CTE no coincidentes en apilamientos híbridos (por ejemplo, PTFE vs. FR4).

- Verificación: Resultados de la prueba de choque térmico.

- Solución: Usar preimpregnados de alto Tg compatibles con el núcleo de RF; ajustar los parámetros del ciclo de laminación.

Cómo elegir una PCB anti-interferencias (decisiones de diseño y compensaciones)

La selección de la configuración correcta para una PCB anti-interferencias implica equilibrar el rendimiento con el costo y la capacidad de fabricación.

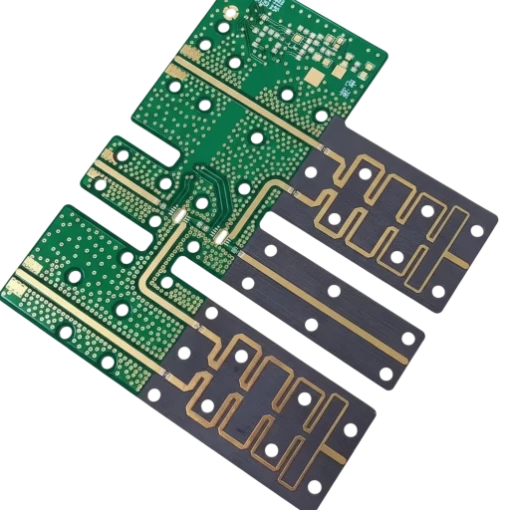

1. Apilamiento híbrido vs. RF puro

- Híbrido: Utiliza material de RF costoso solo en las capas superior/inferior y FR4 estándar para el núcleo.

- Ventajas: Menor costo, suficiente para muchas aplicaciones de banda L/banda S.

- Desventajas: Proceso de laminación complejo; posibles problemas de deformación.

- RF puro: Utiliza material de alta frecuencia uniforme en todo el espesor.

- Pros: Mejor rendimiento eléctrico, CTE consistente.

- Contras: Costo de material significativamente más alto.

2. Selección del Acabado Superficial

- ENIG (Níquel Químico Oro por Inmersión): Buena vida útil y superficie plana. Sin embargo, el níquel es magnético y puede causar intermodulación pasiva (PIM) en circuitos de RF sensibles.

- Plata por Inmersión: Excelente conductividad y no magnético. Ideal para anti-interferencias de alta frecuencia, pero se empaña fácilmente si no se manipula correctamente.

- OSP: El costo más bajo, bueno para RF, pero con una vida útil corta.

3. Blindaje: Latas vs. Integrado

- Latas Metálicas: Tradicionales, efectivas y reparables. Añaden peso y altura.

- Blindaje Integrado/de Cavidad: Fresado de cavidades en la PCB para alojar componentes, luego chapado. Reduce el perfil pero aumenta el costo de fabricación y la complejidad.

4. Tecnología de Vías

- Vías Pasantes: Las más baratas pero crean talones que actúan como antenas a altas frecuencias.

- Vías Perforadas por Detrás: Elimina la porción de talón no utilizada. Esencial para señales > 5 Gbps o > 3 GHz para mantener la integridad de la señal.

Preguntas Frecuentes sobre PCB Anti-Interferencias (costo, tiempo de entrega, defectos comunes, criterios de aceptación, archivos DFM)

P: ¿Cuánto cuesta una PCB Anti-Interferencias en comparación con una PCB estándar? R: Espere que los costos sean de 3 a 10 veces más altos que los de las placas FR4 estándar. El factor principal del precio es el laminado especializado (por ejemplo, Materiales PCB Rogers), requisitos de tolerancia más estrictos (control de impedancia) y, a menudo, la necesidad de ciclos de laminación híbridos.

P: ¿Cuál es el plazo de entrega típico para la fabricación de estas placas? R: El plazo de entrega estándar es de 10 a 15 días hábiles. Si los materiales especializados (como núcleos específicos de Rogers o Taconic) no están en stock, el plazo de entrega puede extenderse a 3-4 semanas. APTPCB almacena materiales de alta frecuencia comunes para acelerar este proceso.

P: ¿Cuáles son los criterios de aceptación para las PCB anti-interferencias? R: La aceptación se basa generalmente en los estándares IPC-6012 Clase 3. Los criterios clave incluyen la verificación de impedancia TDR (aprobado/fallido según la tolerancia), secciones transversales limpias que no muestren delaminación y la superación de pruebas de contaminación iónica para prevenir corrientes de fuga.

P: ¿Puedo usar FR4 estándar para un diseño anti-interferencias? R: Generalmente, no. El FR4 tiene un alto factor de disipación (Df) y una constante dieléctrica (Dk) inestable a altas frecuencias, lo que degrada la integridad de la señal. Sin embargo, el FR4 puede usarse en apilamientos híbridos para capas digitales no críticas.

P: ¿Qué archivos se requieren para una revisión DFM de una PCB anti-interferencias? R: Debe proporcionar archivos Gerber (o ODB++), un dibujo detallado del apilamiento que especifique los tipos de materiales y el orden de las capas, una netlist IPC para la verificación de pruebas eléctricas y un dibujo de perforación que identifique las ubicaciones de perforación trasera, si corresponde.

P: ¿En qué se diferencia una PCB de radar AESA de una PCB anti-interferencias estándar? R: Una PCB de radar AESA es un subconjunto de placas anti-interferencias que requiere una coincidencia de fase extrema entre canales. A menudo implica cientos de capas de complejas redes de formación de haces y exige las tolerancias de grabado más estrictas posibles para asegurar que todos los elementos de la antena irradien en fase perfecta.

P: ¿Cuál es el defecto más común en las PCB resistentes a interferencias? R: El defecto más común es la "discontinuidad de impedancia". Esto ocurre cuando los anchos de las trazas varían durante el grabado o cuando los planos de referencia se interrumpen, causando reflexiones de la señal que reducen la capacidad del sistema para filtrar el ruido de interferencia.

P: ¿APTPCB ofrece pruebas de rendimiento anti-interferencias? R: Realizamos pruebas eléctricas a nivel de placa (abierto/cortocircuito) y pruebas de impedancia (TDR). Las pruebas funcionales anti-interferencias (simulación de interferencias) suelen ser realizadas por el cliente a nivel de ensamblaje del sistema, ya que requieren software y hardware propietarios.

P: ¿Cómo ayudan los condensadores enterrados en los diseños anti-interferencias? A: Las capas de capacitancia enterradas (que utilizan dieléctricos muy delgados entre la alimentación y la tierra) proporcionan un excelente desacoplamiento de alta frecuencia. Esto reduce la impedancia de la red de distribución de energía (PDN), disminuyendo el ruido que de otro modo podría desensibilizar el receptor.

P: ¿Cuál es el impacto de la rugosidad de la superficie en estas PCB? R: A frecuencias superiores a 10 GHz, la corriente fluye principalmente a lo largo de la "piel" del conductor. El cobre rugoso aumenta la longitud del camino, lo que lleva a una mayor pérdida de inserción. Recomendamos cobre VLP (Very Low Profile) para todos los diseños anti-interferencias de alta frecuencia.

Recursos para PCB anti-interferencias (páginas y herramientas relacionadas)

Para optimizar aún más su diseño, consulte estos recursos específicos:

- Aplicación industrial: PCB para Aeroespacial y Defensa – Estándares y requisitos para placas de grado militar.

- Datos de materiales: Materiales de PCB Rogers – Especificaciones para los sustratos anti-interferencias más comunes.

- Guía de diseño: PCB de Alta Frecuencia – Reglas generales para circuitos de RF y microondas.

- Planificación de apilamiento: Apilamiento de PCB – Cómo organizar las capas para una integridad de señal óptima.

Glosario de PCB anti-interferencias (términos clave)

| Término | Definición | Relevancia para anti-interferencias |

|---|---|---|

| EMI (Interferencia Electromagnética) | Perturbación generada por una fuente externa que afecta un circuito eléctrico. | La principal amenaza que una PCB anti-interferencias está diseñada para resistir. |

| Control de Impedancia | Mantenimiento de una resistencia específica a las señales de CA (ej., 50Ω) a lo largo de una pista. | Evita las reflexiones de señal que los inhibidores pueden explotar para degradar el rendimiento. |

| Jaula de Faraday | Un cerramiento formado por material conductor (o vías) para bloquear campos electromagnéticos. | Utilizada en PCBs mediante vías de unión para aislar secciones de RF sensibles. |

| Dk (Constante Dieléctrica) | Una medida de la capacidad de un material para almacenar energía eléctrica en un campo eléctrico. | La estabilidad de Dk es crucial para mantener la precisión de fase en sistemas de radar. |

| Df (Factor de Disipación) | Una medida de la tasa de pérdida de potencia en un material dieléctrico. | Se requieren materiales de bajo Df para preservar señales débiles en entornos de interferencia. |

| Crosstalk (Diafonía) | Transferencia de señal no deseada entre canales de comunicación. | Debe minimizarse para evitar que el ruido interno reduzca el umbral de interferencia. |

| Back-drilling (Taladrado posterior) | Eliminación de la porción no utilizada de un orificio pasante chapado (stub). | Elimina las reflexiones de señal en enlaces de alta velocidad/alta frecuencia. |

| Apilamiento Híbrido | Un apilamiento de PCB que utiliza diferentes materiales (ej., Rogers + FR4). | Equilibra el costo y el rendimiento para sistemas anti-interferencias complejos. |

| Efecto piel | La tendencia de la corriente de alta frecuencia a fluir cerca de la superficie de un conductor. | Requiere perfiles de cobre lisos para minimizar las pérdidas. |

| TDR (Reflectometría en el Dominio del Tiempo) | Una técnica de medición utilizada para determinar la impedancia de las trazas de PCB. | El método estándar para verificar la calidad de fabricación de las placas de RF. |

Solicite una cotización para PCB Anti-Jamming (revisión DFM + precios)

¿Listo para pasar del diseño al prototipo? APTPCB ofrece revisiones DFM exhaustivas para garantizar que su PCB Anti-Jamming cumpla con todas las especificaciones de impedancia y materiales antes de que comience la producción.

Para obtener la cotización más precisa, proporcione:

- Archivos Gerber: Formato RS-274X o ODB++.

- Plano de Fabricación: Incluya detalles del apilamiento, requisitos de materiales (por ejemplo, Rogers 4350B) y tablas de impedancia.

- Cantidad y Plazo de Entrega: Volumen de prototipo o producción en masa.

- Requisitos Especiales: Contraperforación, inspección de Clase 3 o acabados superficiales específicos.

Conclusión: Próximos pasos para el PCB Anti-Jamming

El despliegue exitoso de una PCB anti-interferencias requiere una sinergia entre técnicas de diseño avanzadas y fabricación de precisión. Al controlar estrictamente las propiedades de los materiales, la impedancia y el blindaje, los ingenieros pueden construir sistemas que mantienen la integridad en los entornos electromagnéticos más hostiles. Ya sea para radar AESA o comunicaciones seguras, la elección del fabricante es tan crítica como el propio diseño. Asegúrese de que su socio tenga la capacidad de manejar apilamientos híbridos y requisitos de RF de tolerancia estricta para garantizar el éxito de la misión.