Un buen diseño de placa de equilibrado BMS suele marcar la diferencia entre un paquete multicelda estable y otro que pierde capacidad útil con el tiempo. Si no igualas correctamente las celdas, un bloque de baterías de litio (Li‑ion o LiFePO4) conectado en serie terminará con desajustes de SOC y tensión, lo que puede causar cortes prematuros, degradación acelerada e incluso riesgo de fuga térmica.

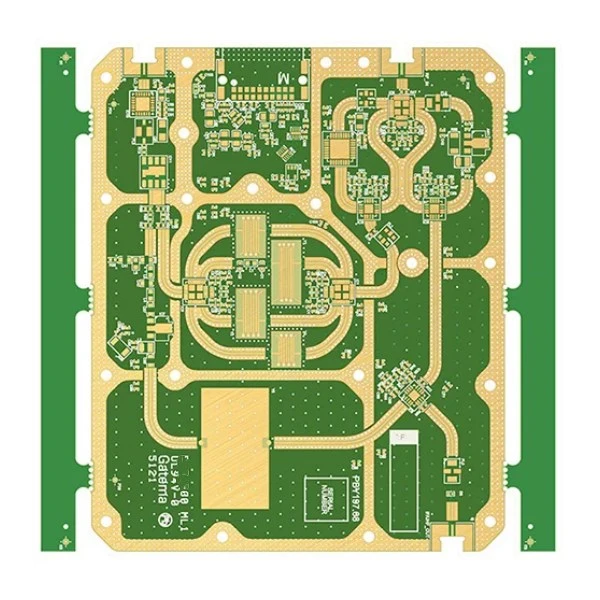

En APTPCB (fábrica de PCB APTPCB) vemos con frecuencia errores repetidos: medición de tensión contaminada por caída IR y acoplamientos, y problemas térmicos alrededor de resistencias de descarga y MOSFETs. Esta guía reúne reglas prácticas, parámetros recomendados y un marco de resolución de problemas para que tu placa BMS sea robusta y fabricable (DFM).

Diseño de placa de equilibrado BMS: respuesta rápida (30 segundos)

Si necesitas una síntesis, aplica estos puntos primero:

- Ajusta la corriente de equilibrado a la capacidad: en pasivo, suele ser razonable apuntar a ~1% de la capacidad de la celda (tasa C) para corregir la deriva (p. ej., 50 mA–100 mA en paquetes pequeños y ≥1 A en almacenamientos grandes).

- Prioriza la disipación térmica: el equilibrado pasivo convierte energía en calor. Usa planos de cobre, vías térmicas y, si hace falta, PCB de cobre pesado para alejar los puntos calientes de las celdas.

- Rutea en Kelvin para medir bien: separa líneas de sensado de los caminos de potencia; si no, la caída IR distorsiona la lectura.

- No subestimes referencia/ADC: una precisión mejor que 0.1% es un buen objetivo; un error de ~10 mV puede recortar capacidad útil de forma apreciable.

- Protección a prueba de fallos: añade protecciones redundantes (sobretensión/sobretemperatura) que no dependan del firmware principal.

Cuándo se aplica (y cuándo no) el diseño de equilibrado BMS

El nivel de diseño necesario depende del producto y del bloque de baterías: hay casos donde es imprescindible, y otros donde es un compromiso de coste.

Cuándo conviene diseñarlo con rigor:

- Packs en serie (≥2S): a partir de 2S la deriva entre celdas es inevitable con el uso.

- Alta vida útil por ciclos: EV, ESS y robótica/industrial (1000+ ciclos) requieren equilibrado estable.

- Lotes de celdas mezclados: si no puedes evitarlo, el equilibrado activo ayuda a compensar diferencias de impedancia.

- Carga rápida: altas tasas C amplifican los desajustes; sin buen equilibrado una celda llega antes al punto de corte.

Cuándo puede ser limitado o no necesario:

- 1S: no hay equilibrado entre celdas, solo protección.

- Productos de muy bajo costo: algunos aceptan menor vida útil para reducir BOM.

- Plomo‑ácido (a veces): puede existir cierta auto‑igualación, aunque en bancos grandes se prefiere control electrónico.

- Baterías primarias: no aplica a químicas no recargables.

Reglas y especificaciones (parámetros clave y límites)

Esta tabla resume reglas típicas para un diseño de placa de equilibrado BMS que funcione de forma estable bajo corriente y temperatura.

| Regla / Parámetro | Valor / Rango recomendado | Por qué importa | Cómo verificar | Si se ignora |

|---|---|---|---|---|

| Corriente de equilibrado | 0.5% a 2% de la capacidad (Ah) | Debe corregir la deriva más rápido de lo que aparece. | Calcular corriente del resistor a $V_{cell,max}$. | Bloque desbalanceado; cae la capacidad útil. |

| Ancho líneas de sensado | 6–10 mil (0.15–0.25 mm) | Solo señal; evita efectos parásitos innecesarios. | Revisión del ruteo (Gerber). | Ruido; lecturas inestables. |

| Ancho pistas de potencia | Calculado para $\Delta T < 10^\circ C$ | Evita sobrecalentamiento en descarga/equilibrado. | Calculadora IPC‑2152 según corriente. | Delaminación; fallo de pista; riesgo de incendio. |

| Potencia del resistor de descarga | Potencia nominal > 2× disipación real | Margen de seguridad para evitar deriva o fallo por temperatura. | Hoja de datos vs. $P=V^2/R$. | El resistor falla; el equilibrado deja de funcionar. |

| MOSFET Rds(on) | < 10 mΩ (para alta corriente) | Reduce pérdidas y puntos calientes. | Hoja de datos + estimación térmica. | El MOSFET se calienta y falla en abierto o cortocircuito. |

| Exactitud de tensión | ±2 mV a ±5 mV | Define inicio/fin del equilibrado. | Comparación con multímetro calibrado. | Sobrecarga o no se activa el equilibrado. |

| Separación térmica | > 5 mm de las celdas | Evita calentar la química del bloque de baterías. | Revisión 3D + cámara térmica. | Degradación acelerada; riesgo. |

| Distancia de aislamiento | > 0.5 mm por 100 V | Reduce arco en stacks HV (>60 V). | Creepage/clearance en CAD. | Cortocircuito; fallo catastrófico. |

| Condensadores de filtro | 100 nF–1 µF en líneas de sensado | Filtra ruido HF (motor/inversor). | Osciloscopio en nodos ADC/sense. | Lecturas erráticas; disparos falsos. |

| Tg del PCB | Tg alto (>170°C) | Resiste mejor estrés térmico del pasivo. | Selección por datasheet. | Alabeo; rotura de vías. |

| Recubrimiento conformal | Acrílico o silicona | Protección ante condensación y fugas. | Inspección bajo UV. | Corrosión; cortos en humedad. |

Pasos de implementación (puntos de control del proceso)

Usa estos pasos para convertir el concepto en un diseño de placa de equilibrado BMS realmente fabricable.

Define química y número de series:

- Li‑ion (3.6 V/4.2 V), LiFePO4 (3.2 V/3.65 V) o LTO: fija umbrales y márgenes.

- Verificación: confirmar que la tensión máxima del stack no supera la rigidez dieléctrica de los componentes.

Elige topología de equilibrado:

- Pasivo (descarga resistiva) o activo (transferencia capacitiva/inductiva). El pasivo suele bastar por debajo de 100 W; el activo se justifica por eficiencia y paquetes grandes.

- Verificación: validar coste, tamaño y complejidad.

Calcula la corriente objetivo:

- Estimar desajuste por auto‑descarga (típicamente 2–3%/mes) y dimensionar $R = V_{cell}/I_{balance}$.

- Verificación: comprobar que equilibra dentro de la ventana real de carga.

Selección de componentes y márgenes de seguridad:

- Resistencias de descarga (potencia/impulso) y MOSFETs con umbral de compuerta adecuado si se accionan desde el IC.

- Verificación: rangos de temperatura (-40°C a +105°C si aplica) y márgenes de tensión/corriente.

Esquemático y simulación:

- Añadir filtros RC en las líneas de sensado; simular para evitar picos que dañen el controlador.

- Verificación: alinear tensión de activación con umbrales e histéresis.

Layout (enfoque térmico):

- Alejar resistencias de descarga del MCU y sensores; usar planos de cobre y vías térmicas como disipador.

- Verificación: revisar guías de PCB de alta conductividad térmica.

Ruteo de sensado (Kelvin):

- Rutea sensado separado de potencia; conecta lo más cerca posible de terminales, idealmente en modo diferencial.

- Verificación: evitar lazos de conmutación de alta corriente paralelos a las líneas de sensado.

Fabricación de prototipo:

- Pedir lote pequeño y confirmar peso de cobre (p. ej., 2 oz/3 oz).

- Verificación: realizar FAI (inspección de primer artículo) de colocación y polaridad.

Pruebas funcionales:

- Comprobar activación a umbral exacto; usar cámara térmica y mantener puntos calientes típicamente <60°C–80°C.

- Verificación: validar que el equilibrado se detiene al caer por debajo del límite de histéresis.

Solución de problemas (modos de fallo y correcciones)

Síntoma: las celdas siguen desbalanceadas tras carga completa

- Causas: corriente demasiado baja; carga termina antes de tiempo; error de medida.

- Comprobaciones: medir corriente real; verificar que el punto de corte del cargador no está por debajo del umbral de inicio.

- Solución: bajar R (subir corriente); ajustar estrategia de carga; recalibrar.

- Prevención: dimensionar por el peor caso de mismatch.

Síntoma: decoloración del PCB u olor a quemado

- Causas: resistencias sobrecargadas; pistas pequeñas; poco cobre.

- Comprobaciones: termografía; comprobar $P=V^2/R$.

- Solución: subir potencia, aumentar cobre, mejorar ventilación.

- Prevención: aplicar margen de seguridad (p. ej., 50%) y, si es extremo, PCB de núcleo metálico.

Síntoma: lecturas de tensión inestables

- Causas: ruido en sensado; masa deficiente; aliasing.

- Comprobaciones: osciloscopio en ADC; buscar bucles de masa.

- Solución: aumentar RC (p. ej., 1 kΩ + 100 nF); alejar de nodos de conmutación.

- Prevención: sensado diferencial + estrategia de planos de masa.

Síntoma: MOSFET de equilibrado en corto (siempre ON)

- Causas: ESD; pico de sobretensión; sobretemperatura.

- Comprobaciones: medir Gate‑Source y Drain‑Source; revisar TVS/diody si cargas inductivas.

- Solución: sustituir MOSFET; añadir TVS.

- Prevención: $V_{ds}$ ≥ 1.5× $V_{cell,max}$ y resistor de gate para suavizar conmutación.

Síntoma: el BMS corta antes de tiempo

- Causas: caída IR en sensado; falso disparo de sobretensión.

- Comprobaciones: comparar tensión en terminales vs lectura BMS bajo carga.

- Solución: mejorar Kelvin; optimizar ruteo de sensado.

- Prevención: considerar resistencia de conectores/arnés.

Síntoma: el bloque se descarga en almacenamiento

- Causas: alta corriente en reposo; MOSFETs con fuga; residuos de flux.

- Comprobaciones: medir corriente en reposo; inspección de fugas o cortocircuitos parciales.

- Solución: ICs ultra‑low‑power; limpieza.

- Prevención: modo sleep robusto + proceso de limpieza estricto.

Cómo elegir (Pasivo vs Activo)

1. Pasivo (descarga resistiva)

- Mecanismo: disipa energía de la celda más alta como calor.

- Pros: bajo coste, simple, compacto, fiable.

- Contras: baja eficiencia (calor), corriente limitada (normalmente <200 mA), lento en paquetes grandes.

- Mejor para: e‑bikes, herramientas, portátiles, consumo.

- Enfoque: la térmica manda.

2. Activo (transferencia de energía)

- Mecanismo: transfiere energía a celdas más bajas mediante capacitores o inductores.

- Pros: alta eficiencia (>90%), poca calor, corrientes altas (1 A–10 A), más capacidad útil.

- Contras: caro, control complejo, más área, mayor riesgo EMI.

- Mejor para: EV, sistemas ESS grandes y paquetes de alto valor.

- Enfoque: frecuencia de conmutación y apantallamiento EMI.

Matriz de decisión: Si tu bloque < 20 Ah y el coste es clave, elige Pasivo. Si tu bloque > 50 Ah o la eficiencia es crítica, elige Activo. Entre 20 Ah y 50 Ah, decide según restricciones térmicas del gabinete.

Preguntas frecuentes (costo, lead time, DFM)

P: ¿Cuál es el impacto típico de costo por añadir equilibrado? R: En pasivo suele ser bajo (resistencias + MOSFETs), aprox. $0.50–$2.00 por serie según volumen. En activo, inductores/transformadores y control elevan el costo, a menudo $10–$30+ por placa.

P: ¿Afecta al lead time del PCB? R: Diseños pasivos estándar suelen mantenerse en 5–10 días. Si necesitas cobre pesado (3 oz+) o materiales high‑Tg, añade 3–5 días.

P: ¿Criterios de aceptación en ensamblaje? R: AOI, ICT y prueba funcional simulando entradas de celda. Corriente dentro de ±10% del objetivo y fuga por debajo del umbral (normalmente <10 µA).

P: ¿Qué archivos DFM debo enviar? R: Gerbers (RS‑274X), Centroid/PnP, BOM y una nota con requisitos de aislamiento/ruptura, además de zonas para conformal coating a evitar (contactos, test points).

P: ¿Se puede usar FR4 estándar? R: Sí en muchos pasivos de baja corriente. Para >500 mA o alta densidad térmica, se recomienda FR4 high‑Tg (Tg 170). Para calor extremo, considera PCB de núcleo de aluminio o metal.

P: ¿Cómo probar sin baterías reales? R: Con simulador de celdas o fuentes de precisión; una escalera de resistencias también sirve para provocar desequilibrio controlado.

P: ¿Mejor acabado superficial? R: ENIG suele ser el preferido: planitud para paso fino y buena resistencia a corrosión.

P: ¿Cómo manejar rutas de alta corriente? R: Polígonos/planos en lugar de pistas finas; dimensionar al corriente del bloque. Para 50 A+, barras colectoras y/o cobre pesado.

P: ¿Por qué aparece un zumbido? R: Coil‑whine o MLCCs “cantando” en activo; en pasivo, PWM en 20 Hz–20 kHz también puede ser audible. Subir frecuencia ayuda a menudo.

P: ¿APTPCB realiza FCT? R: Sí, podemos implementar FCT según tu procedimiento y requisitos de fixture.

Recursos (páginas relacionadas)

- Soluciones de PCB para potencia y energía: capacidades para electrónica de batería/energía.

- Directrices DFM: lista de verificación para preparar producción.

- Servicios de ensamblaje SMT: proceso para ICs BMS de paso fino y potencia.

Glosario (términos clave)

| Término | Definición |

|---|---|

| Equilibrado de celdas | Igualar tensión y SOC de celdas en un bloque en serie. |

| Equilibrado pasivo | Disipar energía de la celda más alta como calor mediante un resistor de descarga. |

| Equilibrado activo | Transferir energía de celdas altas a bajas con C/L. |

| BMS (sistema de gestión de batería) | Sistema electrónico que supervisa y protege la batería o el bloque. |

| SOC (estado de carga) | Nivel de carga relativo a la capacidad (en %). |

| SOH (estado de salud) | Indicador del estado o envejecimiento frente al nominal. |

| Resistencia de descarga | Resistencia de potencia usada para descargar una celda en pasivo. |

| Conexión Kelvin (4 hilos) | Medición que elimina el efecto de resistencias de cableado. |

| OCV (Open Circuit Voltage) | Tensión en bornes sin carga (sin corriente). |

| C‑Rate | Tasa de carga/descarga relativa a la capacidad nominal. |

| Fuga térmica | Aumento de temperatura auto‑acelerado hasta fallo. |

| Histéresis | Diferencia entre umbral de inicio y de parada para evitar oscilación. |

Solicite un presupuesto para una placa de equilibrado BMS

¿Listo para llevar tu placa de equilibrado BMS de prototipo a producción? APTPCB puede revisar DFM para detectar riesgos térmicos y de ruteo antes de industrializar. Envíanos Gerbers, BOM y requisitos de prueba para un presupuesto detallado en 24 horas.

Conclusión (siguientes pasos)

Un diseño BMS fiable requiere disciplina en térmica, precisión de medida, márgenes de seguridad en componentes y DFM. Tanto si eliges pasivo (barato, pero caliente) como activo (eficiente, pero complejo), el diseño de PCB dicta la seguridad y la vida útil del bloque de baterías. Aplica las reglas, puntos de control y pasos de resolución de problemas anteriores para llegar a pruebas y producción con menos sorpresas.