La computación de alto rendimiento exige tasas de transferencia de datos más rápidas entre chips heterogéneos, lo que convierte el control de impedancia de la placa de interconexión EMIB en un factor crítico en el encapsulado moderno de semiconductores. A medida que los diseños avanzan hacia el encapsulado 2.5D y las arquitecturas de chiplets, los límites tradicionales entre la PCB y el sustrato del paquete se difuminan. Garantizar la integridad de la señal a través del puente incrustado y el sustrato orgánico circundante requiere una ejecución de fabricación precisa. Esta guía proporciona un flujo de trabajo completo para ingenieros y equipos de adquisiciones para gestionar la impedancia en estas interconexiones avanzadas.

Puntos Clave

- Definición: El control de impedancia de la placa de interconexión EMIB se refiere al mantenimiento de una impedancia característica específica (generalmente 85Ω o 100Ω diferencial) a través de la transición del puente de silicio al sustrato orgánico.

- Métrica Crítica: La pérdida de retorno y la pérdida de inserción son tan importantes como el valor de impedancia objetivo ($Z_0$) en la integración de chiplets de alta velocidad.

- Impacto del Material: La desadaptación en la constante dieléctrica ($D_k$) entre el puente de silicio y las capas de construcción de la PCB es la fuente principal de reflexión de la señal.

- Concepto Erróneo: Muchos asumen que las tolerancias estándar de PCB (+/- 10%) son suficientes; sin embargo, los diseños EMIB a menudo requieren un control de +/- 5% o más estricto.

- Validación: Las pruebas de reflectometría en el dominio del tiempo (TDR) deben realizarse en cupones de prueba específicos que imiten la transición de puente a placa, no solo en cupones de traza estándar.

- Consejo de fabricación: Controlar la rugosidad de la superficie del cobre es esencial para minimizar las pérdidas por efecto pelicular a frecuencias superiores a 25 GHz.

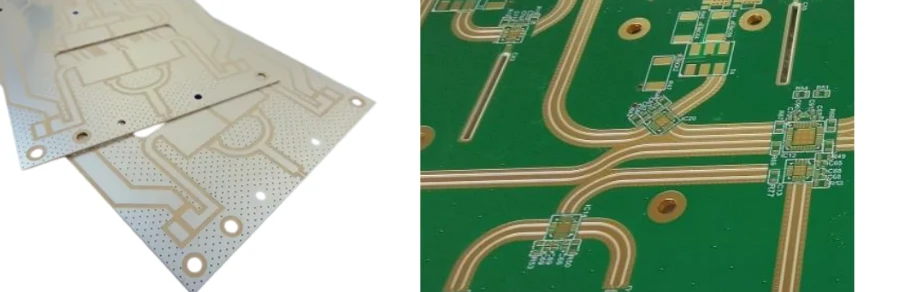

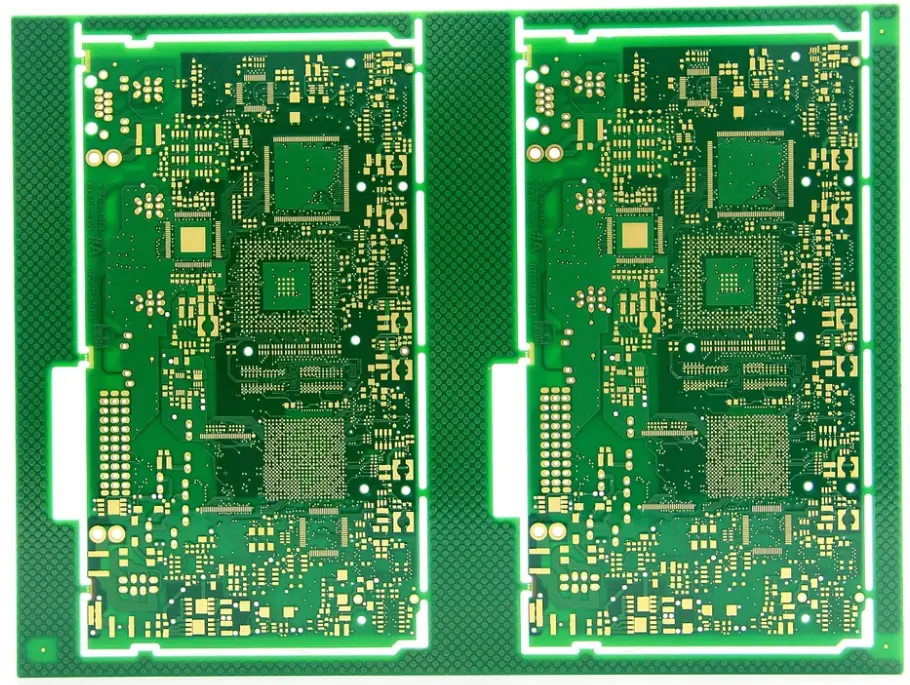

- APTPCB (APTPCB PCB Factory) se especializa en los procesos de PCB HDI y tipo sustrato de alta precisión necesarios para soportar estas arquitecturas de encapsulado avanzadas.

Qué significa realmente el control de impedancia de la placa de interconexión EMIB

Comprender la definición central es el primer paso antes de analizar métricas específicas y tolerancias de fabricación.

El control de impedancia de la placa de interconexión EMIB es la disciplina de ingeniería que gestiona la resistencia eléctrica a las señales de CA a medida que viajan entre el puente de silicio incrustado y el sustrato del paquete orgánico. A diferencia de las PCB estándar donde las trazas corren sobre capas uniformes de fibra de vidrio, una estructura EMIB (Embedded Multi-die Interconnect Bridge) implica un entorno híbrido. Las señales deben atravesar desde un dado de silicio, a través de micro-bumps, hacia un puente de silicio y de allí hacia el sustrato del paquete. La "placa de interconexión" en este contexto actúa como el portador. Debe coincidir con la impedancia del enrutamiento de paso ultrafino en el puente de silicio. Si la impedancia no coincide en la interfaz, se producen reflexiones de señal. Estas reflexiones causan corrupción de datos, aumento de las tasas de error de bits (BER) y reducción de la eficiencia energética. Para APTPCB, lograr este control significa utilizar técnicas avanzadas de HDI (Interconexión de Alta Densidad), microvías láser y materiales dieléctricos ultrafinos que cierran la brecha entre la fabricación de semiconductores y la fabricación tradicional de PCB.

Métricas de control de impedancia de la placa de interconexión EMIB que importan

Una vez que se define el alcance del control de impedancia, los ingenieros deben cuantificar la calidad utilizando indicadores de rendimiento específicos.

El éxito de un diseño de placa de interconexión EMIB se basa en la estricta adherencia a las métricas de integridad de la señal. En aplicaciones de alta velocidad como aceleradores de IA o procesadores de centros de datos, un simple "aprobado/fallido" en la resistencia es insuficiente. Debe evaluar cómo se comporta la placa en todo un espectro de frecuencias.

| Métrica | Por qué es importante | Rango típico / Factores | Cómo medir |

|---|---|---|---|

| Impedancia Característica ($Z_0$) | Determina si la ruta de la señal coincide con la fuente y la carga. Los desajustes causan reflexiones. | 85Ω o 100Ω (Diferencial); 50Ω (De un solo extremo). Tolerancia: ±5% a ±10%. | Reflectometría en el Dominio del Tiempo (TDR) en cupones de prueba. |

| Pérdida de inserción | Mide cuánta potencia de señal se pierde a medida que viaja a través de la interconexión. | < -1,5 dB por pulgada a la frecuencia de Nyquist. Muy influenciado por la rugosidad del cobre y $D_k$. | Analizador de red vectorial (VNA) o extracción de parámetros S. |

| Pérdida de retorno | Mide la cantidad de señal reflejada de vuelta a la fuente debido a discontinuidades de impedancia. | < -10 dB a -15 dB es deseable. Cuanto menor, mejor. | VNA (parámetro S11). |

| Sesgo (Intra-par) | La diferencia de retardo de tiempo entre las líneas positiva y negativa de un par diferencial. | < 5 ps (picosegundos). Crítico para la señalización diferencial. | TDR u osciloscopio. |

| Estabilidad de la constante dieléctrica ($D_k$) | Las variaciones en $D_k$ causan fluctuaciones de impedancia a lo largo de la traza. | $D_k$ estable en todas las frecuencias (por ejemplo, 3,0 - 3,5 para sustratos avanzados). | Verificación de la hoja de datos del material y anillos resonadores. |

| Rugosidad de la superficie del cobre | El cobre rugoso aumenta la resistencia a altas frecuencias (efecto pelicular). | $R_z$ < 2 µm (se recomienda lámina de cobre VLP o HVLP). | Perfilómetro o SEM (Microscopio Electrónico de Barrido). |

Cómo elegir el control de impedancia de la placa de interconexión EMIB: guía de selección por escenario

Con las métricas establecidas, el siguiente desafío es seleccionar la estrategia de control adecuada según el escenario de aplicación específico. Diferentes casos de uso final requieren distintos niveles de rigor en el control de impedancia de la placa de interconexión EMIB. La sobreespecificación añade costes innecesarios, mientras que la infraespecificación conduce a fallos del sistema.

Escenario 1: Computación de alto rendimiento (HPC) e IA

- Requisito: Ancho de banda máximo (integración HBM).

- Compromiso: Requiere la tolerancia de impedancia más estricta (±5%) y materiales de muy baja pérdida.

- Orientación: Elija películas de acumulación avanzadas (ABF) y cobre HVLP. El coste es secundario a la hora de priorizar el rendimiento.

Escenario 2: Dispositivos móviles de consumo

- Requisito: Miniaturización y duración de la batería.

- Compromiso: Las limitaciones de espacio obligan a utilizar dieléctricos más delgados, lo que dificulta el control de la impedancia.

- Orientación: Priorice los materiales de núcleo delgado. Acepte tolerancias ligeramente más holgadas (±7-10%) para mantener el rendimiento y reducir costes.

Escenario 3: Sistemas ADAS automotrices

- Requisito: Fiabilidad y estabilidad térmica.

- Compromiso: Los materiales deben soportar ciclos térmicos, que pueden desplazar la impedancia con el tiempo.

- Orientación: Seleccione materiales de alto Tg con $D_k$ estable en amplios rangos de temperatura. La validación debe incluir pruebas de estrés térmico.

Escenario 4: Infraestructura 5G / Estaciones base

- Requisito: Alta frecuencia y baja latencia.

- Compromiso: Las largas longitudes de traza en el sustrato aumentan los riesgos de pérdida de inserción.

- Orientación: Concéntrese en laminados "Low Loss" y "Ultra Low Loss". El control de impedancia debe tener en cuenta las bandas de frecuencia específicas (mmWave).

Escenario 5: Prototipo / NPI (Introducción de Nuevo Producto)

- Requisito: Velocidad de entrega y depuración.

- Compromiso: Los plazos de entrega rápidos pueden limitar la disponibilidad de materiales.

- Orientación: Utilice materiales de alta velocidad estándar disponibles. Concéntrese en validar la lógica del diseño en lugar de una optimización perfecta de la impedancia.

Escenario 6: Producción en Masa (Sensible al Costo)

- Requisito: Rendimiento y eficiencia de costos.

- Compromiso: No puede mantener tolerancias ultraajustadas sin altas tasas de desecho.

- Orientación: Diseño para la Fabricación (DFM). Ensanchar las trazas donde sea posible para hacer que la impedancia sea menos sensible a las variaciones de grabado.

Puntos de control para la implementación del control de impedancia de la placa de interconexión EMIB

Después de seleccionar la estrategia correcta, el enfoque se desplaza a la ejecución táctica, desde los archivos de diseño hasta el producto final.

La implementación del control de impedancia de la placa de interconexión EMIB requiere un esfuerzo sincronizado entre el ingeniero de diseño y el área de fabricación. Utilice esta lista de verificación para asegurarse de que no se omita ningún paso crítico durante el proceso de fabricación de PCB HDI.

- Definición del Apilamiento:

- Recomendación: Definir explícitamente el número de capas, los espesores dieléctricos y los pesos de cobre.

- Riesgo: Los apilamientos ambiguos conducen a cálculos de impedancia incorrectos por parte del ingeniero CAM.

- Aceptación: Hoja de apilamiento aprobada firmada tanto por el diseñador como por el fabricante.

Selección de materiales:

- Recomendación: Especificar la serie exacta del material (por ejemplo, Megtron 6, Rogers o películas ABF específicas).

- Riesgo: Las designaciones genéricas "FR4" fallarán a velocidades EMIB.

- Aceptación: Certificación de material (CoC) del proveedor.

Ancho y espaciado de trazas (L/S):

- Recomendación: Ajustar el ancho de traza en CAM para compensar los factores de grabado (forma trapezoidal).

- Riesgo: El sobregrabado reduce el ancho de traza, aumentando la impedancia.

- Aceptación: Análisis de sección transversal (microsección) que verifica la geometría.

Continuidad del plano de referencia:

- Recomendación: Asegurar planos de tierra sólidos debajo de las señales de alta velocidad, especialmente cerca de la interfaz del puente.

- Riesgo: Las divisiones en el plano de referencia causan discontinuidades de impedancia inmediatas.

- Aceptación: Inspección Óptica Automatizada (AOI) de las capas internas.

Registro de microvías:

- Recomendación: La alineación de la perforación láser debe ser precisa para conectar las almohadillas del puente al sustrato.

- Riesgo: La desalineación cambia el acoplamiento capacitivo, alterando la impedancia.

- Aceptación: Inspección por rayos X de la alineación de las vías.

Espesor del chapado de cobre:

- Recomendación: Mantener una distribución uniforme del chapado.

- Riesgo: Las variaciones en el espesor del cobre afectan la inductancia total de la línea.

- Aceptación: Medición de espesor no destructiva (CMI).

Aplicación del acabado superficial:

- Recomendación: Usar ENIG o ENEPIG para superficies planas adecuadas para wire bonding o flip-chip.

- Riesgo: Los acabados HASL gruesos crean superficies irregulares y variaciones de impedancia.

- Aceptación: Medición del espesor del acabado superficial (XRF).

Compensación de grabado:

- Recomendación: La fábrica debe aplicar una compensación global de grabado basada en el peso del cobre.

- Riesgo: El grabado inconsistente en todo el panel conduce a variaciones de impedancia entre unidades.

- Aceptación: Prueba de cupón de impedancia en los bordes del panel.

Efecto de la máscara de soldadura:

- Recomendación: Considerar el $D_k$ de la máscara de soldadura en el cálculo de la impedancia (para capas externas).

- Riesgo: La máscara de soldadura reduce la impedancia en 2-3 ohmios; ignorar esto causa fallos.

- Aceptación: Medición TDR después de la aplicación de la máscara de soldadura.

Validación TDR final:

- Recomendación: Pruebas al 100% de los cupones de impedancia para lotes críticos.

- Riesgo: Envío de placas que pasan la continuidad eléctrica pero fallan la integridad de la señal.

- Aceptación: Informe TDR que muestre aprobado/reprobado frente a la tolerancia.

Errores comunes en el control de impedancia de las placas de interconexión EMIB

Incluso con una lista de verificación, con frecuencia ocurren errores específicos en el complejo entorno de la fabricación de puentes integrados.

Evitar estos errores comunes en el control de impedancia de las placas de interconexión EMIB puede ahorrar semanas de tiempo de rediseño y miles de dólares en desechos.

- Ignorar la "Zona de Transición": La discontinuidad de impedancia más crítica ocurre donde la señal se mueve del puente de silicio al sustrato de la PCB. Los diseñadores a menudo igualan la impedancia de la traza pero ignoran la capacitancia parasitaria de la almohadilla/bump de aterrizaje. Corrección: Simule la transición en solucionadores de campo 3D y optimice el apilamiento de almohadillas.

- Usar Constantes Dieléctricas Genéricas: Confiar en el valor $D_k$ "de marketing" (por ejemplo, 4.0) en lugar del valor dependiente de la frecuencia (por ejemplo, 3.8 a 10 GHz). Corrección: Solicite la tabla de materiales dependientes de la frecuencia a APTPCB.

- Descuidar los Modelos de Rugosidad del Cobre: Los calculadores de impedancia estándar asumen cobre liso. A velocidades EMIB, la rugosidad añade un retraso y una pérdida significativos. Corrección: Utilice el modelo de Huray o factores de corrección de rugosidad similares en los cálculos.

- Cupones de Prueba Inadecuados: Colocar los cupones de prueba demasiado lejos del circuito real o usar diseños que no coinciden con la densidad real de las trazas. Corrección: Use cupones incrustados o estructuras de prueba "en circuito" siempre que sea posible.

- Pasar por Alto las Tolerancias de Fabricación: Diseñar una línea de 50 ohmios que requiere una traza de 3.1 mil, cuando la capacidad mínima de la fábrica es de 3 mil +/- 0.5 mil. Corrección: Consulte el Calculador de Impedancia y las reglas de diseño con antelación.

- No tener en cuenta las áreas ricas en resina: En sustratos heterogéneos, la resina puede acumularse en los huecos entre las trazas, cambiando el $D_k$ local. Corrección: Utilice un relleno de cobre ficticio (thieving) para asegurar una distribución y prensado uniformes de la resina.

Preguntas frecuentes sobre el control de impedancia de la placa de interconexión EMIB

Para finalizar los detalles técnicos, aquí están las respuestas a las preguntas más apremiantes sobre logística y ejecución.

P: ¿Cómo afecta el control estricto de la impedancia de la placa de interconexión EMIB al costo general? R: Reducir las tolerancias de ±10% a ±5% puede aumentar los costos entre un 15% y un 25%. Esto se debe a la necesidad de materiales de mayor calidad, pruebas TDR más frecuentes y menores rendimientos de fabricación.

P: ¿Cuál es el plazo de entrega típico para prototipos de placas de interconexión EMIB con requisitos de impedancia? R: Los plazos de entrega estándar son de 15 a 20 días. Sin embargo, si se requieren materiales especializados de baja pérdida o películas ABF, los plazos de entrega pueden extenderse a 4-6 semanas dependiendo de la disponibilidad del material.

P: ¿Qué materiales son los mejores para el control de impedancia de la placa de interconexión EMIB a 56 Gbps? R: El FR4 estándar no es adecuado. Debe utilizar materiales como Panasonic Megtron 6/7, Isola Tachyon o películas Ajinomoto Build-up (ABF) especializadas que ofrecen una baja tangente de pérdida ($D_f$) y un $D_k$ estable.

P: ¿Cómo se realizan las pruebas para las capas enterradas en un sustrato EMIB? A: Probar las capas enterradas es difícil en la placa terminada. Utilizamos "cupones de prueba" ubicados en los rieles del panel que tienen la misma estructura de capa y geometría de traza que la placa real. Estos se prueban mediante TDR antes de que las capas externas sean laminadas o después de la fabricación final.

Q: ¿Cuáles son los criterios de aceptación para las pruebas TDR en estas placas? A: El criterio de aceptación estándar es que la impedancia medida debe caer dentro de la tolerancia especificada (por ejemplo, 100Ω ±10%). Además, la forma de onda TDR debe ser suave, sin caídas o picos pronunciados que indiquen discontinuidades.

Q: ¿Puedo usar vías estándar para el diseño de placas de interconexión EMIB? A: Generalmente, no. Los diseños EMIB requieren un enrutamiento de alta densidad que necesita microvías láser, vías ciegas y vías enterradas para gestionar la integridad de la señal y la densidad. Las perforaciones mecánicas suelen ser demasiado grandes y crean demasiada capacitancia parasitaria.

Q: ¿Cómo especifico el control de impedancia en mis archivos Gerber? A: No confíe únicamente en los nombres de archivo Gerber. Incluya un dibujo de fabricación detallado (Fab Drawing) que enumere las capas específicas, los anchos de traza, los planos de referencia y los valores de impedancia objetivo para cada grupo de señales.

Q: ¿Cuál es la diferencia entre impedancia single-ended y diferencial en este contexto? A: La impedancia de un solo extremo (single-ended) hace referencia a una pista con respecto a un plano de tierra (normalmente 50Ω). La impedancia diferencial hace referencia a dos pistas entre sí y al plano de tierra (normalmente 85Ω o 100Ω). Las rutas de datos EMIB son casi exclusivamente diferenciales para rechazar el ruido.

Recursos para el control de impedancia de las placas de interconexión EMIB

- Fabricación de PCB de alta velocidad: Explore las capacidades de fabricación de placas que soportan altas tasas de datos.

- Calculadora de impedancia: Una herramienta para estimar el ancho y el espaciado de las pistas para su impedancia objetivo.

- Tecnología PCB HDI: Conozca las tecnologías de microvías y líneas finas esenciales para los sustratos EMIB.

- Diseño de apilamiento de PCB: Pautas para organizar las capas y lograr una integridad de señal óptima.

Glosario de control de impedancia de las placas de interconexión EMIB

| Término | Definición |

|---|---|

| EMIB | Embedded Multi-die Interconnect Bridge. Una tecnología que utiliza un puente de silicio incrustado en un sustrato para conectar chips. |

| Impedancia ($Z_0$) | La oposición que un circuito presenta al paso de una corriente cuando se aplica un voltaje. |

| TDR | Reflectometría en el Dominio del Tiempo. Una técnica de medición utilizada para determinar la impedancia de una línea. |

| Microvía | Un pequeño orificio perforado con láser (típicamente < 150µm) para conectar capas adyacentes en placas HDI. |

| ABF | Película Ajinomoto Build-up. Un material aislante dominante utilizado en sustratos de CI para CPU/GPU de alto rendimiento. |

| CTE | Coeficiente de Expansión Térmica. La velocidad a la que un material se expande con el calor. Las desadaptaciones causan problemas de fiabilidad. |

| Insertion Loss | Pérdida por Inserción. La pérdida de potencia de la señal resultante de la inserción de un dispositivo (o traza) en una línea de transmisión. |

| Return Loss | Pérdida de Retorno. La pérdida de potencia en la señal devuelta/reflejada por una discontinuidad en una línea de transmisión. |

| Differential Pair | Par Diferencial. Dos señales complementarias utilizadas para transmitir datos, ofreciendo alta inmunidad al ruido. |

| Skin Effect | Efecto Pelicular. La tendencia de la corriente alterna de alta frecuencia a distribuirse cerca de la superficie del conductor. |

| Dielectric Constant ($D_k$) | Constante Dieléctrica ($D_k$). Una medida de la capacidad de un material para almacenar energía eléctrica en un campo eléctrico. Afecta la velocidad de la señal y la impedancia. |

| Loss Tangent ($D_f$) | Tangente de Pérdidas ($D_f$). Una medida de la potencia de la señal perdida como calor dentro del material dieléctrico. |

| RDL | Capa de Redistribución. Capas metálicas en un chip o sustrato que redirigen los pads de E/S a diferentes ubicaciones. |

Conclusión: Próximos pasos para el control de impedancia de la placa de interconexión EMIB

Dominar el control de impedancia de las placas de interconexión EMIB es un requisito previo para competir en la era de los chiplets y la integración heterogénea. Requiere un cambio de mentalidad, de "conectar puntos" a "gestionar líneas de transmisión". Al comprender las métricas de pérdida de inserción y pérdida de retorno, seleccionar los materiales adecuados y aplicar estrictos puntos de control de fabricación, puede asegurarse de que sus diseños de alto rendimiento funcionen según lo previsto.

Si está listo para llevar su diseño del concepto a la producción, APTPCB está lista para ayudarle. Para obtener una revisión DFM precisa y un presupuesto, por favor, proporcione lo siguiente:

- Archivos Gerber (RS-274X) o datos ODB++.

- Diagrama de apilamiento que indique los materiales deseados y el número de capas.

- Requisitos de impedancia (por ejemplo, Capa 3, 100Ω Diferencial, Ancho de traza 4mil).

- Netlist para la validación de pruebas eléctricas.

Visite nuestra Página de presupuesto para iniciar su proyecto hoy mismo.