Diseño de PCB de interfaz EtherCAT: definición, alcance y a quién va dirigida esta guía

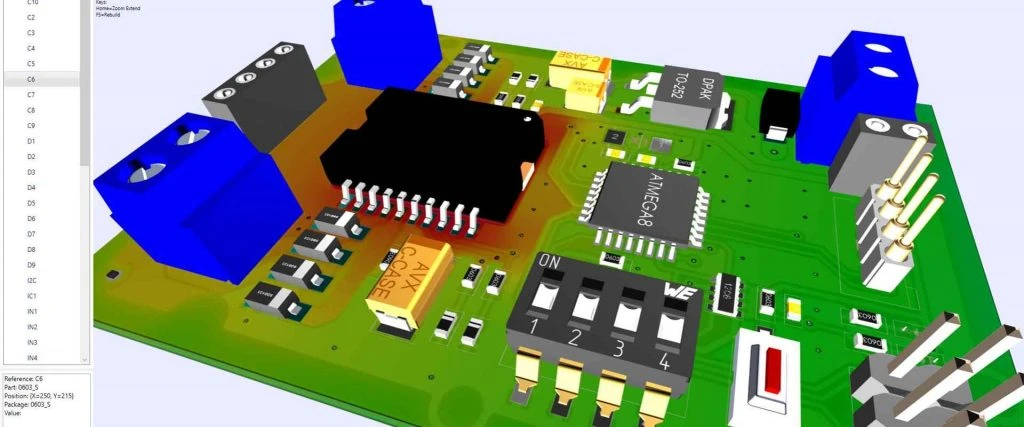

El diseño de PCB de interfaz EtherCAT se refiere a los procesos especializados de ingeniería y diseño necesarios para implementar el protocolo EtherCAT (Ethernet for Control Automation Technology) en una placa de circuito impreso. A diferencia del Ethernet de oficina estándar, EtherCAT opera en entornos industriales hostiles que requieren transmisión de datos en tiempo real con sincronización a nivel de microsegundos. El alcance de este trabajo de diseño abarca el diseño de la capa física (PHY), el enrutamiento de pares diferenciales, el control de impedancia, el aislamiento magnético y estrategias de conexión a tierra robustas para evitar la pérdida de paquetes en entornos eléctricamente ruidosos.

Este manual está escrito para ingenieros de hardware, líderes de adquisiciones técnicas y gerentes de producto que están haciendo la transición de un prototipo a la producción en masa. Va más allá de la teoría esquemática básica para centrarse en la fabricabilidad, la fiabilidad y la validación de la cadena de suministro. Encontrará especificaciones prácticas para incluir en su documentación, un desglose de los modos de fallo comunes durante la ampliación y una lista de verificación rigurosa para garantizar que su socio de fabricación pueda ofrecer una calidad constante. En APTPCB (APTPCB PCB Factory), a menudo vemos que los diseños fallan no por errores lógicos, sino por problemas de diseño físico que comprometen la integridad de la señal bajo estrés. Esta guía tiene como objetivo cerrar la brecha entre una hoja de datos funcional y un producto robusto y listo para el campo. Al seguir estos pasos, se reduce el riesgo de interrupciones de comunicación (errores CRC) y se asegura que su equipo de automatización industrial cumpla con los estrictos estándares de fiabilidad esperados en el mercado.

Cuándo usar el diseño de PCB de interfaz EtherCAT (y cuándo un enfoque estándar es mejor)

Comprender las demandas específicas de los protocolos industriales es el primer paso antes de sumergirse en las especificaciones técnicas de su placa.

Si bien las directrices de diseño de Ethernet estándar proporcionan una base, el diseño de PCB de interfaz EtherCAT es obligatorio cuando su aplicación implica control de movimiento, robótica o E/S en tiempo real donde la latencia debe ser determinista. Ethernet estándar (TCP/IP) puede tolerar paquetes reenviados y latencia variable; EtherCAT no. Si un paquete se pierde o se retrasa debido a una mala integridad de la señal, todo el bucle de control puede fallar, causando tiempo de inactividad de la máquina. Por lo tanto, si su dispositivo actúa como esclavo o maestro EtherCAT en un entorno de automatización de fábrica, debe adoptar las estrictas prácticas de impedancia y blindaje que se describen aquí. Por el contrario, un enfoque de diseño Ethernet estándar, menos riguroso, podría ser suficiente para puertos de datos administrativos o interfaces de registro no en tiempo real donde el entorno está controlado (por ejemplo, una sala de servidores) y una latencia ocasional es aceptable. Sin embargo, para los puertos EtherCAT reales (IN/OUT), el enfoque "estándar" es a menudo una receta para fallos intermitentes en el campo. El costo de un diseño especializado es insignificante en comparación con el costo de depurar la pérdida intermitente de sincronización en una máquina industrial desplegada.

Especificaciones de diseño de PCB de interfaz EtherCAT (materiales, apilamiento, tolerancias)

Una vez que haya determinado que es necesaria una implementación robusta de EtherCAT, el siguiente paso es traducir las necesidades de rendimiento en especificaciones de fabricación concretas.

Definir estos requisitos con antelación evita la "ingeniería por suposición" donde el fabricante adivina sus necesidades. Incluya estas 8–12 especificaciones en su plano de fabricación y RFQ para asegurar que el diseño de la PCB de interfaz EtherCAT se ejecute correctamente:

- Control de impedancia diferencial: Especifique 100Ω ±10% para todos los pares diferenciales (TX+/TX-, RX+/RX-). Este es el factor más crítico para la integridad de la señal.

- Impedancia de terminación simple: Defina 50Ω ±10% para las líneas de reloj y datos MII/RMII/RGMII que conectan el controlador esclavo EtherCAT (ESC) al PHY.

- Estrategia de apilamiento de PCB: Exigir una placa de 4 capas como mínimo para cualquier diseño EtherCAT. Las capas 2 y 3 deben servir como planos sólidos de tierra y alimentación para proporcionar una ruta de retorno para las señales de alta velocidad.

- Peso del cobre: El estándar de 1 oz (35µm) suele ser suficiente para las capas de señal, pero asegúrese de que los planos de alimentación puedan manejar la corriente si la placa también acciona motores o E/S pesadas.

- Selección de materiales: Utilice FR-4 High Tg (Tg > 170°C) si el dispositivo funciona en armarios industriales con altas temperaturas ambiente. Un Tg estándar (130-140°C) puede causar agrietamiento del barril (barrel cracking) bajo ciclos térmicos.

- Ancho y espaciado de las trazas: Indique explícitamente el ancho y el espaciado de las trazas requeridos para lograr la impedancia objetivo basándose en el apilamiento del proveedor. Típicamente, esto es alrededor de 4-6 mil de ancho / 5-8 mil de espaciado.

- Coincidencia de longitud de pares (Skew): Requerir que el skew intra-par sea inferior a 5 mils (0,127 mm) para evitar cambios de fase que cierren el ojo de datos.

- Coincidencia de longitud entre pares: Mantenga los pares de transmisión y recepción coincidentes dentro de 2 pulgadas (50 mm), aunque esto es menos crítico que el skew intra-par.

- Tensión de aislamiento: Especifique un espacio libre en el diseño de PCB para soportar un aislamiento de 1,5 kVrms entre la tierra del chasis (blindaje) y la tierra digital, típicamente logrado a través de los magnéticos y un vacío físico en los planos de la PCB.

- Tipos de vías: Especifique vías pasantes estándar. Evite las vías ciegas/enterradas a menos que la densidad lo exija absolutamente, ya que aumentan el costo y la complejidad sin beneficiar la integridad de la señal a 100 Mbps.

- Acabado superficial: Elija ENIG (Níquel Químico Oro por Inmersión) para pads planos, lo que ayuda con la soldadura precisa de chips PHY de paso fino y conectores RJ45.

- Color de la máscara de soldadura: Aunque a menudo es estético, evite las máscaras mate negras o blancas para los prototipos iniciales, ya que dificultan la inspección visual de las pistas; el verde o el azul son preferibles para NPI (New Product Introduction).

Riesgos de fabricación del diseño de PCB de interfaz EtherCAT (causas raíz y prevención)

Con las especificaciones definidas, ahora debe anticipar dónde podría fallar el diseño al pasar de 5 prototipos a 5.000 unidades.

Los riesgos de escalado en el diseño de PCB de interfaz EtherCAT a menudo provienen de variaciones de proceso y factores estresantes ambientales que no aparecieron en el banco de pruebas.

- Desajuste de impedancia debido a la variación de grabado:

- Por qué sucede: Durante la producción en masa, el sobregrabado puede estrechar las pistas, aumentando la impedancia por encima de 110Ω.

- Detección: Reflexiones de señal, aumento de la tasa de error de bits (BER).

- Prevención: Requerir cupones TDR (Time Domain Reflectometry) en cada panel de producción y solicitar un informe TDR.

- Fallo de arranque del oscilador de cristal:

- Por qué sucede: La capacitancia parásita de los residuos de fundente o un mal diseño impiden que el reloj PHY arranque de forma fiable.

- Detección: El dispositivo no logra conectarse periódicamente o está inoperativo al llegar.

- Prevención: Mantenga las trazas del cristal ultracortas (<10 mm), rodéelas con anillos de guarda de tierra y asegúrese de que el proceso de ensamblaje de la PCB incluya un lavado exhaustivo (si no se utiliza fundente no-clean).

- Daño por ESD al PHY:

- Por qué ocurre: Los entornos industriales tienen alta estática. Si los diodos TVS se colocan demasiado lejos del conector, el pico golpea primero al PHY.

- Detección: Fallo permanente del puerto después de la manipulación o instalación.

- Prevención: Coloque los dispositivos de protección ESD inmediatamente al lado de los pines del conector. Dirija las señales a través de las almohadillas de protección, no solo las "derive".

- Saturación o fallo de los magnéticos:

- Por qué ocurre: Uso de magnéticos discretos de baja calidad o RJ45 integrados que no pueden manejar el sesgo de CC o temperaturas extremas.

- Detección: La pérdida de paquetes aumenta significativamente a altas temperaturas.

- Prevención: Valide los magnéticos según la lista recomendada por el fabricante del PHY. No cambie los magnéticos por un "equivalente más barato" sin realizar pruebas.

- Bucles de tierra / Problemas de blindaje:

- Por qué ocurre: Acoplamiento incorrecto entre la tierra del chasis y la tierra digital (por ejemplo, falta del circuito paralelo de resistencia de 1MΩ + condensador).

- Detección: La comunicación se interrumpe cuando se encienden motores cercanos o VFDs.

- Prevención: Siga estrictamente las pautas de "Bob Smith Termination" y aislamiento. Asegúrese de que el blindaje RJ45 esté conectado a la Tierra del Chasis (Chassis Ground), no directamente a la Tierra Digital (Digital Ground).

- Fatiga mecánica del conector:

- Por qué ocurre: Los conectores RJ45 dependen de las uniones de soldadura para su resistencia mecánica. Los cables pesados vibran en entornos industriales, agrietando las uniones.

- Detección: Conexión intermitente cuando se mueve el cable.

- Prevención: Utilice conectores con pestañas de blindaje pasantes para el anclaje mecánico, incluso si los pines de señal son SMT.

- Estrangulamiento térmico del PHY:

- Por qué ocurre: Los PHY modernos se calientan mucho. Si la PCB carece de vías térmicas debajo de la almohadilla expuesta (paquetes QFN), el calor se acumula.

- Detección: Caídas de enlace después de 30-60 minutos de operación.

- Prevención: Coloque una densa matriz de vías térmicas conectadas al plano de tierra directamente debajo del componente PHY.

- Discontinuidades del plano de referencia:

- Por qué ocurre: Enrutamiento de pares diferenciales sobre una división en el plano de tierra (por ejemplo, cruzando de áreas de plano de 3.3V a 5V).

- Detección: Altas emisiones EMI y mala integridad de la señal.

- Prevención: Asegúrese de que los pares diferenciales corran sobre un plano de referencia de tierra sólido e ininterrumpido en toda su longitud.

- Sesgo por efecto de tejido de fibra:

- Por qué ocurre: En líneas de muy alta velocidad (Gigabit EtherCAT G), el patrón de tejido de vidrio en FR4 puede hacer que una pata del par viaje más rápido que la otra.

- Detección: Jitter y cierre del diagrama de ojo.

- Prevención: Para EtherCAT estándar de 100 Mbps, esto es raro. Para Gigabit, enrute las trazas con un ligero ángulo (zigzag) en relación con el tejido.

- Residuos de fundente bajo BGA/QFN:

- Por qué sucede: Una limpieza deficiente debajo de componentes de baja holgura provoca corrientes de fuga.

- Detección: Operación inestable en ambientes húmedos.

- Prevención: Utilice casas de ensamblaje de buena reputación con procesos de lavado verificados o pastas sin limpieza calificadas.

Validación y aceptación del diseño de PCB de interfaz EtherCAT (pruebas y criterios de aprobación)

La prevención de riesgos requiere un plan de validación estructurado que confirme que el diseño de PCB de interfaz EtherCAT cumple con todos los requisitos físicos y funcionales.

Este plan debe ejecutarse durante la fase NPI (Introducción de Nuevos Productos) antes de la aprobación para la producción en masa.

- Verificación de impedancia TDR:

- Objetivo: Confirmar la precisión de fabricación de las trazas.

- Método: Medir cupones de prueba proporcionados por el fabricante de PCB.

- Criterios: 100Ω ±10% para pares diferenciales; 50Ω ±10% para señales de un solo extremo.

- Prueba de resistencia DC y continuidad:

- Objetivo: Asegurar que no haya aperturas/cortocircuitos en la ruta de la señal.

- Método: Prueba automatizada de sonda volante o lecho de agujas.

- Criterios: 100% de aprobación en todas las redes.

- Prueba de integridad de la señal (diagrama de ojo):

- Objetivo: Validar la calidad de la señal física.

- Método: Utilice un osciloscopio con una sonda diferencial en los pines TX del PHY.

- Criterios: El "ojo" debe estar bien abierto, cumpliendo los requisitos de la máscara IEEE 802.3. Sin sobreimpulso >10%.

- Prueba de tasa de error de paquetes (BERT):

- Objetivo: Probar la fiabilidad funcional a lo largo del tiempo.

- Método: Ejecute un bucle maestro EtherCAT enviando millones de paquetes durante 24-48 horas.

- Criterios: Cero paquetes perdidos (errores CRC) durante la duración.

- Prueba de estrés térmico:

- Objetivo: Verificar la estabilidad bajo calor.

- Método: Opere el dispositivo en una cámara a la temperatura máxima nominal (por ejemplo, 85°C) durante 4 horas.

- Criterios: Sin caídas de enlace; la temperatura del PHY permanece dentro de los límites de la hoja de datos.

- Prueba de vibración/choque:

- Objetivo: Validar la robustez mecánica del conector.

- Método: Perfil de vibración aleatoria (por ejemplo, 5-500Hz) mientras el enlace está activo.

- Criterios: Sin grietas físicas; sin pérdida momentánea de enlace.

- Escaneo de pre-cumplimiento EMC/EMI:

- Objetivo: Asegurar que el dispositivo no irradie ruido excesivo.

- Método: Escaneo con sonda de campo cercano sobre el conector y el área PHY.

- Criterios: Las emisiones deben estar 3-6dB por debajo de las líneas límite de Clase A/B.

- Prueba de inmunidad ESD:

- Objetivo: Verificar los diodos de protección.

- Método: Aplique descarga por contacto (±4kV) y descarga por aire (±8kV) al blindaje y los pines del conector.

- Criterios: El dispositivo puede reiniciarse pero debe recuperarse automáticamente; sin daños permanentes.

- Prueba de aislamiento (Hi-Pot):

- Objetivo: Verificar el aislamiento galvánico.

- Método: Aplicar 1500V CA entre el lado del cable Ethernet y el lado del circuito.

- Criterios: Corriente de fuga < 1mA; sin ruptura.

- Verificación de interoperabilidad:

- Objetivo: Asegurar la compatibilidad con diferentes maestros.

- Método: Conectar a TwinCAT (Beckhoff), Omron y otros maestros estándar.

- Criterios: Enumeración exitosa y transición al estado Operacional (OP).

Lista de verificación de calificación de proveedores para el diseño de PCB de interfaz EtherCAT (RFQ, auditoría, trazabilidad)

Para ejecutar el plan de validación con éxito, necesita un socio de fabricación capaz de cumplir con sus estrictos requisitos de diseño de PCB de interfaz EtherCAT.

Utilice esta lista de verificación para evaluar a los proveedores potenciales. Si no pueden responder a estas preguntas con confianza, probablemente no sean adecuados para la electrónica de comunicación industrial.

Grupo 1: Entradas de RFQ para el diseño de PCB de interfaz EtherCAT (Lo que usted envía)

- Archivos Gerber: Formato RS-274X, claros y sin errores.

- Dibujo de fabricación: Indicando claramente los requisitos de IPC Clase 2 o 3.

- Definición de apilamiento: Orden explícito de las capas, tipo de material y grosor.

- Tabla de impedancia: Listado de capa, ancho de traza, espaciado e impedancia objetivo.

- Tabla de perforación: Definiendo los tamaños de orificio terminados y las tolerancias.

- Archivo Pick & Place: Datos de centroide para el ensamblaje.

- BOM (Lista de Materiales): Con lista de proveedores aprobados (AVL) para piezas críticas como PHYs y Magnéticos.

- Requisitos de prueba: Instrucciones específicas para pruebas TDR y funcionales.

Grupo 2: Evidencia de capacidad para el diseño de PCB de interfaz EtherCAT (Lo que deben demostrar)

- Control de impedancia: ¿Pueden lograr una tolerancia de ±10%? ¿Tienen equipo TDR propio?

- Traza/Espacio mínimo: ¿Pueden grabar de forma fiable 4mil/4mil si es necesario para PHYs de alta densidad?

- Stock de materiales: ¿Disponen de FR4 de alta Tg y materiales adecuados para temperaturas industriales?

- Ensamblaje de paso fino: ¿Pueden manejar QFNs o BGAs con paso de 0,5 mm utilizados para controladores EtherCAT?

- Inspección por rayos X: ¿Tienen capacidad de rayos X para inspeccionar las uniones de soldadura debajo de los chips QFN/BGA?

- Recubrimiento conforme: ¿Ofrecen servicios de recubrimiento para protección en entornos hostiles?

Grupo 3: Sistema de Calidad y Trazabilidad

- Certificaciones: ISO 9001 es obligatorio; IATF 16949 es un plus para el sector industrial/automotriz.

- Estándares IPC: ¿Capacitan a su personal según IPC-A-600 (PCB) e IPC-A-610 (Ensamblaje)?

- Control de calidad de entrada: ¿Cómo verifican la autenticidad de los chips (para evitar PHYs falsos)?

- Inspección de pasta de soldar (SPI): ¿Se utiliza SPI en cada placa para prevenir defectos de soldadura?

- AOI (Inspección Óptica Automatizada): ¿Se realiza AOI después del reflujo?

- Trazabilidad: ¿Pueden rastrear un número de serie de PCB específico hasta el lote de laminado crudo utilizado?

Grupo 4: Control de cambios y entrega

- PCN (Notificación de Cambio de Producto): ¿Le notificarán antes de cambiar la marca de la máscara de soldadura o el proveedor de laminado?

- EQ (Preguntas de Ingeniería): ¿Revisan los archivos y hacen preguntas de DFM antes de comenzar? (El silencio es una señal de alarma).

- Plazo de entrega: ¿Es el plazo de entrega consistente para los volúmenes que espera?

- Embalaje: ¿Utilizan embalajes seguros contra ESD, sellados al vacío y con desecante?

- Logística: ¿Pueden enviar DDP (Delivered Duty Paid) si usted es internacional?

Cómo elegir el diseño de PCB de interfaz EtherCAT (compensaciones y reglas de decisión)

En el diseño de PCB de interfaz EtherCAT, la ingeniería es el arte del compromiso. Aquí le mostramos cómo navegar por las compensaciones comunes.

- Magnéticos integrados (MagJack) vs. Magnéticos discretos:

- Si prioriza el ahorro de espacio y la facilidad de diseño: Elija MagJacks integrados. Ahorran espacio en la placa y reducen el recuento de componentes.

- Si prioriza el rendimiento térmico y la fiabilidad del aislamiento: Elija Magnéticos discretos. Permiten una mejor disipación del calor y mayores clasificaciones de voltaje de aislamiento, a menudo preferidos en entornos de alta vibración.

- Apilamiento de 4 capas vs. 6 capas:

- Si prioriza el costo: Elija 4 capas. Es suficiente para la mayoría de los diseños EtherCAT de 100 Mbps si se enruta con cuidado.

- Si prioriza el rendimiento EMI y la densidad: Elija 6 capas. Los planos de tierra adicionales proporcionan un blindaje superior y un enrutamiento más sencillo para ESC complejos con muchos GPIO.

- Conectores M12 vs. Conectores RJ45:

- Si prioriza la protección IP67 (agua/polvo): Elija conectores M12. Son el estándar para el cableado industrial "fuera del armario".

- Si prioriza el costo y el cableado estándar: Elija conectores RJ45. Son omnipresentes y económicos, pero generalmente requieren un entorno IP20 (armario limpio).

- Diseño blindado (STP) vs. no blindado (UTP):

- Si prioriza la inmunidad al ruido: Diseñe para blindado (STP). Asegúrese de que el blindaje del conector esté correctamente conectado a tierra al chasis.

- Si prioriza el costo del cableado: Diseñe para no blindado (UTP). Sin embargo, EtherCAT recomienda encarecidamente cables blindados en zonas industriales.

- Acabado superficial Oro Duro vs. ENIG:

- Si prioriza la durabilidad de la inserción del conector (contactos de borde): Elija Oro Duro.

- Si prioriza la soldabilidad de los componentes SMT: Elija ENIG. Para la mayoría de las placas EtherCAT, ENIG es la opción estándar a menos que la propia PCB se conecte a un backplane.

Preguntas frecuentes sobre el diseño de PCB de interfaz EtherCAT (DFM](/es/resources/dfm-guidelines) – Reglas completas de diseño para la fabricación (DFM), apilamiento, impedancia, inspección AOI)

P: ¿Puedo enrutar las señales EtherCAT en la capa inferior? A: Sí, siempre que tenga un plano de referencia de tierra sólido adyacente a la capa inferior (por ejemplo, la Capa 3 en una placa de 4 capas). Evite enrutar señales de alta velocidad en capas externas sin un plano de referencia.

Q: ¿Cuál es la longitud máxima de la pista para los pares diferenciales EtherCAT? A: Si bien el estándar permite cables largos (100 m), las pistas de PCB deben mantenerse lo más cortas posible para minimizar la atenuación. Idealmente, mantenga las pistas de PHY a Magnetics por debajo de 4 pulgadas (100 mm).

Q: ¿Necesito terminar los pares no utilizados en el conector RJ45? A: Sí. Para EtherCAT de 10/100 Mbps, los pares no utilizados (4,5 y 7,8) deben terminarse a tierra a través de resistencias de terminación "Bob Smith" (75Ω) y un condensador de alta tensión para reducir las EMI.

Q: ¿Cómo manejo la "Tierra de Chasis" vs la "Tierra de Señal"? A: La Tierra de Señal (GND) es para sus chips. La Tierra de Chasis/Tierra de Protección es para el blindaje. Conéctelos cerca del conector usando una resistencia de 1MΩ y un condensador de 1-2kV en paralelo para drenar la estática pero bloquear los bucles de ruido de baja frecuencia.

Q: ¿Es realmente necesario el control de impedancia para pistas cortas? A: Sí. Incluso en pistas cortas, los desajustes de impedancia causan reflexiones. Si bien una pista de 1 cm podría no fallar inmediatamente, reduce el margen de ruido, haciendo que el dispositivo sea susceptible al ruido industrial externo.

Q: ¿Puedo usar un PHY Ethernet estándar para EtherCAT? R: Generalmente, sí. EtherCAT utiliza capas físicas estándar IEEE 802.3. Sin embargo, asegúrese de que el PHY sea compatible con la interfaz MII/RMII requerida por su controlador de esclavo EtherCAT (ESC) específico.

P: ¿Cuál es la mejor manera de enrutar los pares diferenciales? R: Enrútelos estrechamente acoplados (juntos), simétricos y evite las vías si es posible. Si se necesitan vías, colóquelas cerca de los pines y asegúrese de que las vías de tierra estén cerca para mantener la ruta de retorno.

P: ¿Por qué falla mi dispositivo EtherCAT cuando arranca el motor? R: Es probable que sea un problema de conexión a tierra. El ruido del motor se acopla a su placa. Verifique la terminación de su blindaje y asegúrese de que su línea de reinicio al PHY no esté captando ruido (agregue un condensador al pin de reinicio).

Recursos para el diseño de PCB de interfaz EtherCAT (páginas y herramientas relacionadas)

Para ayudarle aún más en su proceso de diseño y adquisición, utilice estos recursos:

- Fabricación de PCB para control industrial – Comprenda los requisitos más amplios para las placas de grado industrial más allá de la interfaz.

- Calculadora de impedancia – Una herramienta rápida para estimar el ancho y el espaciado de sus trazas antes de finalizar el apilamiento.

- Directrices DFM – Reglas completas de diseño para la fabricación (DFM) para garantizar que su diseño sea construible a escala.

- Ensamblaje de PCB llave en mano – Descubra cómo la combinación de fabricación y ensamblaje de PCB puede reducir los riesgos logísticos para NPI complejos.

- Diseño de PCB de alta velocidad – Información técnica más profunda sobre la integridad de la señal para protocolos de alta frecuencia.

Solicitar una cotización para el diseño de PCB de interfaz EtherCAT (DFM](/es/resources/dfm-guidelines) – Reglas completas de diseño para la fabricación (DFM) + precios)

¿Listo para llevar su diseño de PCB de interfaz EtherCAT del concepto a la realidad? APTPCB ofrece una revisión DFM gratuita con cada cotización para detectar problemas de impedancia y diseño antes de que se conviertan en desechos costosos.

Qué enviar para una cotización precisa:

- Archivos Gerber (RS-274X)

- BOM (para ensamblaje)

- Requisitos de apilamiento e impedancia

- Necesidades de cantidad y tiempo de entrega

Haga clic aquí para solicitar una cotización y una revisión DFM

Conclusión: Próximos pasos en el diseño de PCB de interfaz EtherCAT

La implementación exitosa de un diseño de PCB de interfaz EtherCAT requiere más que simplemente conectar pines en un esquema; exige un enfoque holístico de la integridad de la señal, la robustez mecánica y la validación de la cadena de suministro. Al definir especificaciones de impedancia estrictas, anticipando riesgos de escalado como la gestión térmica y la ESD, y validando rigurosamente las capacidades de su proveedor, asegura la fiabilidad de su producto de automatización industrial. Siga la lista de verificación proporcionada, valide temprano y elija un socio de fabricación que comprenda la precisión requerida para la comunicación industrial en tiempo real.