Conclusiónes Clave

- Definición: La cobertura ICT (Prueba en Circuito) de fábrica para PLC se refiere al porcentaje de redes y componentes en una placa de Controlador Lógico Programable que pueden ser verificados eléctricamente durante la fabricación.

- Importancia Crítica: A diferencia de la electrónica de consumo, los PLC requieren una fiabilidad cercana al 100%; los defectos no detectados pueden provocar fallos industriales catastróficos.

- Métricas: El estándar PCOLA/SOQ es el referente de la industria para medir la calidad de la cobertura, no solo simples puntos porcentuales.

- Diseño para Prueba (DFT): Lograr una alta cobertura comienza en la etapa del esquema, no en la planta de producción.

- Compensaciones: Una mayor cobertura a menudo requiere PCB más grandes o accesorios más caros; equilibrar esto es clave para una producción rentable.

- Validación: Los informes de simulación deben validarse frente a los resultados de pruebas físicas durante la Inspección del Primer Artículo (FAI).

- Colaboración: Trabajar con un fabricante capaz como APTPCB (Fábrica de PCB APTPCB) asegura que su estrategia DFT se alinee con las capacidades de producción reales.

En el contexto de los Controladores Lógicos Programables (PLC) (alcance y límites)

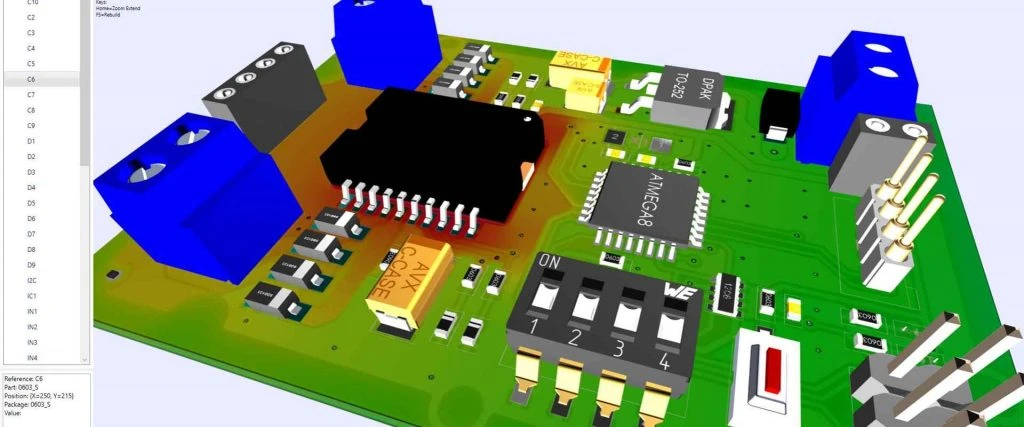

Comprender el alcance de las pruebas es el primer paso para garantizar la fiabilidad industrial en los sistemas de control. Cobertura ICT de fábrica para PLC es una medida cuantitativa de cuánto de la lógica y conectividad de una placa de circuito impreso puede validarse utilizando un probador de "lecho de agujas". En el contexto de los Controladores Lógicos Programables (PLC), esta métrica es mucho más crítica que en la electrónica general. Los PLC operan en entornos hostiles que implican vibraciones, temperaturas extremas e interferencias electromagnéticas. Una unión de soldadura que pasa una inspección visual pero falla una prueba de estrés eléctrico puede causar un cierre de fábrica meses después.

La prueba ICT (In-Circuit Test) se enfoca específicamente en:

- Cortocircuitos y Circuitos Abiertos: Asegurando que no existan puentes no deseados entre las redes y que las pistas sean continuas.

- Valores de Componentes: Verificando que la resistencia, capacitancia e inductancia coincidan con la Lista de Materiales (BOM).

- Presencia y Orientación de Componentes: Asegurando que los chips estén montados y girados correctamente.

- Función de Componentes Activos: Realizando verificaciones lógicas básicas en diodos, transistores y circuitos integrados (CI).

Es importante distinguir la cobertura ICT de la cobertura de la Prueba de Circuito Funcional (FCT). La ICT busca defectos de fabricación (puentes de soldadura, piezas incorrectas), mientras que la FCT verifica que la placa realice su lógica prevista. Para un PLC, una alta cobertura ICT es la base que hace que la FCT sea significativa. Si las conexiones físicas no se verifican primero, la depuración funcional se vuelve imposible. En APTPCB, enfatizamos que la cobertura no es solo un número porcentual. Es una herramienta de gestión de riesgos. Una placa con un 95% de cobertura aún podría pasar por alto el relé de seguridad crítico que protege todo el sistema. Por lo tanto, el alcance debe priorizar las "redes críticas" sobre las estadísticas de cobertura genéricas.

Métricas importantes (cómo evaluar la calidad)

Medir la cobertura requiere más que una simple relación de aprobado/fallido; exige un análisis granular de tipos de defectos específicos.

Para evaluar verdaderamente la cobertura ICT de fábrica para PLC, los ingenieros utilizan métricas específicas que categorizan lo que se está probando y qué tan bien. El estándar de la industria para esto es el modelo PCOLA/SOQ. Este modelo separa los atributos de los componentes (PCOLA) de los atributos de conexión (SOQ).

| Métrica | Por qué es importante | Rango típico o factores influyentes | Cómo medir |

|---|---|---|---|

| Relación de Acceso a Pruebas | Determina si las sondas pueden alcanzar físicamente las redes. | 90% - 100%. Menor en placas HDI. | (Redes con Puntos de Prueba / Redes Totales) × 100. |

| Cobertura de Componentes | Asegura que las piezas correctas estén instaladas. | 85% - 98%. Limitado por condensadores de derivación en paralelo. | Recuento de componentes con valores verificados / Recuento total de la lista de materiales (BOM). |

| Cobertura de Red | Verifica la continuidad y el aislamiento. | 95% - 100%. Crítico para planos de alimentación y tierra. | Recuento de redes completamente probadas / Recuento total de la lista de redes (Netlist). |

| Tasa de Falsos Fallos | Los altos falsos fallos ralentizan la producción y dañan las almohadillas. | < 500 PPM. Influenciado por la calidad del accesorio y la tensión. | (Falsas alarmas / Total de placas probadas) × 1,000,000. |

| Puntuación PCOLA | Comprueba Presencia, Corrección, Orientación, Actividad, Alineación. | Alta. Esencial para circuitos integrados y conectores complejos. | Análisis de software automatizado de la generación del programa de prueba. |

| Puntuación SOQ | Comprueba Cortocircuitos, Circuitos Abiertos, Calidad (integridad de la unión de soldadura). | Crítica. Debe estar cerca del 100% para la seguridad del PLC. | Medido mediante umbrales de resistencia durante la fase de prueba de cortocircuito/circuito abierto. |

| R&R del Calibrador | Asegura que el accesorio de prueba sea consistente y repetible. | < 10%. Si >30%, el sistema de prueba no es fiable. | Análisis estadístico de mediciones repetidas en la misma unidad. |

Guía de selección por escenario (compromisos)

Diferentes escenarios de fabricación dictan diferentes enfoques para lograr una cobertura de prueba óptima.

Lograr una cobertura ICT de fábrica del 100% para PLC es a menudo físicamente imposible o económicamente inviable. Debe seleccionar la estrategia correcta basándose en el ciclo de vida de su producto y las limitaciones técnicas. A continuación, se presentan escenarios comunes y el enfoque recomendado para cada uno.

1. Producción de alto volumen y baja mezcla

- Escenario: Producción en masa de módulos de E/S de PLC estándar.

- Recomendación: Invierta en un accesorio de vacío de alta gama con sondas de doble cara.

- Compromiso: Alto costo inicial de herramientas ($5k - $15k), pero el menor tiempo de prueba por unidad y la mayor repetibilidad.

- Perspectiva de APTPCB: Para volúmenes superiores a 5,000 unidades, el costo del accesorio se amortiza rápidamente, justificando el gasto para una cobertura máxima.

2. Prototipo e NPI (Introducción de Nuevos Productos)

- Escenario: Primera ejecución de una nueva placa de CPU de PLC.

- Recomendación: Utilizar pruebas de sonda volante (FPT) en lugar de un accesorio ICT fijo.

- Compromiso: Costo de herramientas cero, pero un tiempo de prueba por placa muy lento.

- Por qué: Los cambios de diseño son frecuentes. FPT permite actualizar los puntos de prueba en el software sin reconstruir un accesorio físico.

3. Diseños de interconexión de alta densidad (HDI)

- Escenario: PLCs compactos que utilizan micro-vías y BGAs de paso fino.

- Recomendación: Combinar ICT con Boundary Scan (JTAG) e Inspección Automatizada por Rayos X (AXI).

- Compromiso: Las sondas ICT no pueden alcanzar todas las redes en la tecnología PCB HDI. Debe confiar en JTAG para la lógica digital y en los rayos X para las uniones de soldadura BGA.

- Riesgo: Confiar únicamente en ICT aquí resultará en una baja cobertura (<60%).

4. PLCs de seguridad crítica (SIL 3 / SIL 4)

- Escenario: PLCs utilizados en sistemas de apagado de emergencia.

- Recomendación: Pruebas redundantes. Cobertura ICT del 100% en redes de seguridad, seguida de FCT del 100%.

- Compromiso: El costo más alto y el tiempo de ciclo más largo.

- Enfoque: Adherir a los estándares de seguridad para el diseño de PCB de PLC a menudo requiere ranuras de aislamiento físico, lo que puede complicar el sellado al vacío para los accesorios. Aquí se prefieren los accesorios mecánicos de presión.

5. Controladores Industriales de Alto Voltaje

- Escenario: PLCs que gestionan directamente entradas de 220V/480V.

- Recomendación: ICT selectivo. No sondear directamente las redes de alto voltaje si el probador no puede manejar la descarga potencial.

- Compensación: Menor cobertura en las entradas de energía para proteger el equipo de prueba.

- Mitigación: Utilice inspección visual (AOI) para la sección de alto voltaje e ICT para la lógica de bajo voltaje.

6. Placas Recubiertas (Recubrimiento Conformado)

- Escenario: PLCs destinados a entornos húmedos o corrosivos.

- Recomendación: Probar antes del recubrimiento. Si se requiere probar después del recubrimiento, use puntas de goma conductoras o enmascaramiento especializado.

- Compensación: El enmascaramiento añade mano de obra. Las sondas perforantes pueden dañar el recubrimiento, comprometiendo la protección contra la humedad.

Del diseño a la fabricación (puntos de control de implementación)

La implementación exitosa de ICT es un proceso lineal que comienza mucho antes de que se finalice el diseño de la PCB.

Para asegurar una alta cobertura de ICT en fábrica para PLC, los diseñadores deben seguir un estricto flujo de trabajo de Diseño para Prueba (DFT). La adaptación de puntos de prueba en un diseño terminado es una receta para problemas de integridad de la señal y baja cobertura.

- Fase Esquemática - Priorización de Redes: Identificar redes críticas (alimentación, reinicio, relojes, buses de comunicación). Marcarlas como "Debe Probarse" en el esquemático.

- Fase de Diseño (Layout) - Colocación de Puntos de Prueba: Colocar los puntos de prueba (TPs) en la cara inferior de la PCB siempre que sea posible. Los accesorios de una sola cara son significativamente más baratos y fiables que los de doble cara.

- Alineación a la Cuadrícula: Alinear los TPs a una cuadrícula de 2.54mm (100 mil) o 1.27mm (50 mil). Los puntos fuera de la cuadrícula requieren una perforación personalizada costosa para el accesorio.

- Geometría del TP: Utilizar un diámetro de pad mínimo de 0.8mm a 1.0mm para sondas estándar. Pads más pequeños (0.5mm) requieren sondas costosas y frágiles.

- Reglas de Espacio Libre: Mantener al menos 1.5mm de espacio libre entre los puntos de prueba y los cuerpos de los componentes para evitar que la cabeza de la sonda golpee el componente.

- Consideraciones de EMC: Al tratar con la zonificación EMC y la conexión a tierra para PLC, asegurarse de que los puntos de prueba en líneas de alta velocidad no actúen como antenas. Utilizar puntos de prueba "sin stub" o cubrirlos con blindaje de tierra si es necesario.

- Agujeros de Referencia (Tooling Holes): Incluir al menos dos agujeros de referencia no chapados (3mm+) en esquinas opuestas. Estos alinean la PCB con el accesorio. Sin ellos, el sondeo preciso es imposible.

- Generación de Gerber: Exportar un archivo específico de "Puntos de Prueba" o una netlist IPC-356. No confiar en que el fabricante adivine qué pads son para pruebas.

- Fabricación del Accesorio: Enviar los datos al fabricante del accesorio 2-3 semanas antes de la fabricación de la PCB.

- Depuración: La primera pasada suele producir fallos falsos. Ajuste las tolerancias del software (p. ej., la variación de la resistencia) en lugar de modificar físicamente la placa.

- Pruebas de galgas extensométricas: Antes de la producción en masa, mida la tensión mecánica que el accesorio aplica a la PCB. Una flexión excesiva puede agrietar los condensadores cerámicos.

- Documentación: Cree un "Informe de Cobertura" que detalle exactamente qué redes se prueban y cuáles se omiten. Esto es vital para la resolución de problemas futuros.

Para especificaciones detalladas sobre los requisitos de diseño, consulte nuestras directrices DFM.

Errores comunes (y el enfoque correcto)

Incluso los ingenieros experimentados caen en trampas que reducen la cobertura o aumentan los costos de fabricación.

Evitar estos escollos garantiza que su estrategia de cobertura ICT de fábrica para PLC sea eficaz y segura.

- Error: Colocar puntos de prueba debajo de componentes BGA o de perfil bajo.

- Corrección: Los puntos de prueba deben ser accesibles. Si una red solo es accesible debajo de un BGA, sáquela a una vía o a una almohadilla dedicada.

- Error: Confiar en "Via-in-Pad" para el sondeo.

- Corrección: El sondeo de vías chapadas puede causar "agrietamiento del barril" o un contacto poco fiable debido a los huecos de soldadura. Utilice siempre una almohadilla de prueba plana y sólida.

- Error: Ignorar componentes altos.

- Corrección: Los condensadores o transformadores altos en la parte inferior impiden que la placa se asiente plana en el accesorio. Mantenga la parte inferior relativamente plana o cree zonas de "exclusión" para las piezas altas.

- Error: Asumir que el 100% de cobertura es necesario.

- Corrección: Perseguir el último 5% de cobertura (generalmente condensadores de derivación o resistencias pull-up) puede duplicar el costo del accesorio. Acepte una cobertura menor en piezas pasivas no críticas si el control del proceso es bueno.

- Error: Olvidar la rutina de "descarga".

- Corrección: Los condensadores grandes en los PLC almacenan energía. El accesorio ICT debe tener un circuito de descarga para evitar que las sondas del probador se dañen al contacto.

- Error: Usar máscara de soldadura sobre los puntos de prueba.

- Corrección: Los puntos de prueba deben tener una abertura en la máscara. Las sondas no pueden penetrar la máscara de soldadura de forma fiable sin dañar la punta o la placa.

- Error: Descuidar la densidad de las sondas.

- Corrección: Demasiadas sondas en un área pequeña (alta densidad) crean una presión ascendente masiva, lo que podría deformar la placa. Distribuya los puntos de prueba de manera uniforme.

- Error: Pasar por alto los estándares de fabricación de PCB de control industrial.

- Corrección: Las placas industriales tienen cobre más grueso y diferentes perfiles térmicos. Asegúrese de que los parámetros de prueba tengan en cuenta la mayor capacidad de transporte de corriente de las pistas.

Preguntas Frecuentes

P: ¿Cuál es el costo típico de un accesorio ICT para PLC? A: Un accesorio estándar de "cama de agujas" generalmente cuesta entre $2,000 y $6,000, dependiendo del número de puntos de prueba y de si es de una o dos caras.

P: ¿Puede el ICT probar el software en el PLC? R: Generalmente, no. El ICT prueba el hardware (físico). Sin embargo, algunos sistemas ICT avanzados pueden realizar "Programación Flash" para cargar el cargador de arranque inicial, lo que sirve de puente para las pruebas de software.

P: ¿En qué se diferencia el ICT de las pruebas con sonda volante? R: El ICT utiliza un accesorio fijo para probar todos los puntos simultáneamente (rápido, alto costo de configuración). La sonda volante utiliza brazos robóticos móviles para probar los puntos secuencialmente (lento, costo de configuración cero). El ICT es para volumen; la sonda volante es para prototipos.

P: ¿Cuál es el espaciado mínimo entre puntos de prueba? R: Para sondas estándar (100 mil), mantenga 2.54mm de centro a centro. Para paso fino (50 mil), puede reducir a 1.27mm, pero el costo del accesorio aumenta y la durabilidad disminuye.

P: ¿Daña el ICT la PCB? R: Deja pequeñas "marcas de testigo" (hendiduras) en las almohadillas de prueba. Esto es normal y aceptable. Sin embargo, una presión excesiva puede agrietar las uniones de soldadura, por lo que se requiere una prueba de galgas extensométricas.

P: ¿Puedo usar vías como puntos de prueba? R: No se recomienda. Las vías a menudo están cubiertas con máscara de soldadura. Incluso si están abiertas, son irregulares. Es mejor añadir una almohadilla de prueba dedicada conectada a la vía.

P: ¿Cómo manejo los puntos de prueba para pares diferenciales de alta velocidad? R: Añadir un punto de prueba crea un "stub" que puede reflejar señales. Para buses de comunicación PLC de muy alta velocidad, utilice la simulación para asegurarse de que el punto de prueba no degrade la integridad de la señal, o pruebe estas líneas mediante escaneo de límites (boundary scan) en su lugar.

P: ¿Por qué mi informe de cobertura muestra un porcentaje bajo? R: Esto suele ocurrir si tiene muchos condensadores en paralelo (el probador los ve como un solo condensador grande) o si tiene muchas redes que son físicamente inaccesibles (por ejemplo, dentro de un BGA sin fan-out).

P: ¿Necesito ICT si tengo AOI (Inspección Óptica Automatizada)? R: Sí. La AOI solo verifica si la pieza tiene el aspecto correcto. No puede determinar si un resistor tiene el valor incorrecto, si un chip está defectuoso o si hay una soldadura fría debajo de un componente.

P: ¿Qué datos necesita APTPCB para cotizar ICT? R: Necesitamos los archivos Gerber, la BOM (Lista de Materiales), el archivo XY Pick and Place y la Netlist eléctrica (formato IPC-356).

Páginas y herramientas relacionadas

- Servicios de prueba ICT: Explore nuestras capacidades específicas en cuanto a hardware y software de prueba en circuito.

- PCB de Control Industrial: Conozca los requisitos específicos de material y fabricación para la electrónica industrial.

- Directrices DFM: Descargue nuestra lista de verificación para asegurarse de que su diseño esté listo para las pruebas de producción en masa.

Glosario (términos clave)

| Término | Definición |

|---|---|

| Lecho de agujas | Un accesorio ICT tradicional que contiene cientos de sondas con resorte que contactan la PCB simultáneamente. |

| DFT (Diseño para Prueba) | La práctica de ingeniería de diseñar un diseño de PCB específicamente para facilitar pruebas fáciles y completas. |

| DUT (Dispositivo Bajo Prueba) | El conjunto de PCB específico que se encuentra actualmente en el accesorio de prueba. |

| Accesorio | La interfaz mecánica (hardware personalizado) que sujeta la PCB y alinea las sondas con los puntos de prueba. |

| Netlist | Un archivo de texto que describe la conectividad eléctrica de la PCB, definiendo qué pines de componentes están conectados a qué redes. |

| Pogo Pin | Una sonda con resorte utilizada en accesorios de prueba para hacer contacto eléctrico con las almohadillas de la PCB. |

| IPC-356 | El formato de archivo estándar utilizado para comunicar las coordenadas de los puntos de prueba y la información de la red al fabricante. |

| Boundary Scan (JTAG) | Un método para probar interconexiones en circuitos integrados complejos (como FPGAs) sin sondas físicas, utilizando una interfaz serial. |

| Marca de testigo | La pequeña hendidura dejada en una almohadilla de soldadura por la sonda de prueba; prueba de que el punto fue probado. |

| Galga extensiométrica | Un sensor utilizado para medir la flexión o el estrés físico aplicado a la PCB durante la compresión al vacío del accesorio. |

| Falla falsa | Un resultado de prueba que indica un defecto cuando la placa está realmente bien, generalmente causado por un mal contacto de la sonda o tolerancias ajustadas. |

| Pista de guarda | Una técnica en TIC donde las redes circundantes se llevan a un voltaje específico para aislar el componente que se está midiendo. |

Conclusión (próximos pasos)

Lograr una alta cobertura de TIC en fábrica para PLC no es algo secundario; es una decisión estratégica que impacta la seguridad y fiabilidad de los sistemas industriales. Al comprender las métricas de PCOLA/SOQ, seleccionar la estrategia de fijación adecuada y adherirse a estrictas reglas de DFT, usted asegura que cada PLC que sale de la línea esté listo para la dura realidad del entorno de fábrica.

Para avanzar con su proyecto de PLC, APTPCB recomienda una revisión exhaustiva de DFM antes de finalizar su diseño. Al solicitar una cotización, por favor proporcione:

- Archivos Gerber (incluyendo una capa dedicada de Puntos de Prueba si está disponible).

- BOM (Lista de Materiales) con números de pieza del fabricante.

- Netlist (Lista de Redes) (formato IPC-356).

- Esquemáticos (PDF) para referencia de depuración.

- Requisitos de Prueba Específicos (por ejemplo, "Debe probar el 100% de los circuitos de relé de seguridad").

Las pruebas de alta calidad son la póliza de seguro para la reputación de su marca. Comience su viaje de validación con los datos correctos y el socio adecuado.