Definición, alcance y público de esta guía

El control de impedancia en PCB de etapas de potencia GaN se refiere a la gestión precisa de las dimensiones de las pistas, los stackups de capas y los materiales dieléctricos para mantener la integridad de señal y minimizar la inductancia parásita en circuitos de nitruro de galio (GaN). A diferencia de los diseños basados en silicio, los dispositivos GaN conmutan a velocidades extremadamente altas, con dv/dt y di/dt muy elevados. Sin un control estricto de la impedancia, esos flancos de conmutación rápidos provocan sobretensión, ringing e interferencia electromagnética (EMI), hasta el punto de destruir el dispositivo o hacer fallar los ensayos reglamentarios.

Esta guía está escrita para responsables de ingeniería y líderes de compras que están migrando desde diseños con MOSFET de silicio estándar hacia tecnología GaN. El enfoque está puesto en la realidad de fabricación de estas tarjetas. No hace falta ser físico para usarla; hace falta ser un decisor que quiera asegurar una cadena de suministro confiable.

El alcance cubre la intersección crítica entre el diseño de PCB de etapas de potencia GaN y su fabricación. Explicamos cómo especificar requisitos que una fábrica realmente pueda construir, cómo validar los resultados y cómo evitar errores frecuentes en compras. APTPCB (APTPCB PCB Factory) desarrolló esta guía para cerrar la brecha entre la simulación teórica y la producción física.

Cuándo conviene usar este enfoque y cuándo no

Entender el alcance real de los requisitos de GaN ayuda a decidir si su proyecto necesita de verdad el sobrecosto asociado al control avanzado de impedancia o si una fabricación estándar es suficiente.

Use control estricto de impedancia para PCB de etapas de potencia GaN cuando:

- la frecuencia de conmutación supera 500 kHz: a esas velocidades, la inductancia parásita en el lazo de compuerta se convierte en un punto crítico de fallo.

- el diseño tiene alta densidad de potencia: aplicaciones como fuentes de alimentación para servidores o cargadores embarcados de vehículos eléctricos requieren técnicas HDI (High Density Interconnect) con impedancia controlada.

- los tiempos de subida son rápidos (<10ns): si sus transistores GaN conmutan en nanosegundos, las pistas del PCB se comportan como líneas de transmisión y necesitan impedancia adaptada para evitar reflexiones.

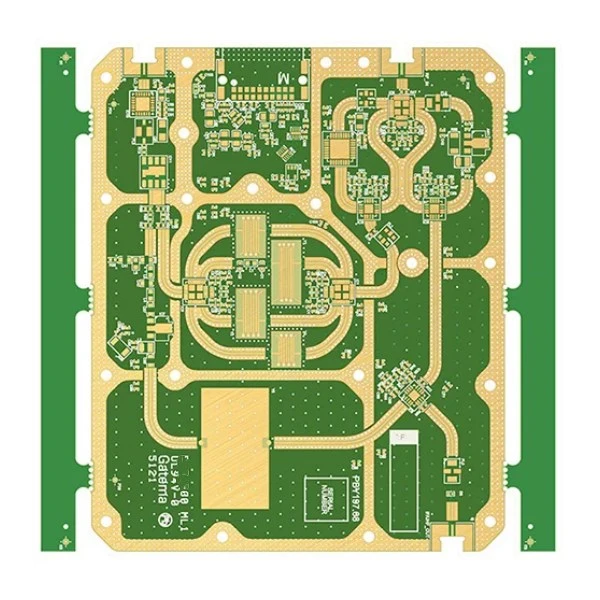

- se trata de amplificadores de potencia RF: GaN es estándar en RF y, en este caso, la adaptación de impedancia es imprescindible para transferir potencia con eficiencia.

Un enfoque estándar es mejor cuando:

- se trabaja con diseños heredados de silicio: si usa Si-MOSFET estándar que conmutan por debajo de 100 kHz, las tolerancias normales de +/- 10% suelen bastar.

- solo hay circuitos auxiliares de baja velocidad: la lógica de control o los rieles auxiliares de la misma placa pueden no requerir los mismos materiales costosos que la etapa principal de potencia.

- el prototipo busca solo ajuste y forma: si el objetivo es validar la mecánica, puede omitir pruebas de impedancia costosas para ahorrar tiempo.

Especificaciones que debe definir (materiales, stackup, tolerancias)

Una vez que determine que su proyecto necesita una fabricación de alto rendimiento, debe fijar especificaciones claras para alinear al equipo de diseño con el fabricante.

- Selección del material dieléctrico: especifique materiales con constante dieléctrica (Dk) estable y tangente de pérdidas (Df) baja a alta frecuencia. Las opciones habituales incluyen FR4 de Tg alta para frecuencias más bajas o laminados Rogers/Isola para aplicaciones GaN de clase RF.

- Simetría del stackup: defina un stackup equilibrado para evitar alabeo. En GaN, la distancia entre la capa superior, donde van los componentes, y el primer plano interno de referencia (GND) debe minimizarse para reducir la inductancia de lazo.

- Tolerancia de impedancia: pase del estándar de +/- 10% a +/- 5% o +/- 7% en pistas críticas del gate drive y del lazo de potencia.

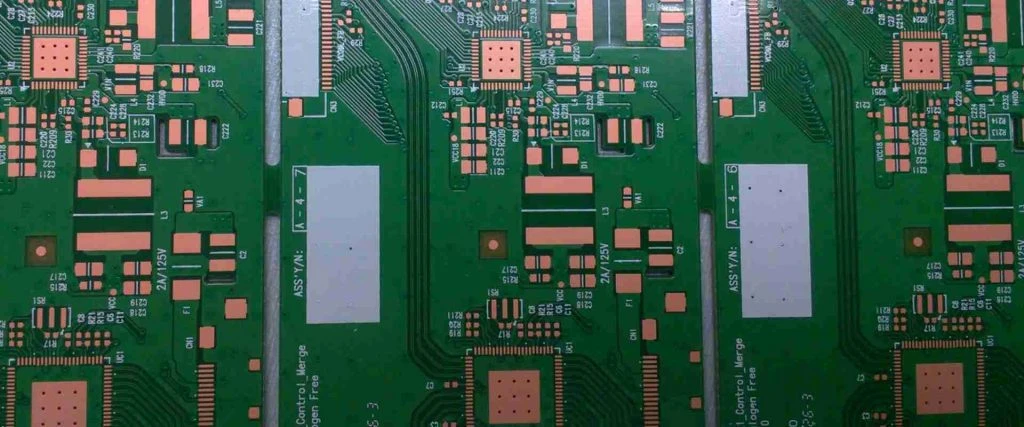

- Peso de cobre: especifíquelo con cuidado. El cobre pesado (2oz+) ayuda a la gestión térmica, pero dificulta el grabado de líneas finas necesario para controlar la impedancia.

- Ancho y separación de pista: defina los mínimos según el peso de cobre. Para cobre de 1oz, 4mil/4mil es estándar; para 2oz, 6mil/6mil es más seguro.

- Tipos de vía: especifique si se necesitan vías ciegas o enterradas. Los diseños GaN suelen usar vía-in-pad metalizada y tapada (POFV) para minimizar los caminos inductivos justo debajo del pad térmico del componente.

- Acabado superficial: ENIG (Electroless Nickel Immersion Gold) o ENEPIG es preferible a HASL. La superficie plana de ENIG es clave para colocar con precisión encapsulados GaN pequeños, como CSP o QFN.

- Máscara de soldadura: especifique máscara LPI (Liquid Photoimageable). El espesor de la máscara afecta la impedancia y el fabricante debe incluir ese efecto en sus cálculos.

- Resistencia al pelado: los dispositivos GaN trabajan en caliente. Asegúrese de que el laminado tenga alta resistencia de adhesión del cobre para evitar delaminación bajo ciclos térmicos.

- Estilo de tejido de vidrio: solicite "spread glass" o tejidos más cerrados, por ejemplo 1067 o 1080, para reducir el efecto del tejido de fibra que puede generar skew en pares diferenciales de alta velocidad.

- Requisitos de limpieza: la contaminación iónica debe controlarse estrictamente para impedir crecimiento dendrítico bajo campos de alto voltaje.

- Documentación: exija un informe de control de impedancia incluido con el embarque, validando las mediciones TDR frente a los archivos de diseño.

Riesgos de fabricación (causas raíz y prevención)

Incluso con especificaciones perfectas, el proceso físico de fabricación introduce variables que pueden alterar el control de impedancia en PCB de etapas de potencia GaN. Identificar esos riesgos pronto evita scrap.

Riesgo: variación del factor de grabado

- Causa raíz: a medida que el cobre aumenta de espesor, el agente químico de grabado elimina cobre de la parte superior de la pista más rápido que de la inferior, creando una forma trapezoidal.

- Detección: análisis microseccional.

- Prevención: APTPCB aplica factores de compensación de grabado a los datos Gerber antes de producción. Los diseñadores deben prever ligeros ajustes de ancho.

Riesgo: inconsistencia en el espesor dieléctrico

- Causa raíz: el flujo del prepreg durante el laminado puede variar, modificando la distancia entre la pista y el plano de referencia.

- Detección: las pruebas TDR muestran discontinuidades de impedancia.

- Prevención: use cobre de relleno o "dummy copper" en áreas vacías para igualar la presión durante el laminado y asegurar espesor uniforme.

Riesgo: errores de registro (desalineación de capas)

- Causa raíz: tolerancias mecánicas en taladrado y alineación de laminación.

- Detección: inspección por rayos X o cupones de verificación de taladro.

- Prevención: use Laser Direct Imaging (LDI) para obtener un registro más preciso e incluya fiduciales específicos para las capas críticas.

Riesgo: variación del espesor de la máscara de soldadura

- Causa raíz: una aplicación desigual de la máscara puede alterar la constante dieléctrica efectiva alrededor de la pista.

- Detección: inspección visual y TDR.

- Prevención: use procesos de recubrimiento por pulverización o cortina de alta calidad y tenga en cuenta el efecto de la máscara desde el cálculo inicial del stackup.

Riesgo: fiabilidad de las vías bajo esfuerzo térmico

- Causa raíz: los dispositivos GaN generan calor concentrado. La expansión del PCB en el eje Z puede agrietar el metalizado de las vías.

- Detección: ensayo de choque térmico.

- Prevención: use materiales de Tg alta (Tg > 170°C) y garantice espesor suficiente de metalizado en los barriles de las vías, con un promedio de 25µm.

Riesgo: falta de resina

- Causa raíz: los diseños con cobre pesado requieren más resina para rellenar los huecos entre pistas. Si el prepreg no tiene suficiente resina, aparecen vacíos.

- Detección: prueba de alta tensión o microsección.

- Prevención: seleccione prepregs con alto contenido de resina para capas adyacentes a cobre pesado.

Riesgo: oxidación del acabado superficial

- Causa raíz: almacenamiento o manipulación deficientes del acabado ENIG.

- Detección: prueba de soldabilidad.

- Prevención: empaque al vacío con desecante y tarjetas indicadoras de humedad, junto con control estricto de vida útil.

Riesgo: absorción de humedad

- Causa raíz: los materiales del PCB absorben humedad del ambiente, lo que incrementa Dk y puede provocar delaminación durante el reflow.

- Detección: prueba por peso u horneado.

- Prevención: hornee las placas antes del ensamblaje y guárdelas en bolsas de barrera de humedad (MBB).

Validación y aceptación (pruebas y criterios de aprobación)

Para garantizar que los riesgos de fabricación hayan sido mitigados, debe ejecutarse un plan de validación sólido antes de aceptar el lote de PCB de etapa de potencia GaN.

Objetivo: verificar la exactitud de la impedancia

- Método: reflectometría en el dominio del tiempo (TDR) en cupones de prueba o placas reales.

- Criterio de aceptación: la impedancia medida debe quedar dentro de la tolerancia especificada, por ejemplo 50 ohms +/- 5%.

Objetivo: verificar la construcción del stackup

- Método: microsección o análisis de corte transversal.

- Criterio de aceptación: los espesores dieléctricos y los pesos de cobre deben coincidir con el dibujo aprobado del stackup dentro de +/- 10%.

Objetivo: verificar el aislamiento

- Método: prueba Hi-Pot (High Potential).

- Criterio de aceptación: sin ruptura ni corriente de fuga por encima del límite, por ejemplo <1mA, al voltaje de prueba especificado.

Objetivo: verificar la soldabilidad

- Método: prueba de flotación de soldadura o balance de mojado.

- Criterio de aceptación: >95% de cobertura del pad con una capa de soldadura lisa y continua.

Objetivo: verificar la fiabilidad térmica

- Método: Interconnect Stress Test (IST) o choque térmico (-40°C a +125°C).

- Criterio de aceptación: el cambio de resistencia en las vías de cadena margarita debe ser <10% tras los ciclos especificados.

Objetivo: verificar la limpieza

- Método: prueba de contaminación iónica (ROSE test).

- Criterio de aceptación: los niveles de contaminación deben quedar por debajo de 1.56 µg/cm² equivalente de NaCl, o según la clase IPC-6012 aplicable.

Objetivo: verificar la precisión dimensional

- Método: CMM (Coordinate Measuring Machine) o inspección óptica.

- Criterio de aceptación: el contorno de la placa, la posición de agujeros y las dimensiones de slots deben cumplir las tolerancias del plano mecánico.

Objetivo: verificar la calidad del recubrimiento

- Método: fluorescencia de rayos X (XRF) para espesor del acabado superficial.

- Criterio de aceptación: espesor de oro ENIG 2-5µin; espesor de níquel 120-240µin.

Checklist de calificación de proveedores (RFQ, auditoría y trazabilidad)

Use esta checklist para evaluar posibles socios con capacidad de fabricación y ensamblaje de PCB de etapas de potencia GaN.

Grupo 1: entradas para RFQ (lo que usted envía)

- Archivos Gerber (RS-274X o X2) con nombres de capa claros.

- Plano de fabricación especificando clase IPC (Class 2 o 3).

- Diagrama de stackup con valores de impedancia objetivo y capas de referencia.

- Requisitos de fichas técnicas de material (Tg, Dk, Df, CTI).

- Tabla de taladrado distinguiendo orificios metalizados y no metalizados.

- Tabla de impedancia vinculando anchos de pista, capas y ohms objetivo.

- Requisitos de panelización, si aplican para ensamblaje.

- Notas especiales sobre vía-in-pad o vías rellenas.

Grupo 2: prueba de capacidad (lo que deben entregar)

- Lista de equipos que demuestre capacidad LDI (Laser Direct Imaging).

- Informes TDR de muestra de proyectos previos de alta velocidad.

- Certificado UL para el stackup de material solicitado.

- Informe DFM que demuestre la revisión de sus archivos específicos.

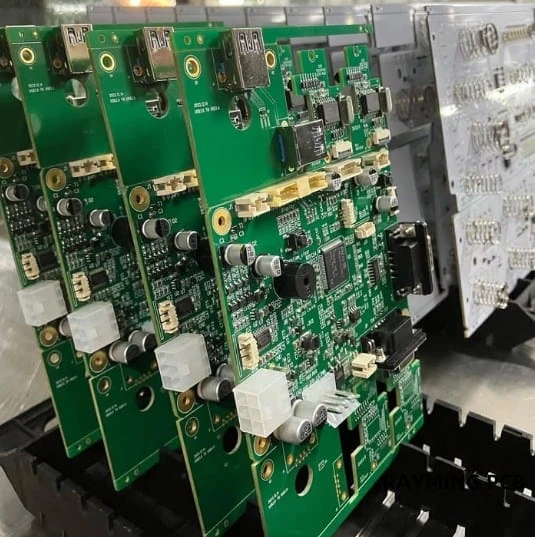

- Evidencia de manejo de cobre pesado y fine pitch en la misma placa.

- Certificación ISO 9001 e IATF 16949, si aplica a automoción.

Grupo 3: sistema de calidad y trazabilidad

- ¿Serializan placas individuales o solo paneles?

- ¿Pueden rastrear lotes de materias primas, desde laminado y foil hasta el PCB terminado?

- ¿Se realiza AOI (Automated Optical Inspection) en cada capa interna?

- ¿Hacen prueba eléctrica al 100% mediante Flying Probe o cama de clavos?

- ¿Existe sala limpia dedicada para exposición y laminación?

- ¿Cuál es su procedimiento para manejar material no conforme (MRB)?

Grupo 4: control de cambios y entrega

- ¿Tienen un proceso formal de PCN (Product Change Notification)?

- ¿Bloquearán el stackup y la marca de material después de aprobar el prototipo?

- ¿Cuál es el plazo estándar para este nivel tecnológico?

- ¿Ofrecen opciones quick-turn para NPI (New Product Introduction)?

- ¿El embalaje es seguro frente a ESD y controlado contra humedad?

- ¿Entregan un Certificate of Conformance (CoC) con cada envío?

Guía de decisión (equilibrios y reglas de elección)

Seleccionar el enfoque correcto para el control de impedancia en PCB de etapas de potencia GaN implica equilibrar rendimiento, costo y fabricabilidad.

- Si prioriza la máxima velocidad de conmutación (>1 MHz): elija materiales Rogers o de alta velocidad en lugar de FR4. La menor tangente de pérdidas justifica un costo de material 2-3 veces mayor para evitar degradación de señal.

- Si prioriza la gestión térmica: elija cobre pesado (3oz+) o PCB de núcleo metálico. Acepte, no obstante, que la tolerancia de impedancia quizá deba relajarse a +/- 10% debido a las dificultades de grabado con cobre grueso.

- Si prioriza la densidad en formato compacto: elija HDI con vía-in-pad. Esto minimiza de forma significativa la inductancia de lazo, pero aumenta el costo de la placa en 30-50% frente a la tecnología through-hole.

- Si prioriza el costo: elija FR4 estándar de Tg alta con stackup estándar. Es viable para aplicaciones GaN <500kHz, pero exige un layout cuidadoso para compensar las limitaciones del material.

- Si prioriza la fiabilidad en automoción o industria: elija fabricación IPC Class 3. Este nivel impone criterios más exigentes de espesor de recubrimiento e inspección, ayudando a que la placa sobreviva a ciclos térmicos severos.

- Si prioriza la integridad de señal por encima de la potencia: elija dieléctricos más finos. Capas delgadas, por ejemplo prepreg de 3-4 mil, aumentan el acoplamiento y reducen diafonía, aunque resultan más delicadas en fabricación.

FAQ (coste, plazo, archivos DFM y pruebas)

¿Cuál es el impacto en coste del control de impedancia para una PCB de etapa de potencia GaN? Agregar control estricto de impedancia suele incrementar el coste unitario del PCB entre 10-20%. Eso cubre cupones TDR, planificación especializada del stackup y rendimientos de fabricación más bajos por las tolerancias ajustadas.

¿Cómo se compara el plazo frente a una placa estándar? Espere 2-3 días adicionales sobre el plazo normal. El equipo de ingeniería necesita más tiempo para EQ (Engineering Questions) relacionadas con el stackup, y las pruebas TDR agregan una etapa al control de calidad final.

¿Qué archivos DFM concretos se necesitan? Además de los Gerber estándar, conviene entregar un archivo IPC-2581 u ODB++ si es posible, o un dibujo detallado del stackup. Marque explícitamente qué pistas son "impedance critical" para que el ingeniero CAM sepa qué líneas medir.

¿Puedo usar FR4 estándar para control de impedancia en una etapa de potencia GaN? Sí, para aplicaciones GaN de menor frecuencia, por debajo de 1 MHz. Sin embargo, debe usar FR4 "High-Tg" con Tg > 170°C para soportar el esfuerzo térmico. A frecuencias más altas, el FR4 estándar resulta demasiado disipativo.

¿Cuáles son los criterios de aceptación para pruebas TDR en placas GaN? El criterio estándar es +/- 10% respecto a la impedancia objetivo. Para GaN de alto rendimiento puede solicitar +/- 5%, pero eso puede limitar la cantidad de proveedores capaces y elevar el coste.

¿Cómo afecta el espesor de cobre al control de impedancia? El cobre más grueso (2oz+) dificulta el grabado preciso de líneas finas y aumenta la variación de impedancia. Si necesita tanto alta corriente como impedancia estricta, considere usar diferentes pesos de cobre en distintas capas.

¿Por qué se recomienda vía-in-pad en el diseño de PCB para etapa de potencia GaN? La vía-in-pad coloca la vía directamente bajo el pad de soldadura del componente. Eso crea el camino más corto posible hacia el plano de tierra y minimiza la inductancia parásita, principal enemiga del rendimiento GaN.

¿Necesito probar el 100% de las placas en impedancia? Normalmente no. La prueba TDR es destructiva si se realiza directamente sobre la placa, por lo que se hace sobre un cupón de prueba en el raíl del panel. Lo habitual es probar un cupón por panel o por lote para validar el proceso.

Páginas y herramientas relacionadas

- Fabricación de PCB de alta frecuencia – Revise opciones de materiales y capacidades específicas para aplicaciones de conmutación rápida como GaN.

- Herramienta de cálculo de impedancia – Use esta herramienta para estimar anchos de pista y separaciones antes de cerrar el layout.

- Capacidades de PCB HDI – Conozca la tecnología High Density Interconnect, a menudo necesaria para minimizar la inductancia de lazo en diseños GaN.

- Guías DFM – Revise las reglas de diseño para que su placa con impedancia controlada pueda fabricarse sin retrasos.

- Servicios de ensamblaje PCB – Entienda cómo manejamos el ensamblaje de componentes GaN de paso fino después de fabricar la placa.

Solicitar cotización (revisión DFM + precio)

¿Listo para pasar del diseño a producción? Envíe sus datos a APTPCB para una revisión DFM completa y una cotización. Revisamos su stackup contra nuestro stock de materiales y validamos sus cálculos de impedancia antes de que pague.

Para una cotización precisa, proporcione lo siguiente:

- Archivos Gerber: RS-274X u ODB++.

- Dibujo del stackup: incluyendo tipo de material e impedancia objetivo.

- Volumen: cantidad de prototipos frente a volumen de producción.

- Requisitos de prueba: indique si se requieren informes TDR o IPC Class 3.

Solicitar cotización y revisión DFM

Conclusión (siguientes pasos)

Implementar con éxito la tecnología de nitruro de galio requiere más que seleccionar el transistor correcto; exige un enfoque integral del control de impedancia en PCB de etapas de potencia GaN. Al definir especificaciones estrictas para materiales y stackup, comprender los riesgos de fabricación y aplicar un plan sólido de validación, usted se asegura de que la etapa de potencia funcione con eficiencia y fiabilidad. Use la checklist incluida para evaluar a sus proveedores y confirmar que pueden cumplir las exigencias severas de la conmutación GaN de alta velocidad.