Contenido

- El contexto: qué hace exigente la calidad de la interfaz de cumplimiento del código de red

- Tecnologías clave (Lo que realmente permite que funcione)

- Vista de ecosistema: placas / interfaces / pasos de fabricación relacionados

- Comparación: opciones habituales y lo que se gana / pierde

- Pilares de fiabilidad y rendimiento (Señal / Potencia / Térmico / Control de proceso)

- El futuro: hacia dónde avanza (Materiales, integración, IA/automatización)

- Solicitar cotización / revisión DFM para la calidad de la interfaz de cumplimiento del código de red (Qué enviar)

- Conclusión

Puntos clave

- La integridad de señal es crítica: la detección precisa de red (LVRT/HVRT) depende de un trazado PCB de bajo ruido y una colocación exacta de componentes.

- Aislamiento y seguridad: la distancia de fuga, el despeje y la selección de material (valores CTI) deben estar bien definidos para evitar fallos de arco catastróficos.

- Comportamiento térmico: las interfaces suelen quedar cerca de módulos de potencia calientes; la placa debe soportar ciclos térmicos sin delaminación.

- Consistencia de fabricación: la inspección automatizada (AOI/SPI) mantiene el mismo estándar de cumplimiento de red en cada unidad.

El contexto: qué hace exigente la calidad de la interfaz de cumplimiento del código de red

Diseñar y fabricar la interfaz para equipos conectados a red, ya sean turbinas eólicas, inversores solares o sistemas de almacenamiento en baterías (BESS), implica equilibrar sensibilidad de medida y robustez industrial. Estas placas deben detectar cambios mínimos de frecuencia o tensión para activar modos de cumplimiento como Low Voltage Ride Through (LVRT). Al mismo tiempo, operan a pocos centímetros de elementos de conmutación de alta potencia (IGBT o MOSFET SiC) que generan alta interferencia electromagnética (EMI).

En APTPCB (APTPCB PCB Factory), el reto principal es sostener control estricto de impedancia y limpieza durante fabricación. Una desviación pequeña en el espesor dieléctrico o un residuo mínimo de flux puede alterar la precisión de sensado o debilitar el aislamiento de alta tensión. Además, los códigos de red (por ejemplo IEEE 1547 o UL 1741) son muy estrictos. Si la placa deriva con el tiempo por calidad de material insuficiente, puede desconectarse una planta completa de forma inesperada y provocar penalizaciones económicas relevantes.

Tecnologías clave (Lo que realmente permite que funcione)

Conseguir alta calidad en una interfaz de cumplimiento de código de red requiere combinar técnicas avanzadas de fabricación PCB y procesos de ensamblaje precisos.

- Técnicas de aislamiento galvánico: la interfaz debe separar la lógica de control de baja tensión (DSP/FPGA) de la conexión de red de alta tensión. Normalmente se usan optoacopladores de cuerpo ancho o aisladores digitales. El trazado debe incluir ruteo preciso de ranuras de aislamiento para evitar trayectorias de fuga sobre la superficie de la placa.

- Diseño analógico de precisión: para medir con exactitud tensión y corriente de red, el PCB usa pares diferenciales y planos de masa analógicos dedicados. Esto reduce el área de lazo y la susceptibilidad al ruido inducido por conmutación de potencia cercana.

- Materiales con CTI alto: el material base (laminado) es clave. Usar FR4 con índice comparativo de trazado (CTI) alto mejora resistencia a ruptura eléctrica y seguimiento eléctrico incluso en ambientes húmedos o contaminados, habituales en despliegues exteriores.

- Cobre pesado y vías térmicas: aunque la interfaz en sí puede ser de baja potencia, suele rutear señales de accionamiento o convivir con rieles de potencia. Las pistas de PCB de cobre pesado y vías térmicas estratégicas ayudan a disipar calor para que el estrés térmico no deteriore la precisión de componentes pasivos sensibles.

Vista de ecosistema: placas / interfaces / pasos de fabricación relacionados

La interfaz de cumplimiento de red no trabaja aislada. Actúa como sistema nervioso entre el "músculo" (módulos de potencia) y el "cerebro" (controlador central).

- Etapa de potencia: la placa de interfaz recibe realimentación de la etapa de potencia. Si el diseño de la placa de potencia y energía es deficiente, acoplará ruido hacia la interfaz.

- Placa controladora de compuerta: con frecuencia, la interfaz de cumplimiento envía señales a una placa controladora independiente. Conectores y cableado entre ambas deben estar adaptados en impedancia para evitar reflexiones (oscilaciones) que provoquen disparos falsos.

- Ensamblaje y recubrimiento: una vez ensambladas, estas placas casi siempre requieren recubrimiento de protección. Este paso protege los circuitos de sensado frente a humedad y polvo en campo. Una interfaz bien diseñada define zonas de exclusión para que el recubrimiento no afecte conectores ni puntos de prueba.

Comparación: opciones habituales y lo que se gana / pierde

Al especificar estas interfaces, los equipos de ingeniería afrontan compromisos claros. ¿Basta un apilado estándar de 4 capas o conviene pasar a 6 capas para mejorar inmunidad al ruido? ¿Se mantiene FR4 estándar o se justifica pagar por dieléctricos de mayor desempeño?

La siguiente matriz resume el impacto práctico de cada decisión.

Matriz de decisión: elección técnica → resultado práctico

| Elección técnica | Impacto directo |

|---|---|

| Apilado de 4 capas vs. 6 capas | Con 6 capas se pueden separar planos de masa analógicos y digitales, mejorando de forma importante la relación señal-ruido (SNR) en el sensado de red. |

| FR4 estándar vs. FR4 con CTI alto | Un CTI alto (>600V) evita el seguimiento carbonizado en zonas de alta tensión, clave para cumplir normas UL/IEC en diseños compactos. |

| Acabado HASL vs. ENIG | ENIG ofrece superficie más plana para componentes de paso fino (como DSP) y mejor resistencia a corrosión que HASL para fiabilidad a largo plazo. |

| Ensamblaje Clase 2 vs. Clase 3 | Clase 3 eleva la fiabilidad con criterios más exigentes de llenado de soldadura y alineación de componentes, algo crítico en infraestructura esencial. |

Pilares de fiabilidad y rendimiento (Señal / Potencia / Térmico / Control de proceso)

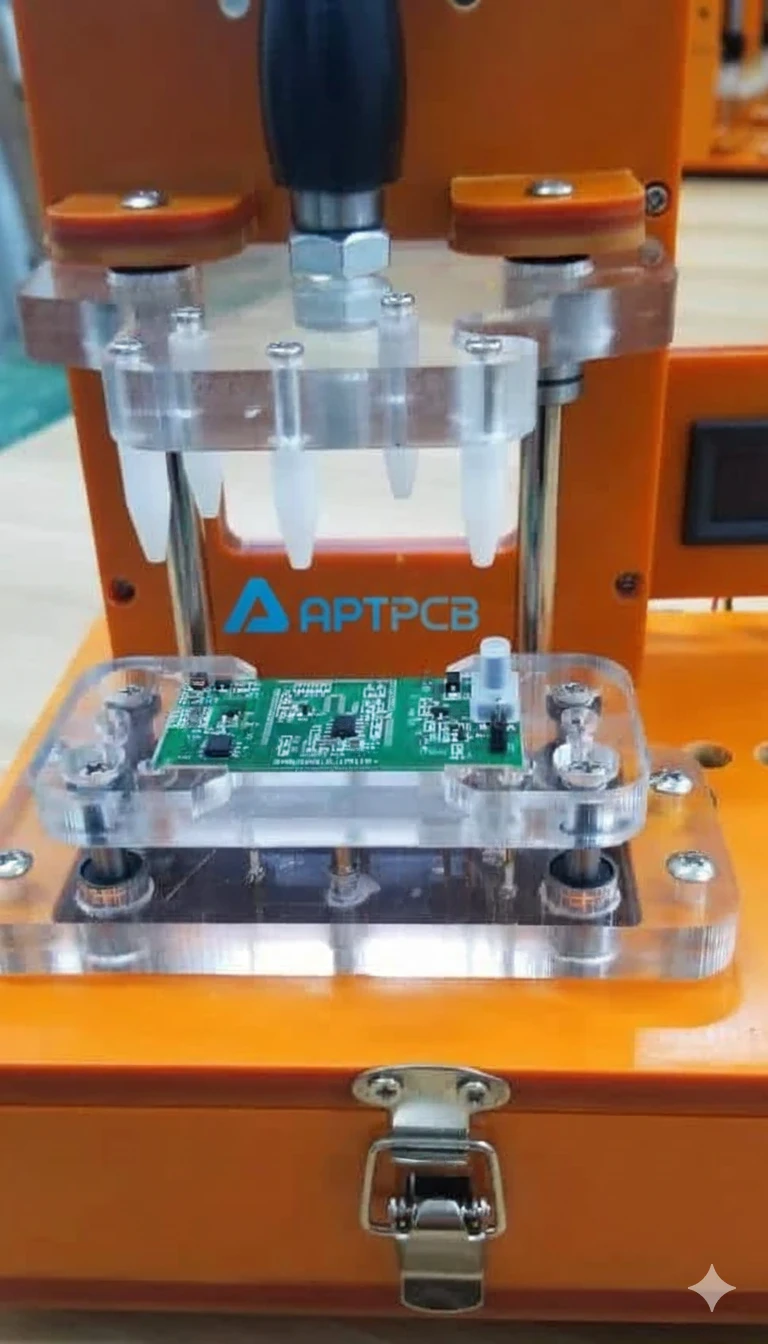

Para que una interfaz de cumplimiento de red alcance sus objetivos, APTPCB aplica una verificación rigurosa. No basta con montar componentes: hay que demostrar que la placa soporta los esfuerzos eléctricos y físicos propios del entorno de red.

Pilares de verificación clave

| Pilar | Qué verificar | Criterio de aceptación |

|---|---|---|

| Integridad de señal | Líneas analógicas de sensado (Tensión/Corriente) | Piso de ruido < 10mV; sin diafonía que afecte la precisión de medida. |

| Aislamiento | Barrera de alta tensión a baja tensión | Superar prueba Hi-Pot a 2.5kV (o norma específica) con fuga < 1mA. |

| Estrés térmico | Uniones de soldadura bajo ciclado | Sin grietas tras 1000 ciclos (-40°C a +125°C). |

| Limpieza | Contaminación iónica | < 1.56 µg/cm² equivalente NaCl para prevenir migración electroquímica. |

El control de proceso durante el ensamblaje de PCB es igual de relevante. La Inspección Óptica Automatizada (AOI) detecta componentes faltantes o desplazados, mientras que el In-Circuit Test (ICT) confirma que los pasivos (resistencias/capacitores) del circuito de sensado están dentro de tolerancia. Una resistencia nominal de 1% que en realidad se desvía 5% puede provocar un fallo de cumplimiento de red.

El futuro: hacia dónde avanza (Materiales, integración, IA/automatización)

A medida que la red se vuelve más inteligente y la electrónica de potencia migra hacia carburo de silicio (SiC) y nitruro de galio (GaN), las exigencias sobre la calidad de interfaz crecen. Velocidades de conmutación más altas implican más EMI y obligan a trazados más estrictos y materiales superiores.

Trayectoria de rendimiento a 5 años (ilustrativa)

| Métrica de rendimiento | Hoy (típico) | Dirección a 5 años | Por qué importa |

|---|---|---|---|

| Manejo de frecuencia de conmutación | 20kHz - 50kHz | 100kHz - 500kHz | Frecuencias mayores reducen tamaño de pasivos, pero elevan la susceptibilidad EMI y exigen apilados más avanzados. |

| Nivel de integración | Sensado y control discretos | Módulos inteligentes integrados | Integrar sensado, control y comunicaciones en una sola placa HDI reduce pasos de ensamblaje, pero aumenta complejidad. |

| Reporte de datos | Banderas básicas de estado | Analítica IA en tiempo real | Las interfaces procesarán datos localmente (Edge AI) para anticipar fallos de red antes de que ocurran. |

Solicitar cotización / revisión DFM para la calidad de la interfaz de cumplimiento del código de red (Qué enviar)

Cuando vayas a pasar tu diseño de interfaz de red de prototipo a producción, entregar un paquete de datos completo es esencial para una cotización precisa y un análisis DFM útil.

- Archivos Gerber: formato RS-274X con todas las capas de cobre, soldermask y serigrafía.

- Plano de fabricación: especifica clase IPC (2 o 3), requisitos de material (p. ej., Tg 170, CTI > 600) y notas de control de impedancia.

- Detalles de apilado: define orden de capas y espesores dieléctricos cuando la impedancia sea crítica.

- BOM (Bill of Materials): incluye números de parte del fabricante, especialmente para componentes críticos de aislamiento y resistencias de precisión.

- Notas de ensamblaje: indica requisitos especiales como soldadura selectiva para conectores de orificio pasante o especificaciones de recubrimiento conformal.

- Requisitos de prueba: define si la fábrica debe ejecutar ICT, FCT (Functional Circuit Test) o prueba Hi-Pot.

- Volumen y plazo: consumo anual estimado y fechas objetivo de entrega.

Conclusión

La calidad de la interfaz de cumplimiento del código de red no es solo una casilla de verificación; es la base de una red eléctrica estable y segura. Una interfaz bien diseñada permite que fuentes renovables y sistemas de almacenamiento interactúen de forma fluida con la infraestructura de red, soporten eventos de fallo y mantengan sincronización.

Al priorizar materiales robustos, trazado preciso y validación rigurosa, los fabricantes pueden evitar fallos costosos de certificación y retiradas en campo. Tanto para un inversor residencial pequeño como para una subestación de gran escala, colaborar con un fabricante experimentado como APTPCB ayuda a que tus placas de interfaz cumplan un estándar alto de fiabilidad y rendimiento.