Interpretar un informe TDR, es decir, de Time Domain Reflectometry, es el ultimo paso de verificacion entre una Printed Circuit Board ya fabricada y un sistema de alta velocidad que realmente funciona. Para compradores tecnicos e ingenieros de calidad, este informe actua como certificado de conformidad y confirma que el stackup fisico y los procesos de grabado cumplieron las exigencias de integridad de senal definidas durante el diseno.

Puntos clave

- Lo que debe especificarse por adelantado: datos, stackup, materiales y pruebas.

- Riesgos principales y senales tempranas de deteccion.

- Plan de validacion y criterios de aprobado o rechazo.

- Checklist de cualificacion de proveedores e informacion de RFQ.

Conclusiones clave

- Lo que debe especificarse por adelantado: datos, stackup, materiales y pruebas.

- Riesgos principales y senales tempranas de deteccion.

- Plan de validacion y criterios de aprobado o rechazo.

- Checklist de cualificacion de proveedores e informacion de RFQ.

- Tolerancia estandar: la mayoria de los PCB rigidos estandar apuntan a $\pm$10% de tolerancia de impedancia; un control mas estricto, como Clase 3 o alta velocidad, suele exigir $\pm$5%.

- Concepto de cupon: la prueba TDR es destructiva sobre las almohadillas de test, por lo que se mide un cupon en el borde del panel y no la placa funcional.

- Artefacto de lanzamiento: los primeros 200 a 500 ps de la grafica representan la conexion de la sonda al cupon y deben ignorarse al leer el valor de impedancia.

Highlights

- Tolerancia estandar: la mayoria de los PCB rigidos estandar trabajan con $\pm$10%; un control mas estricto para Clase 3 o alta velocidad suele requerir $\pm$5%.

- Concepto de cupon: la prueba TDR destruye la zona de contacto de prueba; por eso el fabricante mide un cupon y no la placa final.

- Artefacto de lanzamiento: los primeros 200 a 500 ps de la curva corresponden al acoplamiento de la sonda con el cupon y deben ignorarse.

- Zona de medida: la ventana valida es el plateau central relativamente plano y suele representar 3 a 6 pulgadas de longitud de traza.

- Factores ambientales: temperatura y humedad pueden desplazar la impedancia en 1 a 2 ohmios; la prueba debe hacerse en entorno controlado.

- Correlacion: un cupon conforme garantiza que el proceso fue correcto, pero errores de diseno en la placa real, como ausencia de planos de referencia, pueden hacer fallar el sistema.

- Consejo de validacion: verificar que el ancho de traza en el cupon fisico coincide con el informe de microseccion ayuda a confirmar que los datos TDR son autenticos.

Contenido

- Alcance, contexto de decision y criterios de exito

- Especificaciones a definir por adelantado

- Riesgos principales

- Validacion y aceptacion

- Checklist de cualificacion de proveedores

- Como elegir

- FAQ

- Glosario

Alcance, contexto de decision y criterios de exito

Cuando se compra un PCB con impedancia controlada, el informe TDR no es un simple tramite. Es la principal evidencia de que la placa funcionara a la frecuencia prevista. Esta guia cubre la interpretacion de estos informes para circuitos rigidos, flexibles y rigido-flexibles.

Criterios de exito

Para considerar satisfactoria una validacion TDR deben cumplirse los siguientes puntos:

- Conformidad de impedancia: todas las lineas probadas deben quedar dentro de la tolerancia especificada, por ejemplo 50 $\Omega$ $\pm$5 $\Omega$.

- Estabilidad de forma de onda: la traza TDR debe mostrar un plateau estable sin picos inductivos relevantes ni valles capacitivos superiores a 2 a 3 $\Omega$ dentro de la zona de prueba.

- Capacidad de proceso: para produccion en volumen, el Cpk de impedancia debe ser $\ge$ 1.33, señal de fabricacion estadisticamente estable.

Casos limite

- Trazas cortas: trazas por debajo de 1.5 pulgadas son dificiles de medir con precision usando sondas TDR estandar porque la reflexion de lanzamiento tapa la lectura.

- Materiales de mayores perdidas: en FR4 estandar, las trazas largas pueden mostrar una ligera pendiente ascendente de impedancia por resistencia continua y perdida dielectrica, lo que requiere un criterio de interpretacion especifico.

Especificaciones a definir por adelantado

Un informe TDR legible empieza con documentacion de fabricacion clara. Si los requisitos son ambiguos, el fabricante puede aplicar un enfoque de mejor esfuerzo que pase sus controles internos pero no garantice el rendimiento del sistema.

Notas criticas de fabricacion

Estas exigencias deberian figurar de forma explicita en la RFQ y en el plano de fabricacion:

- Modelos de impedancia: listar cada linea controlada con claridad, por ejemplo "capa 1, 50 ohmios single-ended, ancho 5 mil".

- Frecuencia de prueba y tiempo de subida: especificar el tiempo de subida del pulso TDR. Son comunes 200 ps o 500 ps. Para aplicaciones rapidas, de 25 Gbps o mas, conviene pedir tiempos como 35 ps.

- Diseno del cupon: exigir cupones dispuestos segun IPC-2221 y mantenidos unidos al panel hasta la inspeccion final.

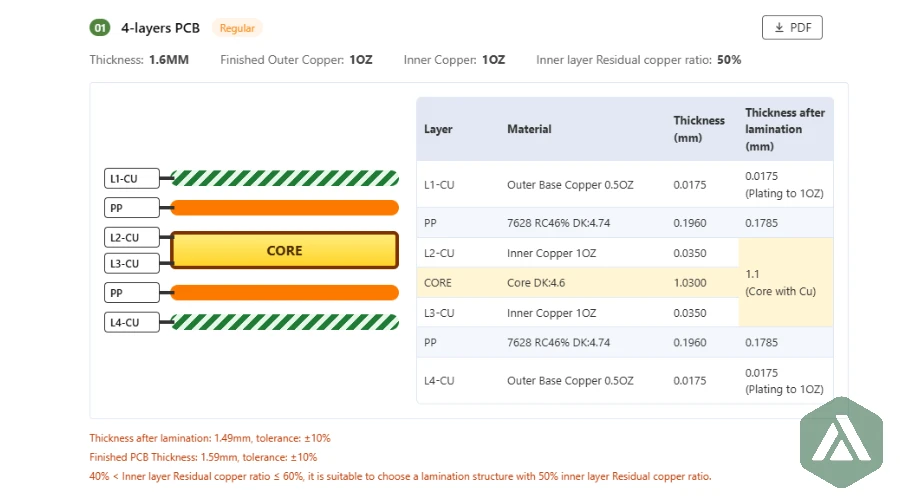

- Materiales dielectricos: definir la familia exacta, por ejemplo Isola PCB o Rogers, para fijar la constante dielectrica Dk.

- Planos de referencia: indicar de forma explicita que capas son referencia de tierra. La ambiguedad aqui es la causa numero uno de errores de stackup.

Tabla de parametros clave

| Parametro | Especificacion estandar | Especificacion de alto rendimiento | Por que importa |

|---|---|---|---|

| Tolerancia de impedancia | $\pm$10% | $\pm$5% | Determina el margen de reflexion de senal. |

| Tolerancia de ancho de traza | $\pm$20% | $\pm$10% o $\pm$0.5 mil | Las variaciones de grabado cambian directamente la impedancia. |

| Altura dielectrica | $\pm$10% | $\pm$5% | La distancia al plano de referencia es el factor mas fuerte sobre la impedancia. |

| Espesor de cobre | IPC Clase 2 | IPC Clase 3 | El espesor de metalizacion afecta la propagacion de la senal. |

| Cupon de prueba | Estandar del proveedor | IPC-2221 Tipo Z | Garantiza que el vehiculo de prueba replica la geometria del PCB. |

| Tiempo de subida TDR | < 200 ps | < 50 ps | Un tiempo de subida mas rapido revela discontinuidades mas pequenas. |

| Tolerancia de Dk | $\pm$5% | $\pm$2% | La consistencia del material asegura repetibilidad entre lotes. |

| Contenido de humedad | < 0.2% | < 0.1% | La absorcion de agua reduce la impedancia. |

Riesgos principales

Comprender como leer un informe TDR de cupon de impedancia exige reconocer la apariencia de un fallo. La mayoria de los problemas proviene de desviaciones fisicas en fabricacion.

1. Sobregrabado, impedancia alta

- Causa raiz: el grabado quimico retiro demasiado cobre y la traza quedo mas estrecha de lo previsto. Una reduccion de 0.5 mil puede elevar la impedancia 2 a 4 ohmios.

- Deteccion temprana: la grafica TDR aparece plana pero de forma constante por encima del objetivo, por ejemplo alrededor de 58 $\Omega$ para una meta de 50 $\Omega$.

- Prevencion: aplicar controles estrictos del proceso de fabricacion de PCB y usar compensacion de grabado en el fotoplot.

2. Variacion de espesor de prepreg, impedancia baja

- Causa raiz: durante el laminado sale mas resina de la prevista y se reduce la distancia entre la traza y el plano de referencia.

- Deteccion temprana: la curva TDR es estable pero siempre queda por debajo del objetivo.

- Prevencion: usar prepregs de bajo flujo o validar los parametros del stackup de PCB.

3. Discontinuidades de impedancia, la caida

- Causa raiz: aumento localizado de capacitancia, a menudo provocado por via stub, una pad de componente o un cambio de plano de referencia.

- Deteccion temprana: caida brusca en la forma de onda TDR.

- Prevencion: asegurar rutas de retorno continuas en el diseno y metalizacion uniforme en fabricacion.

4. Efecto del tejido de fibra

- Causa raiz: con tejidos abiertos de vidrio, una traza puede pasar sobre un haz de vidrio y luego sobre una zona rica en resina, variando el Dk local.

- Deteccion temprana: la linea TDR se ve ondulada o periodica en lugar de plana.

- Prevencion: usar spread glass FR4 o enrutado en zigzag para lineas criticas.

5. Desajuste entre cupon y placa

- Causa raiz: el cupon no replica la geometria real de la placa, por ejemplo por diferencias de despeje respecto a planos de tierra.

- Deteccion temprana: el cupon aprueba pero la placa real falla en la prueba funcional.

- Prevencion: realizar un analisis de microseccion en la placa real y compararlo con la geometria del cupon.

6. Absorcion de humedad

- Causa raiz: el PCB absorbio humedad antes de la prueba.

- Deteccion temprana: la impedancia aparece globalmente mas baja de lo esperado en todas las capas.

- Prevencion: hornear las placas antes de ensayar y almacenarlas en bolsas selladas al vacio.

7. Problemas de contacto de sonda

- Causa raiz: sondas sucias o mala presion de contacto sobre la pad de prueba.

- Deteccion temprana: la zona de lanzamiento es ruidosa o muestra un gran pico inductivo superior a 10 $\Omega$.

- Prevencion: limpiar las sondas con regularidad y usar equipos TDR automatizados.

8. Huecos de laminacion

- Causa raiz: aire atrapado entre capas que altera el Dk efectivo.

- Deteccion temprana: picos de impedancia abruptos e imprevisibles, a menudo acompanados de delaminacion.

- Prevencion: optimizar presion de vacio y tiempo de permanencia en el laminado.

Validacion y aceptacion

Cuando reciba el informe TDR, no se limite a buscar el sello "PASS". Debe analizar tambien la forma de onda.

Anatomia de una forma de onda TDR

- Region 1: lanzamiento, 0 a 0.5 ns: corresponde al cable y la sonda conectandose al cupon. Habra perturbacion. Debe ignorarse.

- Region 2: traza de prueba, 0.5 ns hasta el final: aqui esta el DUT, el dispositivo bajo prueba. Esta seccion deberia verse plana.

- Region 3: abierto, final: la linea se dispara hacia arriba en el extremo de la traza del cupon.

Checklist de criterios de aceptacion

| Elemento de prueba | Criterio de aceptacion | Plan de muestreo |

|---|---|---|

| Impedancia media | Debe quedar dentro de tolerancia, por ejemplo 50 $\Omega$ $\pm$10% | 100% de los cupones, normalmente 2 por panel |

| Variacion de impedancia | La linea no debe ondular mas de $\pm$2 $\Omega$ en la region de prueba | Todas las lineas probadas |

| Verificacion del ancho de traza | El ancho fisico debe cumplir el diseno a $\pm$20% o la tolerancia definida | 1 microseccion por lote |

| Alineacion entre capas | Registro intercapas < 5 mil de desviacion | 1 microseccion por lote |

| Verificacion de Dk | El Dk calculado desde TDR debe coincidir con la especificacion a $\pm$5% | Auditoria periodica |

| Longitud de prueba | La ventana valida debe cubrir al menos 60% de la longitud del cupon | Revision visual de la grafica |

Como validar los datos del informe

- Revise la escala: algunos fabricantes cambian la escala vertical para que una curva ondulada parezca plana. La escala tipica deberia ser de 2 a 5 ohmios por division, no 20.

- Revise fecha y hora: el informe debe haberse generado despues del proceso final de metalizado.

- Verifique el stackup: compare el apilado del informe con su diseno. Si el espesor dielectrico fue ajustado mas de 10% para alcanzar la impedancia, podria violar sus restricciones mecanicas.

Checklist de cualificacion de proveedores

Antes de adjudicar produccion de PCB con impedancia controlada, conviene comprobar las capacidades del proveedor.

- Equipamiento: usa el proveedor equipos TDR conocidos en la industria, como Polar CITS880s, Tektronix DSA8300 o Agilent?

- Software: utiliza un resolvedor de campo, como Polar SI8000 o SI9000, para calcular stackup, o solo formulas aproximadas?

- Generacion de cupon: el cupon se genera automaticamente desde los datos CAM o se dibuja a mano?

- Trazabilidad: puede vincular una grafica TDR concreta con un panel de fabricacion y una fecha concretos?

- Retencion de datos: archiva los datos TDR al menos durante 2 anos?

- Stock de materiales: tiene en inventario materiales rapidos como Megtron o Rogers, o piensa sustituirlos?

- Compensacion de grabado: existe un procedimiento documentado para calcular factores de grabado en funcion del peso de cobre?

- Entorno: estan controladas temperatura y humedad del laboratorio de ensayo?

- Calibracion: se calibra anualmente el equipo TDR con patrones trazables?

- Soporte DFM: ofrece revision DFM para sugerir ajustes de stackup antes de fabricar?

- Capacidad Clase 3: puede demostrar capacidad para tolerancia de $\pm$5% segun IPC Clase 3?

- Mantenimiento de sondas: existe un registro de sustitucion de puntas? Las sondas gastadas generan datos ruidosos.

Como elegir

Decidir el nivel de rigor del control de impedancia implica equilibrar coste y riesgo de integridad de senal.

- Si la interfaz es USB 2.0 estandar o GPIO lento por debajo de 100 MHz, elija fabricacion PCB estandar sin informe TDR especifico.

- Si la interfaz es DDR3, DDR4, PCIe Gen 3 o Ethernet de 1 Gbps o mas, elija tolerancia de $\pm$10% con prueba TDR al 100%.

- Si la interfaz es PCIe Gen 5, 56G PAM4 o RF por encima de 5 GHz, elija tolerancia de $\pm$5% y cobre de baja rugosidad.

- Si el presupuesto manda, elija probar solo las lineas single-ended y diferenciales mas criticas en vez de todas las lineas controladas.

- Si la placa es una Rigid-Flex PCB, elija un proveedor con experiencia real en control de impedancia sobre tierras malladas.

- Si usa HDI PCB con microvias, elija un proveedor capaz de incluir microvias en los cupones de prueba.

- Si el ancho de traza es inferior a 4 mil, elija un proveedor con capacidad de Laser Direct Imaging, LDI.

- Si el stackup es asimetrico, elija relajar la tolerancia de alabeo porque el control estricto de espesores dielectricos puede inducir deformacion.

- Si necesita Quick Turn PCB, elija materiales estandar como FR4 frente a materiales RF exoticos, siempre que el presupuesto de perdidas lo permita.

- Si el informe TDR muestra fallo, elija revisar primero la microseccion. Si la geometria es correcta pero la impedancia no, el Dk del material puede ser el culpable.

FAQ

P: Cuanto aumenta el coste del PCB por la prueba de impedancia? R: Normalmente, control de impedancia mas informe TDR agregan entre 5% y 15% al coste de la placa. Eso cubre ingenieria CAM adicional, el espacio ocupado por el cupon en el panel y la mano de obra de prueba.

P: Puede retrabajarse una placa con impedancia fuera de especificacion? R: No. Una vez grabadas las trazas y laminadas las capas, la geometria queda fijada. Si la impedancia esta fuera de rango, las placas deben desecharse y volver a fabricarse con compensacion de grabado o espesor dielectrico ajustado.

P: Por que la linea TDR sube al final de la traza? R: El final abierto de una traza tiene impedancia teoricamente infinita. Por eso la grafica TDR se eleva bruscamente al final del cupon. Eso confirma ademas que la senal recorrio toda la longitud.

P: Cual es la diferencia entre TDR single-ended y diferencial? R: El modo single-ended mide una linea respecto a tierra, normalmente 50 $\Omega$. El diferencial mide la interaccion entre dos lineas acopladas, tipicamente 90 $\Omega$ o 100 $\Omega$. Para ello se necesita un TDR con dos pulsos sincronizados.

P: Por que fallan mis trazas cortas en TDR? R: Las trazas menores de 1.5 a 2 pulgadas suelen quedar enterradas en la reflexion de lanzamiento. Es dificil obtener una lectura limpia. En esos casos se depende del control de proceso del fabricante sobre trazas mas largas de la misma capa.

P: La mascara antisoldante afecta la impedancia? R: Si. La mascara antisoldante suele reducir la impedancia entre 2 y 3 ohmios porque su Dk es mayor que el del aire. El calculo del fabricante debe considerar si la traza esta recubierta o expuesta.

P: Que significa "tolerancia de impedancia que las fabricas de PCB pueden sostener de forma realista"? R: Las fabricas estandar suelen sostener $\pm$10%. Las mas avanzadas, con LDI y laminacion automatizada, pueden mantener $\pm$5%. Cualquier valor mas estricto, por ejemplo $\pm$2%, suele implicar un proceso muy costoso o casi experimental.

P: Puedo usar un multimetro normal para medir impedancia? R: No. El multimetro mide resistencia en continua. La impedancia es una magnitud de corriente alterna dependiente de frecuencia. Para eso hace falta un TDR o un analizador vectorial de redes.

Solicitar cotizacion o revision DFM para lectura de informe TDR de cupon de impedancia

Glosario

| Termino | Definicion |

|---|---|

| TDR, Time Domain Reflectometry | Tecnica de medida que inyecta un pulso rapido en una linea y analiza reflexiones para calcular impedancia. |

| Cupon | Circuito de prueba situado en el rail del panel y concebido para representar las trazas reales del PCB. |

| Impedancia caracteristica, $Z_0$ | Cociente entre tension y corriente de una onda que se propaga por una linea de transmision. |

| Par diferencial | Dos senales complementarias usadas para transmitir datos con alta inmunidad al ruido. |

| Constante dielectrica, Dk o $\epsilon_r$ | Medida de la capacidad de un material para almacenar energia electrica; afecta velocidad de senal e impedancia. |

| Tangente de perdidas, Df | Medida de la potencia de senal perdida como calor dentro del dielectrico. |

| Tiempo de subida | Tiempo que tarda una senal en pasar del 10% al 90% de su valor final; cuanto mas corto, mayor exigencia de control de impedancia. |

| Microstrip | Traza en capa externa separada de un unico plano de referencia por dielectrico. |

| Stripline | Traza en capa interna atrapada entre dos planos de referencia. |

| Factor de grabado | Relacion entre profundidad de grabado y socavado lateral; clave para calcular el ancho final de traza. |

| Lanzamiento | Interfaz entre sonda TDR y cupon de prueba; crea un artefacto al inicio de la grafica. |

| DUT, Device Under Test | Elemento concreto que se esta midiendo. |

Conclusion

Dominar la lectura de datos de un informe TDR de cupon de impedancia le convierte en un socio activo de calidad y no en un comprador pasivo. Si define desde el principio tiempo de subida, diseno del cupon y clase de tolerancia, evitara fallos costosos de integridad de senal. La curva TDR es el pulso de su PCB de alta velocidad: una linea plana y estable dentro de la ventana de $\pm$10% o $\pm$5% es la mejor senal de un proceso sano. En su siguiente proyecto de alta velocidad, asegurese de que su socio de fabricacion de PCB tenga el equipo y la transparencia necesarios para ofrecer este nivel de validacion.