Invertir en Design for Manufacturability (DFM) y Design for Testability (DFT) es una decisión estratégica que traslada el control de calidad desde una lógica reactiva de corregir fallas hacia una lógica preventiva de evitarlas. Para compradores y product managers, entender cómo reducir defectos de PCBA con DFM y DFT es una de las formas más eficaces de bajar el costo total y acelerar la salida al mercado. Esta guía reúne las especificaciones técnicas y los marcos de decisión necesarios para alinear el diseño de ingeniería con la capacidad real de fabricación.

Aspectos destacados

- Prevención proactiva: DFM detecta antes de producir los problemas de layout que provocan puentes de soldadura, tombstoning y vacíos.

- Cobertura de prueba: DFT asegura que, si aparece un defecto, pueda detectarse por ICT o prueba funcional en lugar de escaparse al campo.

- Reducción de costos: Corregir un defecto en la etapa de diseño cuesta unas 10x menos que corregirlo en ensamblaje y unas 100x menos que resolverlo ya en campo.

- Alineación con el proveedor: Las especificaciones claras sobre el diseño del esténcil y los perfiles de reflow son críticas para componentes complejos como BGA y QFN.

Puntos clave

Antes de entrar en el detalle técnico, esta tabla resume cómo ambas metodologías impactan directamente en el costo y en la confiabilidad del producto.

| Feature | DFM (Design for Manufacturability) | DFT (Design for Testability) |

|---|---|---|

| Objetivo principal | Asegurar que el producto pueda fabricarse de manera consistente con alto rendimiento. | Asegurar que el producto pueda verificarse con rapidez y precisión. |

| Enfoque frente al defecto | Evita que los defectos ocurran, por ejemplo puentes de soldadura. | Detecta los defectos que sí ocurren, por ejemplo circuitos abiertos. |

| Entregable clave | Geometrías de pad optimizadas, alivios térmicos, espaciamiento entre componentes. | Puntos de prueba, acceso JTAG, scan chains. |

| Motor del ROI | Mayor First Pass Yield (FPY), menos retrabajo. | Menor tasa de falla en campo, diagnóstico más rápido. |

Cómo reducir defectos de PCBA con DFM y DFT: alcance, contexto de decisión y criterios de éxito

La reducción de defectos no empieza en la línea de ensamblaje, sino en la fase de esquema y layout. Cuando alguien pregunta cómo reducir defectos de PCBA con DFM y DFT, debe entender que está comprando capacidad de proceso, no solo una tarjeta estándar.

Contexto de decisión

Los compradores suelen enfrentarse al equilibrio entre dedicar más tiempo de ingeniería al principio y ganar velocidad en producción después. Saltarse las revisiones DFM para acelerar un prototipo suele terminar en placas difíciles de fabricar o en tasas elevadas de scrap durante la producción en volumen. El contexto depende de la complejidad del PCBA. Una placa sencilla con pasivos grandes puede requerir poco DFM, mientras que una placa HDI con BGA exige un análisis riguroso.

Criterios de éxito

Para comprobar si las acciones de DFM y DFT están funcionando, conviene seguir al menos estos indicadores:

- First Pass Yield (FPY): porcentaje de placas que pasan todas las pruebas sin retrabajo. Para productos maduros, una meta de 98%+ es habitual.

- Cobertura de prueba: porcentaje de nets y componentes accesibles mediante prueba automatizada. Un DFT sólido apunta a 90%+.

- Tasa de falso rechazo: frecuencia con la que placas buenas se marcan como defectuosas por límites de prueba mal definidos o fixtures inestables.

- Engineering Change Orders (ECOs): una reducción de ECOs relacionados con ensamblaje indica que el DFM está funcionando.

Especificaciones que conviene definir por adelantado

| Parameter | Recommended value / option | Why it matters | How to verify |

|---|---|---|---|

| Layer count | 4–8 (típico), más si hace falta | Afecta costo, rendimiento y margen de ruteo | Stackup + informe DFM |

| Min trace/space | 4/4 mil (típico) | Impacta rendimiento y plazo | DRC + capacidad de fabricación |

| Via strategy | Through vias vs VIPPO vs microvías | Afecta la confiabilidad del ensamblaje | Microsección + criterios IPC |

| Surface finish | ENIG/OSP/HASL | Afecta soldabilidad y planitud | COC + pruebas de soldabilidad |

| Solder mask | Verde mate (por defecto) | Mejora la legibilidad AOI y reduce riesgo de puentes | Prueba AOI + registro de máscara |

| Test | Flying probe / ICT / FCT | Equilibrio entre cobertura y costo | Informe de cobertura + plan de fixture |

| Acceptance class | IPC Class 2 / 3 | Define los límites de defecto aceptables | Notas del plano + reporte de inspección |

| Lead time | Standard vs expedited | Impacta el riesgo de cronograma | Cotización + confirmación de capacidad |

Para implementar DFM y DFT de forma efectiva, ciertos requisitos deben quedar explícitos dentro del paquete de datos. Cuando hay ambigüedad, la planta rellena huecos con supuestos, y ese es un origen frecuente de defectos.

1. Requisitos de datos para DFM

Entregue a su contract manufacturer (CM) algo más que archivos Gerber.

- Selección de clase IPC: indique de forma explícita si la placa debe fabricarse bajo IPC-A-610 Class 2 o Class 3. Esto define criterios de volumen de soldadura y alineación.

- Footprints de componentes: exija la verificación de footprints contra la Bill of Materials (BOM). Las discrepancias entre el componente real y el land pattern son una falla DFM muy común.

- Estrategia de panelización: defina el arreglo de panel. Una mala panelización puede generar fracturas por esfuerzo en condensadores cerámicos durante el depanelizado.

- Diques de solder mask: especifique un ancho mínimo de solder mask entre pads, típicamente 4 mil, para evitar puentes en IC de paso fino.

2. Requisitos de datos para DFT

El DFT suele dejarse para el final, y eso termina en fixtures bed of nails costosos que ni siquiera llegan a las nets críticas.

- Accesibilidad de los test points: exija que todas las nets críticas tengan un test point en la cara inferior del PCB. Así se habilita un In-Circuit Test (ICT) por una sola cara, mucho más económico.

- Clearance de test points: defina un despeje mínimo, por ejemplo 50 mil, entre test points y componentes altos para evitar daños a las puntas.

- JTAG/Boundary Scan: en placas digitales complejas, asegúrese de que la cadena JTAG esté ruteada y accesible. Eso permite probar conexiones entre chips sin usar puntas físicas.

- Netlist: entregue siempre una netlist IPC-356. Este archivo permite comparar la conectividad de Gerber con la conectividad del esquema.

Recursos relacionados

Riesgos clave: causa raíz, detección temprana y prevención

Entender los tipos de defecto más comunes ayuda a priorizar las revisiones DFM. Los problemas más difíciles suelen aparecer debajo de componentes con terminación inferior, como QFN (Quad Flat No-lead) y BGA.

1. Vacíos en componentes QFN y BGA

Los vacíos son bolsas de aire atrapadas dentro de la unión soldada. Un nivel excesivo de vacíos reduce la conductividad térmica y debilita la resistencia mecánica.

- Riesgo: sobrecalentamiento de QFN de potencia por mala transferencia térmica a través de una soldadura con vacíos.

- Prevención (DFM): aplique las qfn reflow best practices to reduce voids. Esto implica dividir en ventanas la apertura de pasta sobre el thermal pad. En lugar de imprimir un bloque grande de pasta que atrape gases, se imprime una rejilla de cuadrados pequeños con una cobertura aproximada del 50-70%, creando canales para que escapen los volátiles durante el reflow.

2. Defectos de soldadura BGA: puentes y opens

Los BGA son complejos porque sus uniones quedan ocultas.

- Riesgo: defectos Head-in-Pillow (HiP), donde la bola de soldadura reposa sobre la pasta pero no llega a coalescer correctamente.

- Prevención (DFM/proceso): se requiere un control estricto según bga voiding control: stencil, reflow, and x-ray criteria.

- Esténcil: utilice esténciles electropulidos con aperturas trapezoidales para mejorar la liberación de pasta.

- Reflow: optimice la zona de soak. Si el flux se quema demasiado pronto, la oxidación impide el mojado correcto.

- Criterios de rayos X: defina límites claros de aceptación. Para IPC Class 2, lo habitual es que los vacíos queden por debajo del 25% del área de la bola.

3. Tombstoning

Este defecto aparece cuando un componente pasivo pequeño se levanta por un extremo durante el reflow.

- Causa raíz: fuerzas de mojado desbalanceadas, a menudo porque un pad está conectado a un plano grande de tierra que actúa como disipador y el otro solo a una pista fina.

- Prevención (DFM): use thermal relief en pads de tierra para que ambos pads alcancen la temperatura de reflow al mismo tiempo.

4. Shadowing

En soldadura por ola o selectiva, los componentes grandes pueden bloquear la llegada de la ola a componentes pequeños ubicados detrás.

- Prevención (DFM): mantenga reglas de espaciamiento específicas en función de la dirección de avance dentro de la máquina de soldadura.

Validación y aceptación: pruebas y criterios de aprobación

| Test / Check | Method | Pass criteria (example) | Evidence |

|---|---|---|---|

| Continuidad eléctrica | Flying probe / fixture | 100% de nets probadas, sin opens ni shorts | Reporte de E-test |

| Dimensiones críticas | Medición | Cumple tolerancias del plano | Registro de inspección |

| Integridad de metalizado / relleno | Microsección | Sin vacíos ni grietas fuera de límites IPC | Fotos de microsección |

| Soldabilidad | Prueba de mojado | Mojado aceptable, sin dewetting | Reporte de soldabilidad |

| Warpage | Medición de planitud | Dentro de especificación, p. ej. ≤0.75% | Registro de warpage |

| Validación funcional | FCT | Todos los casos pasan, log almacenado | Logs de FCT |

¿Cómo se demuestra que DFM y DFT funcionaron? Es imprescindible definir un plan de validación alineado con sus objetivos de NPI assembly.

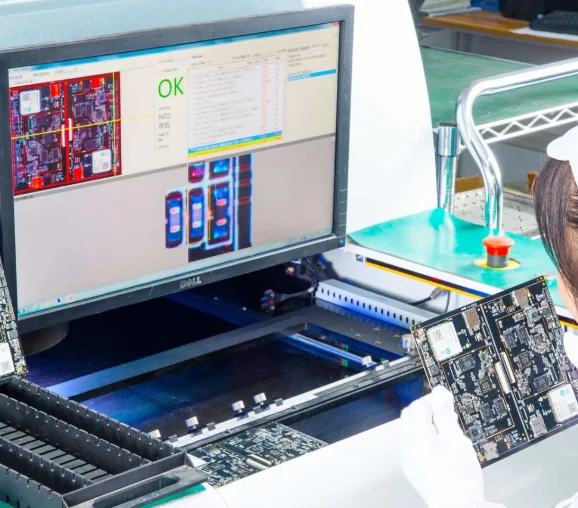

Automated Optical Inspection (AOI)

La AOI es la primera línea de defensa. Usa cámaras para verificar presencia de componentes, polaridad, skew y calidad de soldadura.

- Criterios de aprobación: sin piezas faltantes, marcas de polaridad alineadas y filetes de soldadura conformes con IPC.

- Limitación: no puede ver debajo de BGA o QFN.

X-Ray Inspection (Axi)

La inspección por rayos X es esencial para validar BGA y QFN.

- Criterios de aprobación: deben cumplirse las exigencias de bga voiding control: stencil, reflow, and x-ray criteria. Vacíos <25%, forma de bola consistente y ausencia de puentes.

- Aplicación: inspección al 100% en prototipos y por muestreo en producción masiva.

- Más información: Inspección por rayos X

In-Circuit Test (ICT) y Flying Probe

Aquí es donde el DFT demuestra su valor.

- ICT: usa un fixture bed of nails para probar todas las nets al mismo tiempo. Es rápido, pero implica un costo alto de fixture. Requiere test points definidos en el DFT.

- Flying Probe: utiliza brazos robóticos para sondear puntos sin fixture. Es más lento, pero ideal para prototipos.

- Criterios de aprobación: todos los valores pasivos dentro de tolerancia y ningún short u open en nets activas.

Functional Circuit Test (FCT)

Es la última etapa de validación. La placa se energiza y debe ejecutar su función real.

- Criterios de aprobación: el equipo arranca, el firmware carga y los puertos de I/O responden.

Checklist de calificación de proveedores: RFQ, auditoría y trazabilidad

Cuando evalúe un proveedor para ayudarle a reducir defectos de PCBA con DFM y DFT, utilice este checklist.

1. Capacidades de ingeniería

- ¿El proveedor realiza una revisión DFM obligatoria antes del tooling?

- ¿Entrega un informe DFM detallado y no solo un pass/fail, destacando riesgos como acid traps o slivers?

- ¿Puede proponer footprints alternativos para mejorar el rendimiento?

- Revise las Directrices DFM para el nivel esperado.

2. Control de proceso

- ¿Tiene SPI inline? La SPI evita una parte muy importante de los defectos de pasta y soldadura.

- ¿Dispone de rayos X dentro de la propia planta?

- ¿Puede aplicar las qfn reflow best practices to reduce voids, por ejemplo con vacuum reflow u optimización de perfil?

3. Trazabilidad y sistema de calidad

- ¿La planta está certificada bajo ISO 9001 o IATF 16949?

- ¿Ofrece trazabilidad a nivel de componente, vinculando lotes concretos con números de serie concretos?

- Revise su Sistema de calidad.

Cómo elegir el nivel adecuado de DFM y DFT: compensaciones y reglas de decisión

No todas las placas requieren la misma intensidad de DFM y DFT. Estas reglas ayudan a equilibrar costo y riesgo.

Escenario A: electrónica de consumo simple, bajo costo y alto volumen

- Estrategia: priorizar DFM para maximizar el rendimiento y minimizar el tiempo de ciclo.

- DFT: mínimo. Confiar en AOI y en muestreo funcional.

- Compensación: aceptar una tasa de falla en campo ligeramente mayor para mantener bajo el costo unitario.

Escenario B: médico o automotriz, alta confiabilidad y volumen medio

- Estrategia: DFM y DFT agresivos.

- DFT: 100% ICT y 100% prueba funcional.

- Compensación: costos NRE más altos en fixtures y programación de prueba, pero una tasa de falla en campo cercana a cero.

- Punto específico: cumplimiento estricto de bga voiding control: stencil, reflow, and x-ray criteria.

Escenario C: prototipado rápido

- Estrategia: DFM "ligero". Corregir solo los showstoppers que impiden ensamblar.

- DFT: flying probe sin costo de fixture.

- Compensación: mayor tiempo de prueba por unidad, pero entrega más rápida.

FAQ: costo, lead time, archivos DFM, materiales y pruebas

1. ¿Agregar requisitos de DFM/DFT aumenta el precio cotizado? Sí, al inicio. El tiempo de ingeniería y los fixtures de prueba como NRE elevan el costo inicial. Sin embargo, muchas veces el costo total del proyecto baja al mejorar el rendimiento y reducir el retrabajo.

2. ¿Cuánto agrega una revisión DFM al lead time? Normalmente 1-2 días. Una revisión DFM seria se realiza antes de pedir materiales. Ese pequeño retraso evita semanas perdidas por descubrir más tarde que la placa no era fabricable.

3. ¿Puede DFM corregir un mal diseño de circuito? No. DFM garantiza que la placa pueda fabricarse, no que el circuito vaya a funcionar. Si el esquema tiene errores lógicos, la placa se fabricará bien pero fallará funcionalmente.

4. ¿Cuál es la diferencia entre DFM y DFA? DFM suele referirse a la fabricabilidad del PCB, como grabado o perforado. DFA se refiere al ensamblaje de componentes, como soldadura y clearances. En la práctica, mucha gente usa DFM como término amplio para ambos.

5. ¿Necesito ICT si ya tengo prueba funcional? Idealmente sí. ICT le dice qué componente o qué net falló. La prueba funcional normalmente solo confirma que la placa no funciona. Para diagnóstico y reparación, ICT es mucho más eficiente.

6. ¿Cómo afectan los materiales al DFM? La selección del material, por ejemplo High Tg FR4, determina cómo se expande la placa durante el reflow. Un desajuste de CTE entre componente y placa es una causa importante de fatiga en la soldadura.

7. ¿Cuál es la mejor manera de comunicar notas DFM? Incluya un archivo Read Me o un PDF dentro del zip de Gerber. Enumere de forma explícita requisitos especiales como "Do not X-out arrays" o "Mask plug vias at U1".

Solicitar cotización o revisión DFM: qué debe enviar

¿Quiere optimizar su PCBA para producción en masa? Envíe su paquete de datos para una revisión DFM completa.

Checklist para solicitar cotización:

- Archivos Gerber (RS-274X): capas de cobre, máscara de soldadura, serigrafía, perforado y capas de pasta.

- Bill of Materials (BOM): archivo Excel con Manufacturer Part Numbers (MPN) y designadores de referencia.

- Archivo centroid (Pick and Place): coordenadas X-Y y datos de rotación.

- Assembly drawings: PDF con ubicación de componentes y marcas de polaridad.

- Requisitos de prueba: descripción de la cobertura deseada, por ejemplo ICT, FCT o burn-in.

Glosario: términos clave

| Term | Meaning | Why it matters in practice |

|---|---|---|

| DFM | Design for Manufacturability: reglas de layout para reducir defectos. | Evita retrabajos, retrasos y costos ocultos. |

| AOI | Automated Optical Inspection para detectar defectos de soldadura y ensamblaje. | Mejora la cobertura y detecta desvíos tempranos. |

| ICT | In-Circuit Test para verificar opens, shorts y valores eléctricos. | Prueba estructural rápida para producción en volumen. |

| FCT | Functional Circuit Test con la placa energizada y en operación. | Valida la función real bajo carga. |

| Flying Probe | Prueba eléctrica sin fixture mediante puntas móviles. | Adecuada para prototipos y volúmenes bajos o medios. |

| Netlist | Definición de conectividad para comparar diseño y PCB fabricado. | Detecta opens y shorts antes del ensamblaje. |

| Stackup | Construcción de capas con núcleos, prepregs, cobre y espesor. | Afecta impedancia, warpage y confiabilidad. |

| Impedance | Comportamiento controlado de trazas para señales RF o de alta velocidad, p. ej. 50Ω. | Evita reflexiones y fallas de integridad de señal. |

| ENIG | Acabado superficial de níquel químico con oro por inmersión. | Equilibra soldabilidad y planitud; hay que controlar el espesor de níquel. |

| OSP | Organic Solderability Preservative como acabado superficial. | Bajo costo, pero más sensible a manipulación y múltiples reflujos. |

Conclusión: próximos pasos

Aprender cómo reducir defectos de PCBA con DFM y DFT es una inversión en la vida útil del producto y en la reputación de la marca. Cuando define con claridad las especificaciones de esténcil, perfiles de reflow y accesibilidad de prueba, transforma un proceso opaco en un proceso controlable y predecible.

Involucre al socio de fabricación desde la fase temprana de diseño. Una revisión conjunta de qfn reflow best practices to reduce voids y bga voiding control: stencil, reflow, and x-ray criteria ahorra tiempo y capital. Priorice la transparencia del paquete de datos, valide con rigor y elija un proveedor que trate la calidad como una responsabilidad compartida.