Puntos clave

- Alcance de la definicion: el layout de un PCB de control para inversor trifasico consiste en la disposicion fisica de gate drivers, microcontroladores y circuitos de sensado manteniendo una separacion estricta respecto a la etapa de potencia de alta tension.

- Metrica critica: la inductancia de lazo en la ruta de accionamiento de gate es el factor individual mas importante que afecta a la eficiencia de conmutacion y a la interferencia electromagnetica (EMI).

- El aislamiento es esencial: las distancias correctas de creepage y clearance entre el lado de alta tension (DC link/IGBTs) y el lado de baja tension (MCU/DSP) son innegociables para la seguridad.

- Gestion termica: incluso las placas de control necesitan estrategias termicas, especialmente en gate driver ICs que manejan cargas capacitivas grandes.

- Validacion: la simulacion no basta; hacen falta pruebas de doble pulso y termografia para validar el layout sobre hardware real.

- Preparacion para fabricacion: el DFM debe contemplar requisitos de cobre pesado y simetria del stackup para evitar alabeos.

Que significa realmente “PCB de control para inversor trifasico” (alcance y limites)

El termino layout PCB de control para inversor trifasico se refiere a la disciplina de ingenieria encargada de diseñar la placa de circuito impreso que gobierna la conmutacion de un inversor de potencia trifasico. Mientras la etapa de potencia maneja la corriente principal, a menudo de cientos de amperios, el layout de control actua como cerebro y sistema nervioso del conjunto. Convierte la logica digital, es decir, las señales PWM, en tensiones fisicas de accionamiento de gate al tiempo que lee la realimentacion analogica de corriente, tension y temperatura.

Esta tarea de layout es singular porque se situa en el punto de encuentro entre señales digitales delicadas y eventos de conmutacion de alta tension muy agresivos. Un mal layout no solo produce una placa que funciona mal, sino que con frecuencia acaba en el fallo catastrofico de los modulos de potencia por disparos falsos o sobretensiones.

En APTPCB (APTPCB PCB Factory) vemos a menudo diseños que funcionan perfectamente en simulacion pero que fallan en condiciones reales debido a inductancias parasitas ocultas en el layout del PCB. El alcance de esta guia cubre el recorrido desde la salida del microcontrolador (MCU), pasando por la barrera de aislamiento, hasta el gate driver y, finalmente, hasta la interfaz con los interruptores de potencia, ya sean IGBT, MOSFET o dispositivos SiC/GaN.

Metricas que importan (como evaluar la calidad)

Para determinar si un layout PCB de control para inversor trifasico es robusto, hay que medir parametros fisicos y electricos concretos. Estas metricas marcan la diferencia entre un prototipo y una placa realmente lista para produccion.

| Metrica | Por que importa | Rango tipico o factores de influencia | Como medir |

|---|---|---|---|

| Inductancia del gate loop | Una inductancia alta provoca ringing, sobretension y conmutacion mas lenta. | Objetivo: < 10 nH. Influida por la longitud de pista y la proximidad del retorno. | Simulacion con Q3D Extractor u observacion del overshoot en V_ds. |

| Inmunidad a transitorios en modo comun (CMTI) | Determina si el aislador soporta cambios rapidos de tension (dV/dt) sin corromper datos. | > 50 kV/µs para Si; > 100 kV/µs para SiC/GaN. | Pruebas con generador de pulsos a traves de la barrera de aislamiento. |

| Distancia de creepage | Evita el seguimiento electrico sobre la superficie del PCB con humedad y contaminacion. | Depende de la tension; por ejemplo, 8 mm para sistemas de 400 V en grado de contaminacion 2. | Medicion fisica con calibre o comprobacion de reglas CAD. |

| Distancia de clearance | Evita ruptura en aire entre redes de alta y baja tension. | Definida por IPC-2221 o IEC 60664-1. | Design Rule Check (DRC) en CAD. |

| Resistencia termica (Rth) | Garantiza que gate drivers y reguladores no se sobrecalienten durante la conmutacion a alta frecuencia. | Depende del espesor de cobre y de los vias termicos. | Camara termica bajo carga. |

| Relacion señal-ruido (SNR) | Critica para la realimentacion de sensado de corriente hacia las lineas ADC. El ruido genera rizado de par en motores. | Objetivo: > 60 dB. Influida por la separacion de planos de masa. | Analisis con osciloscopio de las lineas analogicas de feedback. |

Decisiones de diseño segun el escenario (compromisos)

Las distintas aplicaciones exigen enfoques muy diferentes en el diseño de un PCB de control para inversor trifasico. A continuacion se muestran los escenarios mas comunes y sus compromisos.

1. Accionamientos de motor de baja tension (12V - 48V)

- Contexto: herramientas con bateria, e-bikes, robotica.

- Compromiso: el espacio es la restriccion principal.

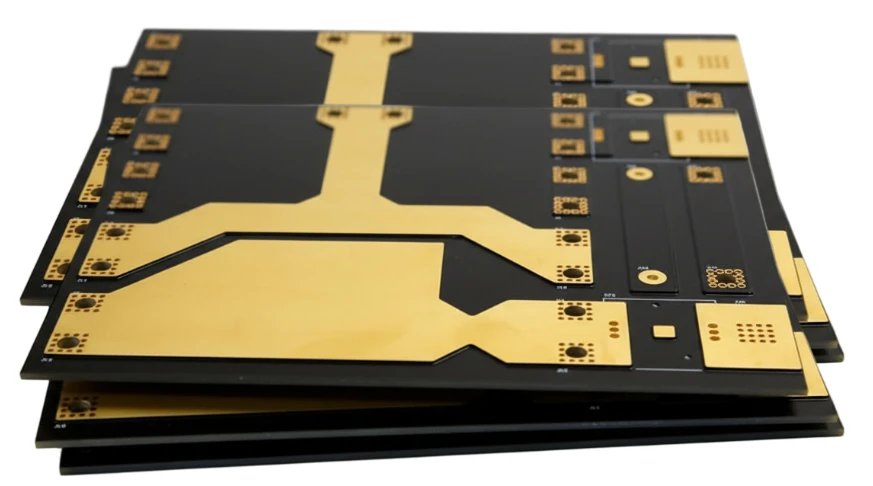

- Guia: en muchos casos potencia y control pueden integrarse en un solo PCB. Utilice tecnologia Heavy Copper PCB para conducir la corriente en una huella reducida. Los requisitos de aislamiento son menos estrictos y permiten una colocacion de componentes mas compacta.

2. Variadores AC industriales (400V - 690V)

- Contexto: automatizacion industrial, bombas, ventiladores.

- Compromiso: la fiabilidad y la seguridad estan por encima del tamaño.

- Guia: seguir de forma estricta IEC 61800-5-1. Usar una placa de control dedicada separada de la etapa de potencia y conectada mediante headers o pines press-fit. Dar prioridad a ranuras amplias de creepage.

3. Inversores de traccion para EV (alta densidad de potencia)

- Contexto: traccion principal de vehiculos electricos.

- Compromiso: vibracion elevada y ciclado termico extremo.

- Guia: usar materiales de grado automocion. El layout debe soportar dV/dt alto, especialmente con SiC. A menudo se requieren sustratos High Thermal PCB o diseños con nucleo metalico para la etapa driver, de modo que el calor se conduzca al sistema de refrigeracion.

4. Inversores solares (conectados a red)

- Contexto: conversion de energia fotovoltaica.

- Compromiso: eficiencia y larga vida util, del orden de 20 anos o mas.

- Guia: reducir las perdidas en el gate drive para mejorar la eficiencia global. El layout debe contemplar tensiones elevadas de bus DC, de hasta 1500 V, lo que exige barreras de aislamiento importantes y en algunos casos recubrimiento conformal.

5. Drivers GaN/SiC de alta frecuencia

- Contexto: fuentes para servidores, cargadores compactos.

- Compromiso: velocidades de conmutacion extremas frente a EMI.

- Guia: la inductancia del lazo debe acercarse a cero. El driver tiene que colocarse fisicamente lo mas cerca posible del interruptor. A menudo hacen falta tecnicas HDI para situar los drivers justo debajo o encima de los dispositivos de conmutacion.

6. Electrodomesticos sensibles al coste

- Contexto: lavadoras, equipos HVAC.

- Compromiso: coste frente a rendimiento.

- Guia: las placas de una o dos capas siguen siendo comunes para reducir coste. Eso complica mucho el ruteo de los caminos de retorno. Los diseñadores deben aplicar con gran disciplina tecnicas de masa estrella para evitar acoplo de ruido sin contar con planos de masa completos.

Puntos de control de implementacion (del diseño a fabricacion)

Pasar del esquematico a la placa fisica exige un proceso disciplinado. Use esta checklist para comprobar que su PCB de control para inversor trifasico esta listo para produccion en APTPCB.

Definicion del stackup:

- Recomendacion: usar al menos 4 capas para inversores industriales (Señal-Masa-Potencia-Señal).

- Riesgo: las placas de 2 capas suelen fallar en EMI por tener caminos de retorno rotos.

- Aceptacion: verificar perfiles de impedancia y simetria de capas.

Colocacion de gate drivers:

- Recomendacion: colocar los drivers a menos de 10 mm de los pines del modulo de potencia o de las gates de los MOSFET.

- Riesgo: las pistas largas actuan como antenas y añaden inductancia.

- Aceptacion: inspeccion visual de la distancia.

Conexion Kelvin para sensado de corriente:

- Recomendacion: rutear muy juntas las parejas diferenciales de las resistencias de sensado.

- Riesgo: captar ruido de conmutacion en el lazo de realimentacion causa inestabilidad de control.

- Aceptacion: verificar el ruteo diferencial en CAD.

Anchura de la barrera de aislamiento:

- Recomendacion: fresar una ranura fisica bajo optoacopladores o aisladores digitales si la tension supera 400 V.

- Riesgo: carbonizacion del PCB con el tiempo y posterior cortocircuito.

- Aceptacion: revisar los archivos Gerber para confirmar los datos de fresado.

Ruteo de la proteccion DESAT:

- Recomendacion: mantener la pista de deteccion DESAT corta y alejada de nodos con alto dV/dt.

- Riesgo: disparo falso de la proteccion contra cortocircuito.

- Aceptacion: revisar el acoplo de ruido en el pin DESAT durante la simulacion.

Separacion de planos de masa:

- Recomendacion: separar claramente AGND, DGND y PGND y unirlos en un unico punto mediante un Net Tie.

- Riesgo: los bucles de masa inyectan ruido de potencia en el MCU.

- Aceptacion: resaltar las redes de masa en CAD para verificar la separacion.

Desacoplo de alimentacion:

- Recomendacion: colocar condensadores de bajo ESR inmediatamente en los pines de alimentacion del gate driver.

- Riesgo: caida de tension durante el pico de corriente de carga de gate.

- Aceptacion: verificar que los condensadores esten, siempre que sea posible, en la misma capa que el IC.

Revision DFM:

- Recomendacion: enviar los datos a una comprobacion DFM Guideline antes de pedir fabricacion.

- Riesgo: taladros imposibles de fabricar o trampas de acido.

- Aceptacion: informe de aprobacion del proveedor.

Errores comunes (y enfoque correcto)

Incluso los ingenieros con experiencia cometen errores en el diseño de PCB de control para inversor trifasico. Estos son los problemas que encontramos con mas frecuencia.

- Error: rutear trazas de gate drive atravesando vias.

- Correccion: cada via añade alrededor de 1.2 nH de inductancia. Mantenga el camino de carga y descarga de gate de alta corriente en la capa superior y sin cambios de capa siempre que sea posible.

- Error: ignorar la ruta de Miller Clamp.

- Correccion: el camino que evita el encendido falso por efecto Miller es tan critico como el camino de encendido. Debe mantenerse corto y ancho.

- Error: colocar el sensor de temperatura lejos del punto caliente.

- Correccion: los sensores NTC/PTC deben estar acoplados termicamente al encapsulado del IGBT/MOSFET o a la parte mas caliente del PCB, no solo cerca.

- Error: pasar por alto el equilibrio de cobre.

- Correccion: grandes pours de cobre en una cara y poco cobre en la opuesta causan alabeo durante reflow. Use copper thieving o patrones equilibrados para compensar.

- Error: pasar señales sensibles bajo el modulo de potencia.

- Correccion: nunca rutee lineas ADC o de comunicacion en capas directamente debajo de los semiconductores de potencia que conmutan. El acoplo capacitivo inyectara ruido.

- Error: marcados de serigrafia insuficientes.

- Correccion: identifique claramente las zonas de alta tension. Es un requisito de seguridad para personal de montaje y pruebas.

FAQ

P: Cuantas capas son recomendables para un PCB de control de inversor trifasico? R: Para accionamientos sencillos de baja tension pueden bastar 2 capas. En variadores industriales de 400 V o mas, 4 capas son lo habitual para disponer de planos de masa solidos. Los inversores EV complejos usan a menudo 6 capas o mas.

P: Debo poner un plano de masa bajo el transformador o acoplador de aislamiento? R: En absoluto. Debe eliminarse todo el cobre de todas las capas bajo los componentes de la barrera de aislamiento para mantener creepage y clearance.

P: Que peso de cobre debo especificar? R: Para las señales de control basta 1 oz (35µm). Si la placa tambien conduce la corriente principal, pueden ser necesarios estandares Industrial Control PCB con 2 oz o 3 oz de cobre.

P: Como reduzco EMI en el layout? R: Minimice el area de lazo en los caminos de alto di/dt, especialmente gate loops y DC link loops. Utilice un plano de masa continuo para la logica de control. Si los objetivos de eficiencia lo permiten, ralentice los flancos con resistencias de gate.

P: Puedo usar material FR4 en inversores de alta tension? R: Si. El FR4 estandar es adecuado para la mayoria de inversores industriales hasta 1000 V siempre que el layout respete las reglas de creepage. Para temperaturas continuas muy elevadas, por encima de 130°C, se recomienda FR4 de alto Tg.

P: Cual es la mejor forma de probar el layout antes de trabajar a plena potencia? R: Empiece con la prueba de doble pulso a tensiones mas bajas. Asi puede comprobar caracteristicas de conmutacion y ringing del gate driver sin arriesgar la etapa de potencia completa.

Paginas y herramientas relacionadas

- Heavy Copper PCB: esencial en inversores donde la placa de control tambien distribuye una parte relevante de la potencia.

- Industrial Control PCB: capacidades especificas para electronica de control industrial robusta y de alta fiabilidad.

- DFM Guidelines: compruebe su layout frente a restricciones de fabricacion antes de enviarlo.

- Power & Energy PCB: soluciones adaptadas a inversores solares, eolicos y conectados a red.

Glosario (terminos clave)

| Termino | Definicion |

|---|---|

| DC Link | Fuente de tension continua, normalmente un banco de condensadores, que alimenta el inversor. |

| IGBT | Insulated Gate Bipolar Transistor. Interruptor de potencia habitual en inversores de alta tension. |

| MOSFET | Metal-Oxide-Semiconductor Field-Effect Transistor. Utilizado en inversores de menor tension o de mayor frecuencia. |

| Gate Driver | Circuito integrado que amplifica señales logicas de baja potencia hasta impulsos de alta corriente para accionar gates de IGBT/MOSFET. |

| Dead Time | Pequeña pausa entre apagar un transistor y encender el otro en la misma rama para evitar cortocircuitos. |

| PWM | Pulse Width Modulation. Metodo empleado para codificar niveles analogicos en pulsos digitales. |

| dV/dt | Velocidad de cambio de tension. Un dV/dt alto puede acoplar ruido a traves de barreras de aislamiento. |

| dI/dt | Velocidad de cambio de corriente. Un dI/dt alto induce picos de tension en inductancias parasitas. |

| Conexion Kelvin | Metodo de conexion a 4 hilos para medir tension sobre un componente, como un shunt, sin incluir la caida de tension de los conductores de corriente. |

| Creepage | Distancia mas corta entre dos partes conductoras siguiendo la superficie del aislante. |

| Clearance | Distancia mas corta entre dos partes conductoras a traves del aire. |

| EMI | Electromagnetic Interference. Ruido generado por la conmutacion que afecta a otras electronicas. |

| EMC | Electromagnetic Compatibility. Capacidad del equipo para funcionar sin causar ni sufrir EMI. |

Conclusion (siguientes pasos)

Dominar el layout PCB de control para inversor trifasico exige equilibrar teoria electrica, normas de seguridad y restricciones fisicas de fabricacion. Un layout bien resuelto protege el cerebro digital sensible frente a la brutalidad de la potencia y garantiza asi eficiencia y fiabilidad.

Cuando este listo para pasar del diseño al prototipo, APTPCB puede ayudarle. Para obtener una cotizacion precisa y una revision DFM completa, envie por favor:

- Archivos Gerber en formato RS-274X.

- Detalles del stackup como peso de cobre y espesor dielectrico.

- Especificaciones de material como clase Tg y valor CTI para alta tension.

- Requisitos especiales como fresado de ranuras de aislamiento, cobre pesado o colores concretos de solder mask para mejorar el contraste.

Si estos datos se entregan con claridad, el proceso de fabricacion sera mas rapido y podremos producir una placa que cumpla con las exigencias severas de la electronica de potencia.