Puntos clave

Antes de sumergirnos en las profundidades técnicas de las interconexiones cuánticas, aquí están los puntos esenciales que los equipos de ingeniería deben comprender.

- El material importa: El hilo de oro estándar a menudo no es adecuado para qubits superconductores debido a la resistencia residual; el aluminio (1% silicio) es el estándar para entornos criogénicos.

- La inductancia es parasitaria: La longitud y la altura del bucle del wirebond añaden directamente inductancia, lo que puede desintonizar la frecuencia del qubit.

- Criticidad del acabado superficial: Los materiales magnéticos (como el níquel estándar en ENIG) destruyen la coherencia del qubit; los acabados no magnéticos como ENEPIG u oro blando son obligatorios.

- Estrés mecánico: La interfaz debe sobrevivir a ciclos térmicos repetidos desde temperatura ambiente (300K) hasta rangos de miliKelvin (mK) sin levantarse.

- Respuesta en frecuencia: El wirebond actúa como una discontinuidad en la línea de transmisión; mantener los enlaces cortos minimiza el desajuste de impedancia.

- Validación: Las pruebas de continuidad a temperatura ambiente son insuficientes; a menudo se requieren relaciones de resistencia de CC (RRR) y pruebas de tracción criogénicas.

Qué significa realmente el wirebonding para la interfaz de qubit (alcance y límites)

Comprender los requisitos fundamentales del wirebonding para la interfaz de qubit comienza reconociendo que la fiabilidad estándar IPC Clase 3 no es suficiente para las aplicaciones cuánticas. En la electrónica tradicional, el wirebonding conecta un chip de silicio a un marco de conexión o PCB para transmitir señales de potencia y lógicas. En el ámbito cuántico, el wirebonding para la interfaz de cúbit cumple un doble propósito: proporciona conectividad eléctrica mientras mantiene el delicado estado cuántico (coherencia) del cúbit. Esta interfaz opera en un régimen donde los fotones individuales importan, y el ruido térmico debe ser prácticamente inexistente.

El alcance de este proceso difiere del ensamblaje estándar de tres maneras:

- Régimen térmico: La unión debe mantener la integridad mecánica a temperaturas cercanas al cero absoluto (10 mK a 4 K).

- Entorno electromagnético: El propio bucle de alambre se convierte en un elemento radiante. Si no se controla, actúa como una antena, captando ruido o irradiando energía que causa decoherencia.

- Superconductividad: Para los cúbits superconductores, la propia unión por hilo a menudo debe volverse superconductora para evitar la disipación de energía (calentamiento) en el punto de conexión.

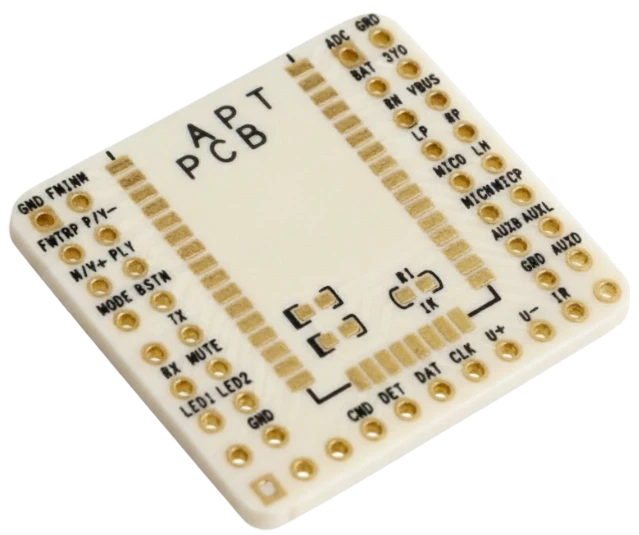

APTPCB (APTPCB PCB Factory) a menudo aconseja a los clientes que el diseño del sustrato (PCB) y el proceso de ensamblaje (wirebonding) no pueden tratarse por separado en aplicaciones cuánticas. La geometría de la almohadilla en el PCB dicta la forma de la unión, lo que a su vez dicta la inductancia.

Métricas importantes para el wirebonding de la interfaz de cúbit (cómo evaluar la calidad)

Una vez definido el alcance, los ingenieros deben cuantificar el éxito utilizando métricas específicas que van más allá de las fuerzas de tracción estándar. La siguiente tabla describe los indicadores críticos de rendimiento para una interfaz cuántica de alta calidad.

| Métrica | Por qué es importante | Rango típico / Factor | Cómo medir |

|---|---|---|---|

| Inductancia parasitaria | La alta inductancia altera la frecuencia de resonancia del cúbit y limita el ancho de banda. | 0,5 nH a 2,0 nH (dependiente de la geometría) | VNA (Analizador de Red Vectorial) o simulación TDR. |

| Resistencia al cizallamiento del enlace | Asegura la fiabilidad mecánica durante la contracción/expansión térmica. | > 5 gramos (dependiendo del diámetro del hilo) | Probador de enlaces Dage (prueba de cizallamiento). |

| Corriente crítica (Ic) | La corriente máxima que el enlace puede soportar sin romper la superconductividad. | > 10 mA (específico de la aplicación) | Medición con sonda de 4 puntos a temperaturas criogénicas. |

| Desajuste de impedancia | Las reflexiones en la interfaz del enlace causan pérdida de señal y ondas estacionarias. | Objetivo 50 Ohms (VSWR < 1,2) | TDR (Reflectometría en el Dominio del Tiempo). |

| Relación de Resistencia Residual (RRR) | Indica la pureza del metal y su rendimiento a bajas temperaturas. | > 10 para hilos de Al | Relación de Resistencia a 300K vs 4K. |

| Consistencia de la altura del bucle | Las variaciones en la altura cambian la inductancia, causando una dispersión de la frecuencia del cúbit. | Tolerancia de ± 10 µm | Perfilado óptico / AOI 3D. |

Cómo elegir el wirebonding para la interfaz del cúbit: guía de selección por escenario (compensaciones)

Con las métricas establecidas, el siguiente paso es seleccionar la estrategia de unión adecuada basada en su arquitectura cuántica específica. Las diferentes modalidades de cúbits (superconductores, de espín, de iones atrapados) imponen distintas restricciones al proceso de wirebonding.

Escenario 1: Cúbits Transmon Superconductores

- Requisito: Trayectoria de resistencia cero y ruido magnético mínimo.

- Recomendación: Unión por cuña de aluminio (Aluminum Wedge Bonding).

- Compensación: Los hilos de aluminio son más difíciles de unir a ciertas superficies de oro que los hilos de oro. Debe asegurarse de que el acabado superficial de la PCB sea compatible (por ejemplo, oro blando grueso o almohadillas de aluminio). Se prefiere la unión por cuña ultrasónica a la unión por bola termosónica para evitar calentar las sensibles uniones Josephson.

Escenario 2: Cúbits de Espín en Silicio

- Requisito: Líneas de puerta de alta densidad, menos sensibles al ruido magnético que los transmones, pero el espacio es limitado.

- Recomendación: Unión por bola de oro (si se utiliza una barrera no magnética).

- Compensación: El oro es más fácil de unir y permite un paso más estrecho (paso fino). Sin embargo, el oro no es un superconductor. Si las líneas transportan una corriente significativa, la disipación de calor se convierte en un problema.

Escenario 3: Líneas de Control de Alta Frecuencia (4-8 GHz)

- Requisito: La adaptación de impedancia es fundamental para evitar la reflexión de la señal.

- Recomendación: Unión por cinta (Ribbon Bonding).

- Compromiso: Usar una cinta plana en lugar de un hilo redondo reduce la inductancia y mejora la adaptación de impedancia, acercándola a 50 Ohmios. El compromiso es que la unión por cinta requiere herramientas de cuña especializadas y pads de unión más grandes en la PCB de alta frecuencia.

Escenario 4: Integración 3D / Módulos multichip

- Requisito: Conectar múltiples chips cuánticos vertical u horizontalmente.

- Recomendación: Unión por cuña de bucle corto.

- Compromiso: Mantener los bucles extremadamente cortos minimiza la inductancia, pero aumenta el estrés mecánico durante los ciclos térmicos. El desajuste del CTE (Coeficiente de Expansión Térmica) entre el chip y el interposer debe ser mínimo.

Escenario 5: Ajuste y sintonización de frecuencia

- Requisito: Ajuste de la inductancia post-fabricación.

- Recomendación: Perfilado de bucle adaptativo.

- Compromiso: Similar a la sintonización y ajuste de precisión de antenas en la fabricación de RF, la forma del wirebond se puede ajustar para "sintonizar" la inductancia. Esto requiere un equipo de unión altamente avanzado capaz de perfiles de bucle complejos, lo que aumenta el costo de fabricación.

Escenario 6: Prototipado rápido

- Requisito: Rápida respuesta para probar diseños de chips.

- Recomendación: Unión por cuña manual o semiautomática.

- Compromiso: La unión manual es más lenta y menos consistente (mayor variación de inductancia) pero permite pruebas inmediatas sin programación compleja. Adecuado para pruebas de concepto, no para producción.

Puntos de control para la implementación de la interfaz de cúbit mediante wirebonding (del diseño a la fabricación)

Seleccionar el método correcto es solo la mitad de la batalla; se requieren protocolos de implementación rigurosos para asegurar que la interfaz sobreviva la transición del diseño al refrigerador de dilución.

Fase 1: Diseño de PCB/Sustrato

- Selección del acabado superficial: Especificar ENEPIG (Níquel químico, Paladio químico, Oro por inmersión) u Oro blando. Evitar HASL estándar o Estaño por inmersión. Asegurarse de que la capa de Níquel sea no magnética (alto contenido de fósforo) si se usa, o eliminarla por completo.

- Geometría de las almohadillas: Diseñar las almohadillas para acomodar el «pie» de la unión por cuña. Para la unión por cinta, las almohadillas deben ser rectangulares y estar alineadas con la trayectoria de la señal.

- Conexión a tierra: Rodear las almohadillas de señal con vías de tierra (configuración tierra-señal-tierra) para mantener la impedancia hasta el punto de unión.

Fase 2: Suministro de materiales

- Pureza del hilo: Suministrar hilo de Aluminio 99,999% (5N) o Aluminio-1% Silicio. Las impurezas dispersan los electrones y rompen la superconductividad.

- Calidad del sustrato: Utilizar PCB cerámicas (Alúmina o Nitruro de Aluminio) para una mejor coincidencia térmica con los chips de silicio en comparación con FR4.

Fase 3: Preparación previa a la unión

- Limpieza con plasma: Implemente un ciclo de limpieza con plasma de Argón/Oxígeno inmediatamente antes de la unión para eliminar contaminantes orgánicos de los pads. Esto es crítico para la fiabilidad de la unión por cuña.

- Desgasificación (Bake-out): Elimine la humedad del sustrato. La humedad atrapada en la PCB puede desgasificarse en la cámara de vacío o congelarse/expandirse durante el enfriamiento, agrietando la unión.

Fase 4: Proceso de Unión

- Optimización de parámetros: Realice un DOE (Diseño de Experimentos) para la potencia ultrasónica, el tiempo y la fuerza. La ventana para los chips cuánticos es estrecha: demasiada potencia daña el cúbit; muy poca resulta en desprendimientos.

- Control de bucle: Programe la máquina de unión para perfiles de "bucle bajo" o "bucle plano" para minimizar la inductancia parasitaria.

Fase 5: Validación Post-Unión

- Prueba de tracción no destructiva: Aplique una fuerza muy ligera (por ejemplo, 1g) para asegurar que no existan "uniones falsas".

- Inspección visual: Verifique la presencia de grietas en el talón y la precisión de la colocación de la unión.

- Cualificación criogénica: Muestree unidades aleatoriamente para pruebas de choque térmico (inmersión en nitrógeno líquido) seguidas de comprobaciones de continuidad.

Unión de cables para la interfaz de cúbits: errores comunes (y el enfoque correcto)

Incluso los ingenieros experimentados encuentran escollos al pasar de las interconexiones clásicas a las cuánticas.

Error 1: Uso de subcapas magnéticas

- El error: Usar ENIG estándar (Níquel Químico Oro por Inmersión) donde la capa de Níquel es magnética.

- La Consecuencia: El campo magnético del Níquel interrumpe el estado de espín o el flujo del cúbit, reduciendo el tiempo de coherencia.

- La Solución: Especificar Níquel-Fósforo no magnético o usar un acabado directo de Oro sobre Cobre o Plata.

Error 2: Ignorar la Desigualdad del CTE

- El Error: Unir un chip de Silicio directamente a una placa FR4 estándar con cables cortos y tensos.

- La Consecuencia: Cuando se enfría a 10mK, el FR4 se encoge mucho más que el Silicio. La tensión rompe los cables.

- La Solución: Usar un interposer con CTE (Coeficiente de Expansión Térmica) igualado o dejar un "bucle de servicio" (holgura) en el cable, aunque esto compromete la inductancia.

Error 3: Sobre-unión (Demasiada fuerza/potencia)

- El Error: Aplicar alta energía ultrasónica para asegurar una unión fuerte.

- La Consecuencia: Esto puede crear cráteres (micro-grietas) en el sustrato subyacente o dañar las delicadas uniones Josephson en el chip.

- La Solución: Usar la energía mínima requerida para una unión fiable. Validar primero con pruebas de cizallamiento en muestras de prueba.

Error 4: Bucles de cable largos

- El Error: Permitir bucles grandes y arqueados para facilitar el espacio de unión.

- La Consecuencia: Aumenta significativamente la inductancia ($L \approx 1 \text{nH/mm}$). Esto actúa como un filtro de paso bajo y crea discontinuidades de impedancia.

- La Solución: Mantener las uniones lo más cortas y planas posible. Colocar la cavidad del chip o el estante de la PCB a la misma altura que la superficie del chip (montaje empotrado).

Error 5: Descuidar la Eliminación de Óxido en el Aluminio

- El error: La unión a almohadillas de aluminio que se han oxidado sin una limpieza adecuada.

- La consecuencia: Contactos de alta resistencia o uniones que no se adhieren.

- La solución: Se requiere una limpieza agresiva con plasma o un fregado mecánico (parte de la acción de unión por cuña) para romper la capa de óxido.

Error 6: Asumir que las pruebas a temperatura ambiente equivalen al rendimiento criogénico

- El error: Aprobar una unidad basándose únicamente en comprobaciones de continuidad a 300K.

- La consecuencia: Las uniones pueden fallar mecánicamente al enfriarse (circuito "abierto") o exhibir una resistencia no lineal.

- La solución: Realizar pruebas de "inmersión en frío" en lotes de muestra.

Preguntas frecuentes sobre el wirebonding para la interfaz de cúbits (costo, plazo de entrega, materiales, pruebas, criterios de aceptación)

P: ¿Cómo afecta el wirebonding para la interfaz de cúbits al costo del ensamblaje de la PCB? R: Aumenta el costo debido a la necesidad de materiales especializados (hilo de Al de alta pureza), sustratos especializados (Cerámica o Rogers) y el menor rendimiento de la unión por cuña de precisión en comparación con la unión por bola de alta velocidad. Además, la NRE (Ingeniería No Recurrente) para configurar los perfiles de bucle es mayor.

P: ¿Cuál es el plazo de entrega típico para los sustratos adecuados para el wirebonding cuántico? R: El FR4 estándar es rápido, pero los sustratos de grado cuántico como la alúmina o los laminados de alta frecuencia a menudo tienen plazos de entrega de 3 a 5 semanas. APTPCB ofrece servicios acelerados para el ensamblaje NPI para reducir este plazo. P: ¿Podemos usar alambre de cobre en lugar de aluminio para una mejor conductividad? R: Generalmente, no. El cobre se oxida rápidamente y es más duro, lo que requiere fuerzas de unión más altas que pueden dañar el chip. Además, el aluminio se vuelve superconductor a 1.2K, lo que lo convierte en un conductor perfecto de resistencia cero para circuitos cuánticos, mientras que el cobre no.

P: ¿Cuáles son los criterios de aceptación para una unión de alambre cuántica? R: Los criterios suelen incluir:

- Resistencia al cizallamiento > X gramos (basado en el diámetro del alambre).

- Precisión de colocación dentro de ±10 µm.

- Variación de la altura del bucle < 5 µm.

- Cero grietas en el talón visibles con un aumento de 100x.

- Resistencia de CC < 0.5 Ohms (a temperatura ambiente).

P: ¿Cómo se prueban las uniones de alambre sin destruir el cúbit? R: Utilizamos "cupones de prueba" o chips ficticios unidos con los mismos parámetros para pruebas destructivas (tracción/cizallamiento). Los chips cuánticos reales se someten a una inspección visual del 100% (AOI) y a comprobaciones de continuidad de baja corriente si el diseño lo permite.

P: ¿Por qué se menciona "sintonización y ajuste de antena" en el contexto de la unión de alambre? R: Aunque es principalmente un término de RF, el concepto se aplica aquí. El bucle de alambre actúa como un inductor. Al ajustar con precisión la forma del bucle (recortando la longitud/altura), los ingenieros pueden "sintonizar" la impedancia de la interconexión para que coincida con la línea de transmisión, minimizando la pérdida de señal.

P: ¿APTPCB maneja la unión de alambre o solo la fabricación de PCB? A: APTPCB ofrece soluciones llave en mano. Fabricamos el sustrato de alto rendimiento y podemos gestionar el proceso PCBA, incluyendo los requisitos de unión especializados a través de nuestros socios de ensamblaje avanzados.

Recursos para wirebonding para interfaz de qubit (páginas y herramientas relacionadas)

Para ayudarle aún más en su proceso de diseño, utilice los siguientes recursos disponibles en nuestra plataforma.

- Selección de sustrato: Explore las capacidades de PCB cerámicas para la estabilidad criogénica.

- Integridad de la señal: Utilice nuestra calculadora de impedancia para diseñar sus trazas antes de que lleguen a la almohadilla de wirebonding.

- Acabados de superficie: Lea sobre los acabados de superficie de PCB para elegir la opción no magnética adecuada.

- Servicios de ensamblaje: Conozca nuestro ensamblaje llave en mano para proyectos complejos y de alta mezcla.

Glosario de wirebonding para interfaz de qubit (términos clave)

| Término | Definición |

|---|---|

| Wedge Bonding | Una técnica de unión que utiliza energía ultrasónica y presión para fijar el cable; preferida para paso fino y cable de aluminio. |

| Ball Bonding | Una técnica que forma una bola en la punta del cable; generalmente más rápida pero requiere calor (termosónico) y típicamente usa oro. |

| Superconductividad | Un estado en el que un material (como el aluminio a <1,2 K) tiene resistencia eléctrica cero. |

| Cúbit (Bit Cuántico) | La unidad básica de información cuántica; altamente sensible al ruido y al calor. |

| Inductancia (Parásita) | Inductancia no deseada añadida por el bucle de cable, que afecta la frecuencia y la calidad de la señal. |

| Criogénico | Relacionado con temperaturas extremadamente bajas (típicamente por debajo de 100K, hasta el rango de mK). |

| CTE (Coeficiente de Expansión Térmica) | La tasa a la que un material se expande/contrae con los cambios de temperatura. La falta de coincidencia provoca fallos en la unión. |

| ENEPIG | Níquel Químico Paladio Químico Oro por Inmersión; un acabado superficial universal bueno para el wire bonding. |

| Efecto Pelicular | La tendencia de la corriente de alta frecuencia a fluir cerca de la superficie del conductor; relevante para las líneas de control de microondas. |

| Unión Josephson | Un componente clave de los cúbits superconductores; extremadamente sensible a las descargas electrostáticas y al calor. |

| Interposer | Una capa intermedia (silicio o cerámica) utilizada para enrutar señales entre el chip y la PCB principal. |

| Grieta en el Talón | Una fractura en el punto donde el cable transiciona de la almohadilla de unión al bucle; un modo de fallo común. |

Conclusión: wire bonding para la interfaz de cúbits – próximos pasos

Dominar el wire bonding para la interfaz de cúbits implica gestionar la intersección de la robustez mecánica, la física criogénica y la ingeniería de microondas. Requiere alejarse de las mentalidades estándar de "solo continuidad" y adoptar un enfoque riguroso para la pureza del material, la geometría del bucle y el acabado de la superficie. Si está listo para llevar su procesador cuántico o electrónica de control del diseño a la fabricación, asegúrese de que su socio de fabricación comprenda estas limitaciones únicas.

Al solicitar un presupuesto a APTPCB, por favor proporcione:

- Archivos Gerber: Con indicaciones claras de las ubicaciones de las almohadillas de unión (bond pads).

- Detalles del apilamiento (Stackup): Incluyendo materiales dieléctricos específicos (por ejemplo, Rogers, Cerámica).

- Especificaciones del acabado superficial: Indique explícitamente "No magnético" si es necesario.

- Diagrama de unión de cables (Wirebond): Especificando las alturas de bucle objetivo y el material del cable (Al vs. Au).

- Temperatura de funcionamiento: (por ejemplo, 4K, 10mK) para que podamos asesorarle sobre los riesgos de CTE.

El hardware cuántico fiable comienza con una interfaz fiable. Contáctenos hoy mismo para revisar su diseño en cuanto a su fabricabilidad.