Advanced Engineering Guide

La realidad de ingenieria en la fabricacion de PCB de alto numero de capas

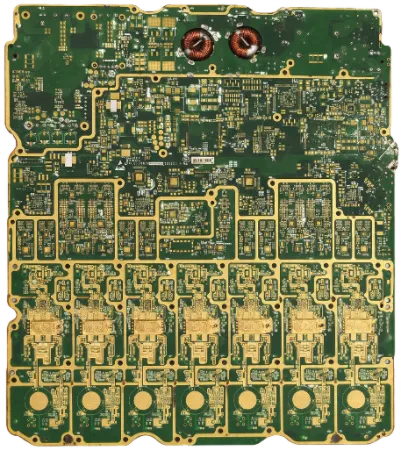

Disenar un backplane de 32 capas o una motherboard de AI de 24 capas en software ECAD es un complejo rompecabezas de enrutamiento, pero fabricarlo es una batalla contra la fisica, la quimica y la termodinamica. A medida que aumenta el numero de capas, el margen de error se reduce exponencialmente. En APTPCB colaboramos con hardware engineers senior de todo el mundo para llevar estos disenos extremos del entorno digital a la realidad fisica. A continuacion se presenta un analisis profundo de los obstaculos de ingenieria en la fabricacion de alto numero de capas y de como los resolvemos.

1. La tirania del registro y del escalado dimensional

La mayor amenaza para una placa de alto numero de capas es el fallo de registro. Un PCB se construye prensando capas alternas de cores completamente curados y prepreg sin curar bajo calor extremo y presion hidraulica. Durante este proceso de laminacion, los materiales se expanden y, al curarse la resina y enfriarse, se contraen. Este escalado dimensional es anisotropico: se contrae de forma distinta en las direcciones X y Y del tejido de fibra de vidrio.

En una placa de 4 capas, un pequeno desplazamiento puede ser absorbido facilmente por el annular ring, es decir, el pad de cobre que rodea un orificio taladrado. En una placa de 40 capas, si las capas internas se desplazan de forma inconsistente, una broca mecanica que desciende por la placa acabara saliendo fuera del pad de cobre en la capa 25, interrumpiendo la conexion o provocando un cortocircuito fatal con un plano de tierra cercano.

La solucion APTPCB: nuestros ingenieros CAM aplican factores de escalado no lineales al artwork de cada capa y predicen matematicamente la tasa de contraccion segun la densidad de cobre de esa capa. Durante el layup utilizamos sistemas de X-Ray induction bonding para alinear fisicamente las capas internas entre si antes del ciclo de prensado, garantizando una precision de registro capa a capa de ±1.5 mil.

2. Metalizado de alta relacion de aspecto: el reto capilar

A medida que aumenta el numero de capas, la placa se vuelve mas gruesa. Una placa de 32 capas puede alcanzar facilmente 5.0 mm (200 mil) de espesor. Si necesitas perforar un via de 10 mil (0.25 mm) a traves de esa placa, creas un tubo capilar microscopico con una relacion de aspecto de 20:1.

Los sistemas estandar de galvanoplastia DC dependen de la dinamica de fluidos para hacer circular banos quimicos ricos en cobre a traves de los orificios. En un via 20:1, el fluido del centro del barril se estanca. Los iones de cobre se agotan y el proceso de metalizado se detiene, produciendo un via con cobre grueso en la superficie pero peligrosamente fino, o incluso inexistente, en la parte central. Bajo el calor extremo del SMT reflow o del wave soldering, la expansion en el eje Z de la placa rompera facilmente ese barril de cobre delgado, provocando circuitos abiertos intermitentes muy dificiles de depurar.

La solucion APTPCB: para placas que superan una relacion de aspecto de 10:1 utilizamos Periodic Reverse Pulse Plating. En lugar de una corriente continua constante, el sistema impulsa la corriente hacia delante y la invierte brevemente. El pulso inverso actua como una "bomba" electrica, retirando los quimicos agotados y atrayendo fluido fresco y rico en cobre hacia el centro del via. Asi se garantiza una pared de barril uniforme y gruesa capaz de soportar multiples ciclos de reflow sin plomo.

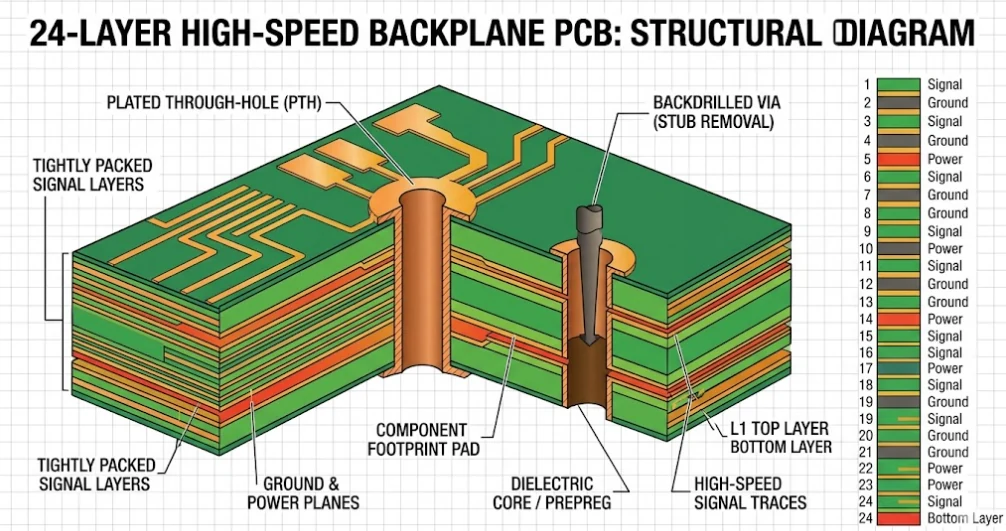

3. Eliminar la resonancia de senal con backdrilling de precision

En arquitecturas digitales de alta velocidad, como PCIe Gen5, 100G/400G Ethernet y 112G PAM4, la geometria fisica del via se convierte en un componente RF activo. Imagina una senal que viaja desde la Layer 1 hasta la Layer 5 en un backplane de 24 capas. La senal sale correctamente en la Layer 5, pero el barril de cobre restante del via, que continua desde la Layer 6 hasta la Layer 24, actua como una antena sin terminar, es decir, un "via stub". Ese stub refleja energia electromagnetica de vuelta al canal, causa interferencia destructiva y cierra el diagrama de ojo.

La solucion APTPCB: para rescatar la integridad de senal utilizamos Controlled-Depth Backdrilling. Mediante maquinas CNC avanzadas equipadas con tecnologia de deteccion conductiva de superficie, la broca entra desde la parte inferior de la placa (Layer 24) y elimina el stub de cobre no deseado, deteniendose con precision antes de alcanzar la capa activa de senal (Layer 5). Alcanzamos de forma rutinaria precisiones de profundidad de ±50μm, dejando un stub residual inocuo de menos de 8-10 mil y liberando asi el canal de resonancias destructivas.

4. Gestion de la impedancia en arquitecturas gruesas

En una placa de 6 capas, una traza single-ended de 50Ω puede requerir una anchura de 6 mil. En una placa de 32 capas, como es necesario utilizar prepregs ultrafinos, por ejemplo de 2 mil, para mantener manejable el espesor total, la distancia entre la traza de senal y su plano de referencia se reduce drásticamente. Para mantener esos mismos 50Ω, la anchura de la traza debe reducirse proporcionalmente, a menudo hasta 2.5 o 3 mil.

Grabar una traza de 3 mil con una tolerancia de impedancia de ±5% exige un dominio quimico absoluto. La solucion APTPCB: utilizamos Laser Direct Imaging (LDI) para lograr una precision de exposicion sub-mil, combinada con lineas de grabado asistidas por vacio que extraen el acido de entre trazas muy proximas para evitar el undercut. Modelamos cada estructura de impedancia en Polar Si9000 y verificamos fisicamente el resultado mediante cupones TDR en cada panel de produccion.