Contenido

- Highlights

- Reducir el coste PCB sin sacrificar yield: definicion y alcance

- Reducir el coste PCB sin sacrificar yield: reglas y especificaciones

- Reducir el coste PCB sin sacrificar yield: pasos de implementacion

- Reducir el coste PCB sin sacrificar yield: troubleshooting

- 6 reglas esenciales para reducir coste sin perder yield

- FAQ

- Solicitar cotizacion / revision DFM para reducir coste sin sacrificar yield

- Conclusion

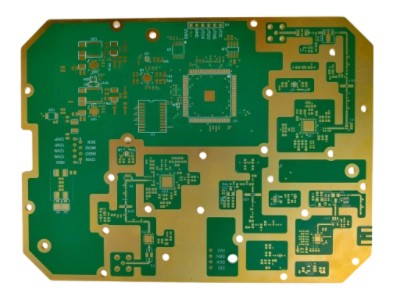

Reducir el coste de una PCB no consiste en empeorar calidad, sino en eliminar requisitos que suben el precio sin aportar rendimiento ni fiabilidad reales. Entender como reducir el coste PCB sin sacrificar yield exige equilibrar DFM, material y limites reales de fabrica.

Quick Answer

Para reducir el coste PCB sin sacrificar yield, el objetivo es mantener el diseno dentro de capacidades estandar.

- Estandarizar materiales: FR4 TG150-TG170 salvo necesidad real RF o high-speed.

- Optimizar panelizacion: buscar mas del 80 % de aprovechamiento.

- Reducir brocas: menos cambios de herramienta implican menos tiempo CNC.

- Relajar tolerancias: usar +/- 0.10 mm si no hace falta +/- 0.05 mm.

- Evitar HDI: blind y buried vias encarecen mucho el proceso.

- Verificar en DFM: localizar cost drivers antes de cotizar.

Highlights

- Uso de panel: uno de los costes ocultos mas importantes.

- Numero de capas: bajar capas no ayuda si obliga a usar HDI.

- Acabado superficial: ENIG es fiable pero mas caro que HASL u OSP.

- Gestion de vias: un aspect ratio razonable protege el yield.

Reducir el coste PCB sin sacrificar yield: definicion y alcance

El precio de una PCB combina coste de material, coste de proceso y perdidas de yield. Una placa mas pequena no siempre es mas barata si obliga a usar pistas de 3 mil, microvias laser o tolerancias especiales.

La reduccion de coste real llega cuando el diseno se mantiene en la zona estable de fabricacion. Una FR4 PCB estandar con 5 mil de pista y espacio es mucho mas economica que una version de 3 mil porque el grabado es mas robusto y el yield mas alto. Del mismo modo, un stackup par sigue siendo mas seguro que un numero impar de capas.

Palanca tecnica → impacto practico

| Palanca / especificacion | Impacto practico (yield/coste/fiabilidad) |

|---|---|

| Uso del panel | Impacto alto. Mala utilizacion equivale a pagar material desperdiciado. |

| Tecnologia via | Driver critico. Blind y buried vias anaden ciclos de laminacion. |

| Trace / Space | Driver de yield. Por debajo de 3.5 mil el proceso es mucho mas sensible. |

| Surface Finish | Coste vs. assembly. HASL es barato, ENIG es plano pero mas caro. |

| Numero y tamano de taladros | Tiempo de maquina. Muchas perforaciones o drills pequenos aumentan tiempo CNC. |

Reducir el coste PCB sin sacrificar yield: reglas y especificaciones

| Regla | Valor recomendado | Por que importa | Como verificar |

|---|---|---|---|

| Min Trace / Space | ≥ 5 mil / 5 mil | Por debajo de 4 mil el grabado se vuelve mas delicado. | Ejecutar DRC. |

| Min Mechanical Drill | ≥ 0.25 mm | Brocas pequenas rompen antes. | Revisar tabla de drills. |

| Annular Ring | ≥ 5 mil | Evita breakout con pequenas desviaciones. | Comparar pad y agujero. |

| Layer Count | Numero par | Un stackup impar favorece warpage. | Revisar PCB Stackup. |

| Board Thickness | 1.6 mm | Los espesores especiales suelen costar mas. | Revisar propiedades. |

| Copper Weight | 1 oz | El cobre pesado requiere mas tiempo de grabado. | Aumentar solo si es necesario. |

Reducir el coste PCB sin sacrificar yield: pasos de implementacion

Proceso de implementacion

Secuencia recomendada

Empezar con el stackup mas simple que cumpla los requisitos electricos.

Colocar componentes para bajar longitud de pistas, cruces y vias.

Ajustar dimensiones y array para meter mas placas por panel.

Eliminar procesos especiales no indispensables.

Reducir el coste PCB sin sacrificar yield: troubleshooting

1. Warpage y bowing

Problema: stackup asimetrico o retirada de copper pours.

Solucion: mantener simetria y equilibrar la densidad de cobre.

2. Desalineacion de solder mask

Problema: mask dams muy finos en una placa de coste estandar.

Solucion: usar gang relief o aumentar spacing entre pads cuando sea posible.

3. Mal plating en vias

Problema: vias pequenas sobre placas gruesas elevan el aspect ratio.

Solucion: mantenerlo por debajo de 8:1 en el rango estandar.

Consulta tambien nuestras DFM Guidelines.

6 reglas esenciales para reducir coste sin perder yield

| Regla / guia | Por que importa | Valor objetivo / accion |

|---|---|---|

| Estandarizar laminado | El material estandar es mas economico y disponible. | FR4 TG150 |

| Maximizar uso del panel | Poco aprovechamiento equivale a pagar scrap. | >80 % |

| Consolidar taladros | Cada cambio de herramienta consume tiempo CNC. | <10 tamanos |

| Evitar blind/buried vias | Los ciclos extra encarecen mucho. | Solo through-hole |

| Relajar tolerancias | Tolerancias muy cerradas aumentan coste de proceso. | +/- 0.10 mm |

| Elegir bien el acabado | El oro es caro si no se necesita planitud maxima. | HASL u OSP |

FAQ

Q: Reducir capas siempre abarata?

A: No, si obliga a usar HDI o routing muy fino.

Q: OSP es mas barato que ENIG?

A: Si, aunque es mas sensible al almacenamiento y al manejo.

Q: Como influye la cantidad?

A: En Mass Production los costes de setup se reparten entre muchas unidades.

Q: Una forma no rectangular ahorra dinero?

A: En general no, porque paneliza peor.

Solicitar cotizacion / revision DFM para reducir coste sin sacrificar yield

Envia:

- Gerber Files: preferiblemente RS-274X.

- Drill File: Excellon con lista de herramientas.

- Diagrama de stackup: orden de capas y peso de cobre.

- Fabrication Drawing: color, acabado y tolerancias.

- Cantidades: prototype o produccion.

Conclusion

Reducir el coste PCB sin sacrificar yield significa disenar con inteligencia para procesos estandar, mejor uso del material y menos complejidad innecesaria. Con reglas claras sobre trace width, drill size y stackup se puede lograr un producto fiable con coste competitivo.