Las placas base de los portátiles concentran la potencia informática de clase de escritorio en placas que miden aproximadamente 250 mm × 200 mm, a menudo más pequeñas para ultrabooks. Esta compresión exige una atención cuidadosa a la integridad de la señal de alta velocidad para interfaces de memoria DDR5, una entrega de energía robusta para procesadores que consumen 45-65W (los portátiles para juegos superan los 150W combinados CPU+GPU), gestión térmica dentro de las limitaciones del chasis, y calidad de fabricación que garantice la fiabilidad a través de años de ciclos térmicos y estrés mecánico.

Esta guía aborda los desafíos específicos de PCB en el diseño de portátiles: optimización de apilamiento de capas para integridad de señal y entrega de energía, restricciones de enrutamiento DDR5 y PCIe, diseño de red de entrega de energía para procesadores modernos, estrategias térmicas que funcionan dentro de factores de forma de notebook, y las capacidades de fabricación necesarias para una calidad de producción consistente.

En Esta Guía

- Diseño de Apilamiento de Capas para Alta Velocidad e Integridad de Energía

- Requisitos de Enrutamiento de Interfaz de Memoria DDR5

- Diseño de Red de Entrega de Energía de CPU y GPU

- Gestión Térmica a Través del Diseño de PCB

- Consideraciones de Fabricación para Placas Base de Portátil

- Pruebas de Fiabilidad y Requisitos de Calidad

Diseño de Apilamiento de Capas para Alta Velocidad e Integridad de Energía

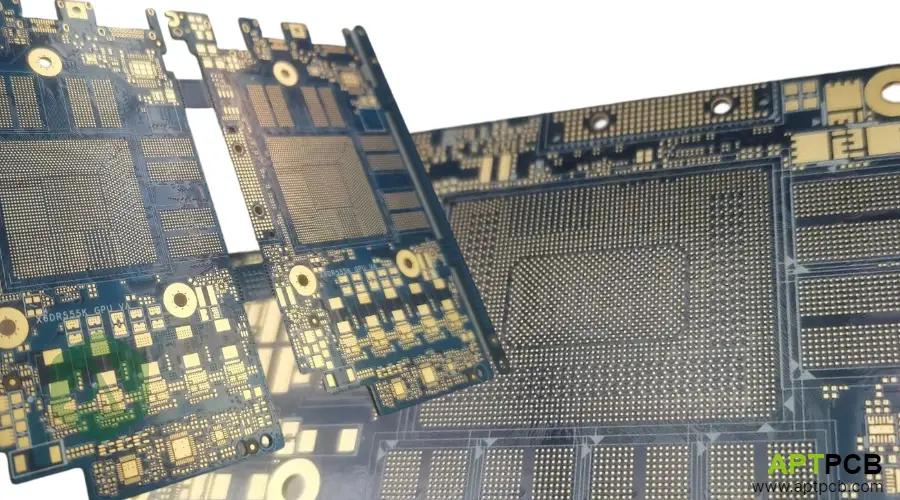

Las placas base de portátiles suelen emplear construcciones de 8-12 capas, equilibrando la capacidad de enrutamiento de señal contra las limitaciones de grosor y costo. El apilamiento debe acomodar interfaces DDR5 que operan a 4800-6400 MT/s, carriles PCIe Gen4/Gen5 a 16-32 GT/s, USB4/Thunderbolt a 40-80 Gbps, y una distribución de energía sustancial para procesadores de alto TDP—todo dentro de un grosor total de 1.0-1.6mm.

Un apilamiento típico de placa base de portátil de 10 capas dedica dos capas a planos de referencia de tierra, dos capas a distribución de energía (divididas entre múltiples rieles de voltaje), y seis capas a enrutamiento de señal. La disposición coloca señales de alta velocidad en capas inmediatamente adyacentes a planos de tierra ininterrumpidos, proporcionando impedancia controlada y caminos de retorno de corriente esenciales para la integridad de la señal a tasas de multi-gigabit.

Consideraciones de Arquitectura de Apilamiento

- Continuidad del Plano de Tierra: Las señales DDR5 y PCIe requieren referencia de tierra ininterrumpida; evite enrutar a través de áreas de plano de tierra debajo de señales de alta velocidad—las anti-pads de vía y divisiones crean discontinuidades en el camino de retorno que degradan la calidad de la señal.

- Segmentación del Plano de Energía: Los portátiles modernos requieren numerosos rieles de voltaje (VCORE, VGT para GPU, VDDQ para memoria, múltiples voltajes de E/S); los planos de energía se segmentan en regiones aisladas con atención cuidadosa a los caminos de retorno de corriente.

- Selección de Dieléctrico: El FR-4 estándar (Dk ~4.2-4.4) es suficiente para DDR5 a las velocidades actuales; PCIe Gen5 y USB4 se benefician de materiales de pérdida media (Dk ~3.5-3.8, Df <0.008) para trazas largas.

- Pesos de Cobre: Las capas de energía internas usan 1oz o 2oz de cobre para una capacidad de corriente adecuada; las capas de señal típicamente 0.5oz o 1oz dependiendo de los requisitos de corriente y restricciones de ancho de traza.

- Objetivos de Impedancia: DDR5 datos/DQS típicamente 40Ω de un solo extremo; pares diferenciales PCIe/USB4 85-100Ω; el control cuidadoso del grosor del prepreg mantiene una tolerancia de impedancia de ±10%.

- Estructuras de Vía: Vías pasantes para entrega de energía; vías ciegas/enterradas (HDI) cada vez más comunes para requisitos de densidad de fanout BGA en paquetes de CPU y PCH.

Trabajar con fabricantes con experiencia en fabricación de PCB multicapa asegura que los diseños de apilamiento sean fabricables con control de impedancia consistente a través de volúmenes de producción.

Requisitos de Enrutamiento de Interfaz de Memoria DDR5

Las interfaces de memoria DDR5 presentan desafíos significativos de enrutamiento de PCB—tasas de datos de hasta 6400 MT/s (y más allá para futuras especificaciones JEDEC) empujan los requisitos de integridad de señal a niveles previamente asociados con el diseño de RF de alta frecuencia. El cambio de arquitectura DDR5 de canal único a canal dual por DIMM significa que cada ranura de memoria requiere enrutar el doble de señales que DDR4, aunque con carga reducida.

Los requisitos de coincidencia de longitud siguen siendo estrictos: los bits de datos dentro de un carril de byte (DQ0-7) deben coincidir dentro de ±2mm; DQS strobe a datos dentro de ±5mm; comando/dirección a reloj dentro de ±25mm. A 6400 MT/s, estas tolerancias corresponden a márgenes de tiempo que no dejan espacio para variación de fabricación o efectos de temperatura—la técnica de diseño adecuada es esencial.

Pautas de Enrutamiento DDR5

- Cambios de Topología: DDR5 elimina la topología multi-drop de generaciones anteriores; punto a punto desde la CPU a cada canal DIMM simplifica el enrutamiento pero aún requiere una cuidadosa coincidencia de longitud y control de impedancia.

- Terminación en el Die: DDR5 mueve la terminación al die, eliminando resistencias de terminación a nivel de placa para señales de datos; reduce el conteo de componentes pero requiere atención a las longitudes de los stubs en conectores DIMM.

- Entrega de Energía: DDR5 integra regulación de voltaje en el DIMM (PMIC); la placa base proporciona entrada de 5V al DIMM en lugar de 1.1V VDDQ—cambia los requisitos del plano de energía frente a DDR4.

- Enrutamiento de Reloj Diferencial: DDR5 utiliza reloj diferencial; impedancia diferencial de 85Ω con acoplamiento estrecho y coincidencia de longitud dentro de ±1mm.

- Optimización de Vía: Las vías de señal de memoria deben minimizar la longitud del stub; perforación posterior disponible pero agrega costo; diseñe la colocación de vías para minimizar transiciones de capa.

- Gestión de Diafonía: Mantenga un espaciado de ancho de línea de 3× entre señales de memoria; los rellenos de tierra entre pares diferenciales ayudan al aislamiento.

Lograr un rendimiento consistente de DDR5 requiere experiencia en diseño de PCB de alta velocidad y procesos de fabricación capaces de mantener tolerancias de impedancia estrictas a través de la producción.

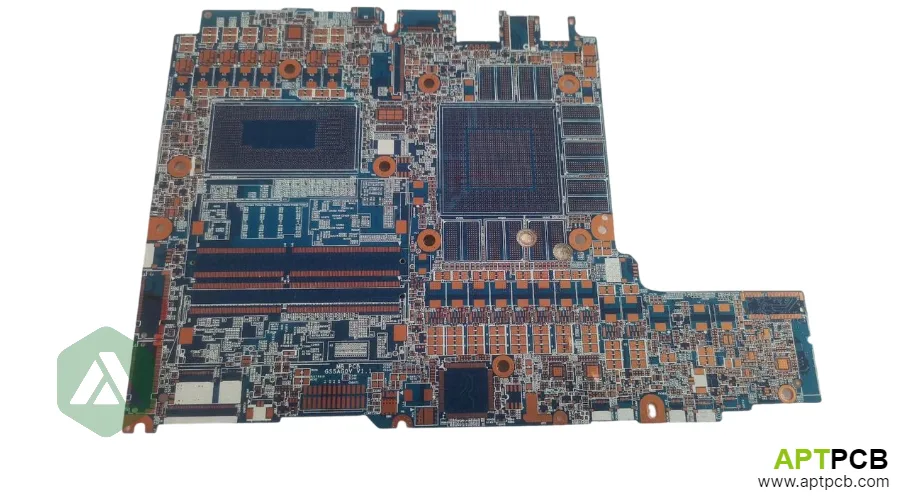

Diseño de Red de Entrega de Energía de CPU y GPU

Los procesadores de portátiles modernos exigen sistemas de entrega de energía que rivalizan con las implementaciones de escritorio—una CPU de portátil de 65W podría consumir 150A a 0.8V durante cargas transitorias, mientras que los portátiles para juegos con GPU discretas pueden superar los 300A combinados entre rieles de energía de CPU y GPU. La red de entrega de energía de PCB (PDN) debe proporcionar voltaje estable con caída mínima bajo transitorios de carga, requiriendo un diseño de plano cuidadoso, estrategia de desacoplamiento y colocación de VRM.

El objetivo de impedancia de PDN se deriva de los requisitos de corriente transitoria y variación de voltaje aceptable. Una impedancia objetivo de 5mΩ plana a 100MHz mantiene la variación de voltaje dentro del 2% para especificaciones típicas de procesadores Intel/AMD. Lograr esta impedancia requiere capacitores a granel (cientos de μF), cerámicos de frecuencia media (10-100μF), y cerámicos de alta frecuencia (100nF-10μF) distribuidos adecuadamente en la placa.

Estrategias de Diseño de Entrega de Energía

- Peso de Cobre del Plano: Los planos de energía que sirven a CPU/GPU requieren mínimo 2oz de cobre; 3oz para diseños de alto TDP—la densidad de corriente no debe exceder 35A/mm² para un aumento de temperatura aceptable.

- Optimización de Forma del Plano: El plano VCORE debe extenderse debajo del paquete del procesador con penetraciones de vía mínimas; simule la distribución de corriente para identificar cuellos de botella.

- Colocación de Capacitor de Desacoplamiento: Capacitores a granel (470μF+) cerca del VRM; cerámicos de frecuencia media distribuidos a lo largo de los bordes del plano de energía; cerámicos de alta frecuencia directamente en los pines del procesador (debajo si se usan vías ciegas).

- Colocación de Componentes VRM: Coloque inductores de etapa de potencia y MOSFETs lo más cerca posible del procesador como permitan las restricciones térmicas; caminos de entrega de energía más largos aumentan la inductancia parásita y el tiempo de respuesta transitoria.

- Detección de Corriente: Muchos diseños incluyen resistencias de detección de corriente en el camino de energía; la colocación afecta la precisión—ubique en la salida de VRM antes de las divisiones de distribución.

- Capacidad de Corriente de Vía: Las vías de entrega de energía conducen corriente significativa; use arreglos de vías en lugar de vías individuales—cada vía de 0.3mm transporta con seguridad ~1A DC; el análisis térmico verifica la temperatura de la vía.

Entender los requisitos de PCB de cobre pesado ayuda a asegurar que los diseños de entrega de energía sean fabricables y cumplan con los requisitos de transporte de corriente sin aumento excesivo de temperatura.

Gestión Térmica a Través del Diseño de PCB

Las soluciones térmicas de portátiles dependen de tubos de calor y ventiladores para eliminar el calor de los paquetes de procesador, pero el PCB juega un papel secundario crucial en la dispersión de calor y proporciona la interfaz térmica entre componentes y sistemas de enfriamiento. El diseño térmico de PCB afecta tanto el rendimiento del procesador (el enfriamiento inadecuado causa estrangulamiento) como la fiabilidad a largo plazo (el estrés de ciclo térmico causa fatiga de la junta de soldadura).

El PCB debajo de los paquetes de procesador sirve como un dispersor de calor inicial—las vías térmicas conducen el calor desde la conexión BGA de la capa superior a los planos de cobre internos y la superficie inferior. Para componentes sin contacto directo con disipador de calor (chipset, reguladores de voltaje, memoria), el PCB puede ser el camino térmico primario, haciendo que la cobertura del plano de cobre sea crítica.

Enfoques de Diseño Térmico de PCB

- Arreglos de Vías Térmicas: Arreglos densos de vías (broca de 0.3mm, paso de 0.5mm) debajo de paquetes de procesador y GPU conducen el calor verticalmente; las vías rellenas evitan la absorción de soldadura y mejoran la continuidad térmica.

- Utilización del Plano de Cobre: Maximice la cobertura de cobre en capas internas debajo de componentes térmicamente críticos; 2oz de cobre en capas térmicas si el apilamiento lo permite.

- Almohadillas Térmicas de Componentes: Los VRM, chipsets y otros componentes de potencia media a menudo usan almohadillas térmicas a planos de tierra del chasis; el PCB debe proporcionar un área de cobre adecuada en los puntos de conexión.

- Montaje de Disipador de Calor: Los disipadores de calor de portátiles se montan mediante clips de resorte o tornillos; los orificios de montaje de PCB deben proporcionar aislamiento eléctrico (si no están conectados a tierra) y soporte mecánico sin agrietarse.

- Gestión de Expansión Térmica: Los paquetes de procesador grandes (45mm+) experimentan expansión diferencial frente al PCB; el relleno inferior adecuado y el diseño correcto de la junta de soldadura evitan la propagación de grietas.

- Monitoreo de Temperatura: La colocación de sensores térmicos (termistores o diodos térmicos en paquetes de procesador) proporciona retroalimentación para el control del ventilador; asegure que los sensores tengan un buen acoplamiento térmico con los componentes monitoreados.

La integración del diseño térmico de PCB con soluciones de enfriamiento del sistema requiere comprender tanto los principios de gestión térmica como los requisitos de interfaz mecánica.

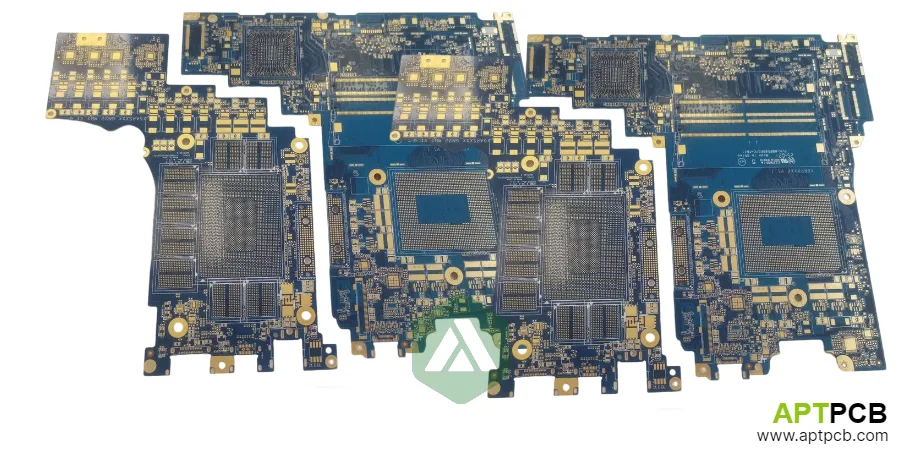

Consideraciones de Fabricación para Placas Base de Portátil

La fabricación de placas base de portátiles combina una complejidad HDI moderada (vías ciegas/enterradas para fanout BGA) con requisitos de producción de alto volumen y expectativas de calidad que se acercan a los estándares automotrices. Los principales OEM—Dell, HP, Lenovo, Apple—imponen requisitos de calificación de proveedores, incluidos estudios de capacidad de proceso, control estadístico de procesos y monitoreo continuo de fiabilidad.

Los paquetes BGA de paso fino utilizados para CPU y PCH (paso de 0.4-0.8mm) exigen un registro de perforación preciso, revestimiento de cobre controlado y aplicación consistente de máscara de soldadura. La variación de fabricación impacta directamente el rendimiento del ensamblaje—el registro de vía mal controlado o la alineación de máscara de soldadura causa defectos de ensamblaje que solo aparecen después de la colocación costosa de componentes.

Requisitos de Fabricación

- Capacidad HDI: Muchos diseños de portátiles requieren vías ciegas (estructuras 1+N+1 o 2+N+2) para un fanout BGA adecuado; vía-en-pad con construcción rellena y tapada para máxima densidad de enrutamiento.

- Registro de Perforación: Registro de vía ciega a capas subyacentes dentro de ±50μm; alineación de capa a capa a través de todas las capas dentro de ±75μm.

- Calidad de Máscara de Soldadura: Máscara de soldadura LPI con ancho de represa controlado entre almohadillas de paso fino; registro a características dentro de ±50μm.

- Acabado Superficial: ENIG preferido para fiabilidad BGA de paso fino; grosor controlado (3-5μin Au, 100-200μin Ni) previene tanto oro excesivo como insuficiente.

- Control de Impedancia: Las trazas DDR5 y PCIe requieren tolerancia de impedancia de ±8%; demostrado a través de medición TDR en cupones de producción.

- Utilización del Panel: El tamaño de la placa y la optimización del panel afectan el costo; las formas irregulares de portátiles pueden limitar la utilización del panel por debajo del 70%—consideración de diseño durante el desarrollo temprano.

Seleccionar socios de fabricación con capacidades de fabricación de PCB demostradas para estructuras HDI y aplicaciones de paso fino asegura que los diseños se traduzcan en producción fabricable.

Pruebas de Fiabilidad y Requisitos de Calidad

Las computadoras portátiles enfrentan expectativas de fiabilidad exigentes—los consumidores esperan 5+ años de vida útil con patrones de uso diario que incluyen ciclos térmicos (ciclos de suspensión-activación causan transiciones de temperatura repetidas), estrés mecánico (abrir/cerrar, llevar en bolsas), y exposición ambiental (humedad, polvo). La calidad y fiabilidad del PCB afectan directamente los costos de garantía y la reputación de la marca.

Los principales OEM especifican pruebas de calificación extensas más allá de los criterios de aceptación estándar de IPC. Los requisitos típicos incluyen ciclos térmicos acelerados (1000+ ciclos, -40°C a +105°C), exposición a la humedad (85°C/85%RH por 1000 horas), choque mecánico y vibración, y ciclos térmicos con energía que simulan condiciones de uso reales.

Marco de Calidad y Fiabilidad

- IPC Clase 2/3: La mayoría de los PCB de portátiles especifican IPC-6012 Clase 2 mínimo; productos premium y portátiles de clase empresarial pueden requerir Clase 3 para tolerancias más estrictas y fiabilidad mejorada.

- Inspección de Microsección: El análisis de sección transversal verifica la calidad del revestimiento de cobre, integridad de la estructura de vía, y grosor del dieléctrico; realizado en lotes de calificación y muestreo de producción continuo.

- Pruebas Eléctricas: Pruebas de continuidad y aislamiento al 100% mediante sonda volante o accesorio; verificación de impedancia controlada en trazas de alta velocidad.

- Ciclos Térmicos: La calificación incluye ciclos térmicos extensos; los criterios de falla incluyen aumento de resistencia de vía, delaminación de laminado y agrietamiento de máscara de soldadura.

- Resistencia CAF: La prueba de filamento anódico conductor (CAF) verifica la resistencia a la migración electroquímica entre conductores estrechamente espaciados; crítico para diseños de paso fino.

- Trazabilidad: Trazabilidad completa del lote desde materiales laminados hasta placas terminadas; esencial para la correlación de análisis de fallas y mejora continua.

Los sistemas de gestión de calidad robustos con procedimientos documentados, equipos calibrados y personal capacitado forman la base para una calidad consistente de PCB de portátiles.

Resumen Técnico

El diseño de PCB de placa base de portátil equilibra requisitos competitivos: integridad de señal de alta velocidad para interfaces DDR5 y PCIe, entrega de energía robusta para procesadores de alto TDP, gestión térmica dentro de factores de forma restringidos, y calidad de fabricación que asegura fiabilidad a largo plazo. El éxito requiere un diseño integrado considerando todos los aspectos simultáneamente en lugar de optimizar cada uno de forma aislada.

Las decisiones clave tempranas en el desarrollo de portátiles incluyen conteo de capas y arquitectura de apilamiento (determinando integridad de señal y capacidad de entrega de energía), nivel de complejidad HDI (afectando costo y complejidad de fabricación), estrategia térmica (papel del PCB en la solución de enfriamiento general), y objetivos de calidad/fiabilidad (impulsando la selección de materiales y requisitos de fabricación).

La relación con el socio de fabricación de PCB resulta crítica—los programas de portátiles implican una producción de volumen significativo con objetivos de costo agresivos, sin embargo, los requisitos de calidad se acercan a los niveles automotrices. La capacidad de fabricación, madurez del proceso y sistemas de calidad factorizan en la selección del socio junto con consideraciones de costo.