Contenido

- Puntos clave

- PCB Lead Time Checklist for Npi: definicion y alcance

- PCB Lead Time Checklist for Npi reglas y especificaciones

- PCB Lead Time Checklist for Npi pasos de implementacion

- PCB Lead Time Checklist for Npi solucion de problemas

- 6 reglas esenciales para PCB Lead Time Checklist for Npi (chuleta)

- FAQ

- Solicitar cotizacion / revision DFM para PCB Lead Time Checklist for Npi

- Conclusion

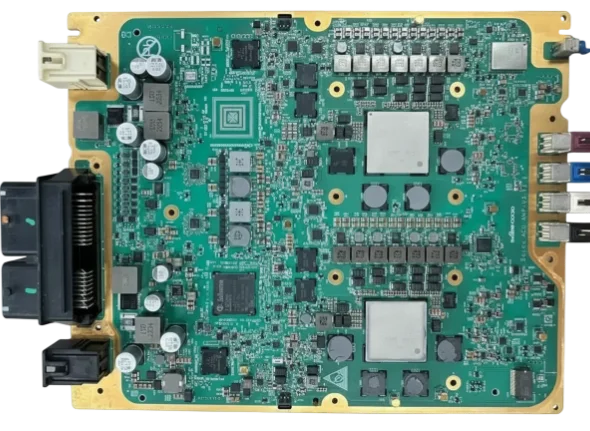

En el mundo de la fabricacion electronica, la fase de New Product Introduction (NPI) es una carrera contra el reloj en la que la precision es el combustible. Una PCB Lead Time Checklist for Npi robusta no consiste solo en contar los dias de fabricacion; consiste en identificar y eliminar los retrasos "ocultos" que aparecen antes incluso de grabar el cobre. Como Senior CAM Engineers en APTPCB, vemos miles de disenos NPI cada ano. La diferencia entre un turnaround de 3 dias y un retraso de 3 semanas suele depender de la claridad de los datos, la disponibilidad de materiales y el cumplimiento de DFM (Design for Manufacturing).

El reloj no empieza cuando sube sus Gerbers; empieza cuando se resuelven las Engineering Questions (EQs) y la planta recibe luz verde. Esta guia presenta exactamente la checklist que usamos para validar los pedidos NPI entrantes en terminos de velocidad y fiabilidad.

Quick Answer

Para optimizar su PCB Lead Time Checklist for Npi, centrese de inmediato en estos tres pilares criticos:

- Regla / rango: mantengase en materiales estandar, por ejemplo FR4 TG150/170, y stackups estandar. Los laminados especiales o espesores dielectricos unicos pueden anadir 2-3 semanas al lead time.

- Error habitual: drill charts ambiguos o requisitos de impedancia sin definir. Si el CAM engineer tiene que adivinar, su placa pasa a "On Hold".

- Metodo de verificacion: ejecute un control DFM y un BOM availability scrub antes de liberar los archivos. Asegurese de que el archivo "Read Me" indica de forma explicita la clase IPC (2 o 3) y las preferencias de stackup.

Puntos clave

- Estado de stock de materiales: el 30 % de los retrasos NPI se debe a especificar laminados fuera de stock. Revise siempre primero las listas de stock.

- Reduccion de EQ: un archivo "Read Me" claro y una netlist pueden reducir los ciclos de Engineering Questions (EQ) de 3 dias a 3 horas.

- Impacto tecnologico: pasar de through-hole estandar a HDI (High Density Interconnect) anade un minimo de 2-3 dias por cada ciclo de laminacion.

- Preparacion para assembly: en NPI turnkey, los lead times de componentes suelen superar al tiempo de fabricacion del PCB; valide la BOM desde el principio.

- Validacion: prevalidar el stackup con el fabricante garantiza el control de impedancia sin redisenos iterativos.

PCB Lead Time Checklist for Npi: definicion y alcance

Cuando hablamos de una PCB Lead Time Checklist for Npi, estamos observando el calendario global necesario para llevar un diseno desde un archivo CAD hasta un prototipo fisico ensamblado. En la fase NPI, el volumen es bajo, pero la complejidad y la urgencia son altas. El alcance de esta checklist cubre tres fases distintas: Pre-CAM (verificacion de datos), Fabrication (fisica y quimica) y Assembly (logistica de componentes).

El "Lead Time" suele entenderse mal. No es solo tiempo de maquina. Incluye:

- Fase EQ: el ida y vuelta de preguntas sobre datos faltantes o violaciones DFM.

- Preparacion de material: corte y horneado de laminados, estandar o exoticos.

- Ciclos de proceso: laminacion, taladrado, metalizado, grabado y acabado superficial.

- Testing: prueba electrica (E-Test) y AOI (Automated Optical Inspection).

Reducir el lead time exige tomar decisiones que simplifiquen estos pasos sin comprometer la integridad de la senal. Por ejemplo, utilizar servicios NPI small batch PCB manufacturing suele darle acceso a lineas fast-track, siempre que sus datos esten limpios.

Palanca tecnica / de decision → Impacto practico

| Palanca de decision / especificacion | Impacto practico (yield/coste/fiabilidad) |

|---|---|

| Seleccion del material base | FR4 estandar en stock = inicio en 24 h. Materiales exoticos como Rogers/Teflon = 1-3 semanas de lead time si no estan en stock. |

| Tecnologia de vias (HDI vs. thru) | Las blind/buried vias requieren laminacion secuencial. Cada ciclo de laminacion anade unos 2-3 dias al lead time NPI. |

| Acabado superficial | ENIG/HASL son estandar y rapidos. Hard Gold o ENEPIG exigen lineas de metalizado mas complejas y anaden 1-2 dias. |

| Tolerancia de impedancia | El ±10 % estandar es rapido. Un ±5 % ajustado exige coupon testing y posibles re-spins, con riesgo de retraso. |

PCB Lead Time Checklist for Npi reglas y especificaciones

Para que su NPI avance por la fabrica sin detenerse por "Engineering Holds", ajuste su paquete a estas especificaciones. No son limites teoricos, sino zonas seguras practicas para la fabricacion quick-turn.

| Regla | Valor recomendado | Por que importa | Como verificar |

|---|---|---|---|

| Ancho / separacion de pistas | ≥ 4 mil / 4 mil (0.1 mm) | Bajar de 3.5 mil exige grabado y AOI especializados, aumentando el riesgo de shorts/opens y el tiempo de inspeccion. | Ejecute DRC en CAD con restricciones de 4 mil. |

| Aspect ratio del taladro | ≤ 8:1 (por ejemplo, agujero de 0.2 mm en placa de 1.6 mm) | Los aspect ratios altos son dificiles de metalizar con fiabilidad. Superar 10:1 requiere ciclos de metalizado especializados y lentos. | Compruebe el espesor de la placa frente al diametro minimo de taladro. |

| Anillo anular | ≥ 4 mil (0.1 mm) sobre el taladro | Permite la desviacion mecanica del taladro sin romper la conexion. | Verifique que el tamano del pad sea el diametro del taladro + 8 mil (0.2 mm). |

| Solder Mask Dam | ≥ 3 mil (0.075 mm) | Evita puentes de soldadura durante el assembly. Un dam menor puede despegarse o requerir LDI (Laser Direct Imaging). | Revise el espacio entre aperturas de mascara en el Gerber Viewer. |

| Acabado superficial | ENIG (Electroless Nickel Immersion Gold) | Mejor equilibrio entre planitud para SMDs y vida de almacenamiento. HASL puede quedar irregular para BGA de paso fino. | Especifiquelo claramente en las notas de fabricacion. |

| Definicion de stackup | "Use Vendor Standard" (si es posible) | Permitir al fabricante usar combinaciones prepreg/core en stock evita demoras por pedido de material. | Anote "Impedance controlled, vendor to adjust stackup" en las Fab Notes. |

Seguir estas reglas es especialmente importante cuando trabaja con tecnologias complejas como HDI PCB, donde el margen de error es mucho menor.

PCB Lead Time Checklist for Npi pasos de implementacion

Implementar una PCB Lead Time Checklist for Npi robusta requiere un cambio de proceso, no solo un documento. Siga esta guia de ejecucion para sincronizar su equipo de diseno con la planta de fabricacion.

Proceso de implementacion

Guia de ejecucion paso a paso

Antes de rutear trazas, contacte con su fabricante, como APTPCB, para confirmar el stackup. Solicite un "Stackup Report" basado en materiales en stock. Esto fija sus calculos de impedancia y garantiza disponibilidad inmediata de core y prepreg.

En [Turnkey Assembly](/pcba/turnkey-assembly), el PCB rara vez es el elemento con mayor lead time; suelen ser los chips. Haga un BOM scrub para detectar componentes obsoletos o sin stock. Defina alternates para pasivos en la BOM y evitar asi bloqueos de assembly.

Ejecute una revision DFM enfocada en los showstoppers: distancia drill-to-copper, slivers y acid traps. Asegurese tambien de que los footprints coinciden con las piezas fisicas (DFA) para evitar problemas de colocacion. Consulte las [DFM Guidelines](/resources/dfm-guidelines) para reglas concretas de clearance.

Envie un paquete completo: Gerbers (RS-274X), Drill file (Excellon), IPC Netlist, fichero Pick & Place, BOM y un PDF "Read Me" claro. La ambigüedad es enemiga de la velocidad. Indique de forma explicita: "No X-outs allowed" o "X-outs accepted" para la panelizacion.

PCB Lead Time Checklist for Npi solucion de problemas

Incluso con checklist, surgen problemas. Asi se solucionan los retrasos NPI mas habituales:

1. "On Hold for Eq" (Engineering Questions)

- Sintoma: recibe un correo pidiendo aclaracion sobre tamanos de taladro o lineas de impedancia.

- Causa raiz: informacion conflictiva, por ejemplo drill file de 0.2 mm mientras el Gerber mide 0.15 mm, o faltan capas de referencia.

- Fix: priorice siempre el archivo Gerber como master. Incluya una nota: "In case of conflict, Gerber data takes precedence." Use nuestro Impedance Calculator para verificar antes del envio que los anchos de traza coinciden con la impedancia objetivo.

2. Escasez de materiales

- Sintoma: la fabrica indica que el material Rogers o Panasonic especificado tiene un lead time de 3 semanas.

- Causa raiz: especificar un laminado de nicho para una placa de uso general.

- Fix: salvo que este disenando placas RF de alta frecuencia, como radar de 77 GHz, permita materiales "Equivalent". Indique: "Material: Isola 370HR or equivalent TG170 material."

3. Problemas de soldabilidad en assembly

- Sintoma: los pads no humectan bien o aparecen voids en BGA.

- Causa raiz: acabado caducado u oxidacion por almacenamiento/manipulacion inadecuados entre Fab y Assembly.

- Fix: si hay retraso entre Fab y Assembly, asegurese de que las placas vayan selladas al vacio con desecante. En NPI, se prefiere ENIG frente a OSP porque OSP tiene menor vida util y es mas sensible a la manipulacion.

6 reglas esenciales para PCB Lead Time Checklist for Npi (chuleta)

| Regla / guia | Por que importa (fisica/coste) | Valor objetivo / accion |

|---|---|---|

| Estandarice materiales | Los laminados especiales requieren pedido al proveedor y anaden dias o semanas. Los materiales en stock son inmediatos. | FR4 TG150/170 (Stock) |

| Drill-to-Copper Clearance | Un clearance ajustado arriesga perforar trazas y crear cortos. Relajarlo mejora yield y velocidad. | ≥ 8 mil (0.2 mm) |

| Defina la impedancia con claridad | La ambigüedad obliga a CAM a calcular y pedir aprobacion. Los stackups predefinidos evitan ese paso. | Incluya tabla de stackup en el Fab Drawing |

| Evite Via-in-Pad (si es posible) | VIPPO exige pasos extra de metalizado y planarizacion (POFV), anadiendo 1-2 dias. | Dog-bone fanout para BGA > 0.5 mm de pitch |

| Estrategia de panelizacion | Arrays ineficientes desperdician material y tiempo de assembly. Deje optimizar a la fab o siga las specs de assembly. | Permita panelizacion por la fab (indique tamano maximo) |

| BOM completa | La ausencia de MPNs (Manufacturer Part Numbers) detiene la compra para assembly de inmediato. | 100 % de MPN Match (sin descripciones genericas) |

FAQ

Q: Cuanto tiempo anade la tecnologia HDI al lead time de NPI?

A: HDI (High Density Interconnect) suele anadir 2-4 dias al lead time estandar. Esto se debe a los ciclos de laminacion secuencial necesarios para blind y buried vias. Un stackup 1+N+1 es mas rapido que un stackup 2+N+2.

Q: Puedo acelerar pedidos NPI a 24 horas?

A: Si, para rigid PCBs estandar de 2-6 capas con materiales estandar, son posibles turnos de 24 horas. Sin embargo, esto exige datos "perfectos" y cero retrasos por EQ. Las placas complejas o las que requieren assembly necesitaran mas tiempo.

Q: Cual es la causa mas comun de retrasos NPI?

A: La ambigüedad de datos. Informacion conflictiva entre el drill file, las capas Gerber y las notas de fabricacion obliga al CAM engineer a detener el proceso y pedir aclaraciones (EQ).

Q: Debo usar consigned parts o turnkey para NPI?

A: Para ganar velocidad, Turnkey suele ser mas rapido porque el fabricante aprovecha cadenas de suministro y stock existentes. Los consigned parts, es decir, enviar sus propios componentes, pueden introducir retrasos si los kits estan incompletos o retenidos en aduana.

Solicitar cotizacion / revision DFM para PCB Lead Time Checklist for Npi

Listo para lanzar su NPI? Envie sus datos a APTPCB para una revision DFM completa y una estimacion precisa del lead time.

Checklist para cotizacion / DFM:

- Gerber Files: formato RS-274X (todas las capas).

- Drill File: formato Excellon (ASCII).

- Fab Drawing: PDF con stackup, material y especificaciones de acabado.

- BOM: formato Excel con Manufacturer Part Numbers (para assembly).

- Pick & Place: coordenadas XY (para assembly).

- Cantidades: numero de prototipos, por ejemplo 5, 10, 50, y volumen anual estimado.

Conclusion

Dominar la PCB Lead Time Checklist for Npi significa controlar las variables que usted si puede influir. Al estandarizar materiales, validar stackups temprano y garantizar claridad de datos, transforma el proceso NPI de un cuello de botella en una ventaja competitiva. La velocidad en NPI no consiste solo en correr, sino en acertar a la primera.

Atentamente, El equipo de ingenieria de APTPCB