Los servo drives ejecutan perfiles de movimiento con precision temporal del orden de los microsegundos. Controlan la corriente del motor para seguir consignas de posicion que pueden cambiar miles de veces por segundo. La PCB debe sostener anchos de banda de control superiores a 1 kHz y, al mismo tiempo, trabajar con niveles de potencia que van desde cientos de vatios hasta decenas de kilovatios. Esta combinacion exige mucho cuidado con la integridad de senal, el layout de potencia y la gestion EMC.

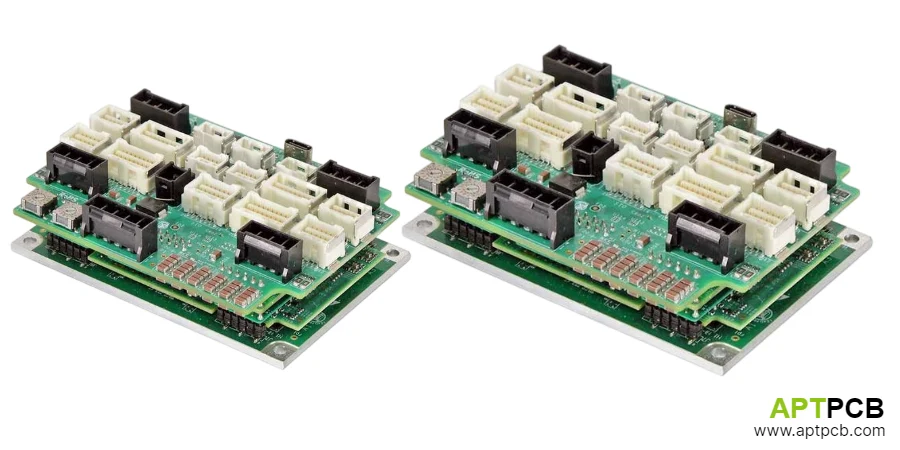

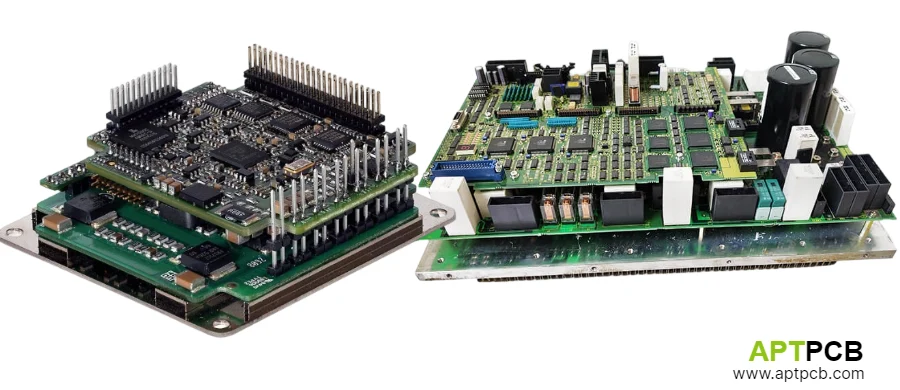

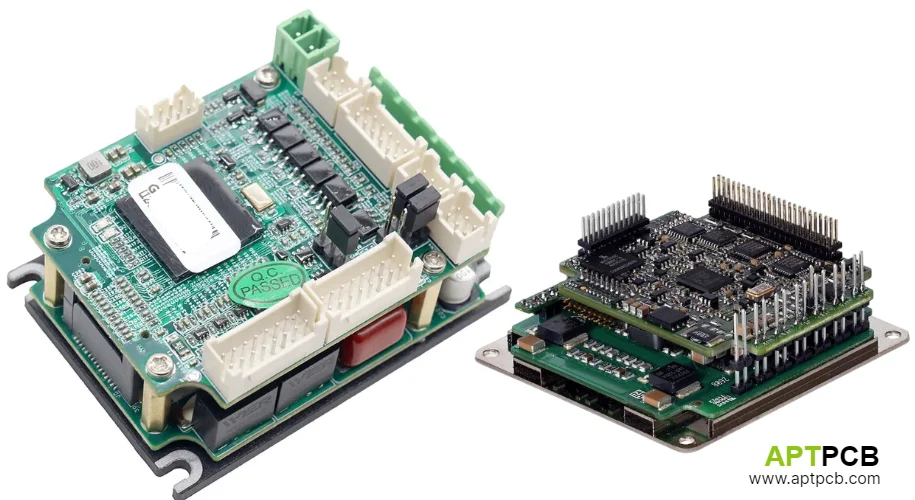

Esta guia se centra en la ingenieria de PCB que define el rendimiento de un servo drive en aplicaciones que van desde maquinaria CNC hasta equipos para manipulacion de semiconductores.

En esta guia

- Interfaces de encoder y retroalimentacion

- Implementacion del lazo de corriente

- Etapa de potencia para aplicaciones servo

- Integridad de la senal de control de posicion

- Diseno termico para cargas dinamicas

- Integracion de seguridad y seguridad funcional

Interfaces de encoder y retroalimentacion

El rendimiento de un sistema servo depende directamente de la exactitud de la realimentacion de posicion. Los encoders incrementales con millones de cuentas por vuelta, los encoders absolutos multiturno y los sensores analogicos de alta resolucion exigen interfaces PCB capaces de conservar la calidad de senal dentro del entorno industrial.

Los encoders incrementales de alta resolucion generan senales diferenciales por encima de 10 MHz cuando el movimiento es rapido. Los circuitos receptores del PCB deben capturar esas senales sin perder flancos. En un encoder de 16 bits, una sola cuenta perdida ya representa un error de posicion de 20 segundos de arco. Los receptores diferenciales con terminacion correcta ayudan a rechazar el ruido de modo comun presente en planta.

Los encoders absolutos modernos transmiten la posicion mediante protocolos serie como BiSS, EnDat o Hiperface a velocidades de hasta 10 Mbit/s. Esos datos son criticos y el drive los procesa en cada ciclo de control. Por eso, el diseno de PCB de alta velocidad debe mantener la integridad de la senal a traves de cables y barreras de aislamiento que protegen la electronica del interfaz de encoder.

Requisitos de la interfaz de encoder

- Terminacion diferencial: Los receptores RS-422 o RS-485 deben tener la terminacion de impedancia correcta justo en la entrada del PCB.

- Puesta a tierra del blindaje del cable: El blindaje del cable del encoder debe conectarse al chasis junto al conector, no cruzar la tarjeta.

- Opciones de aislamiento: Algunos sistemas requieren interfaces de encoder aisladas para evitar que los lazos de tierra afecten la precision.

- Filtrado de entrada: Los filtros RC en las entradas del encoder ayudan a evitar que el ruido de alta frecuencia se acople a los receptores.

- Calidad de alimentacion: Una alimentacion bien filtrada evita que el ruido de conmutacion altere la electronica del encoder.

- Deteccion de fallos: El hardware debe detectar perdida de senal, exceso de frecuencia y errores de comunicacion.

Implementacion del lazo de corriente

El lazo de corriente funciona a la velocidad mas alta dentro de la jerarquia de control del servo. En aplicaciones estandar suele trabajar entre 10 y 20 kHz, mientras que en drives de alto rendimiento puede superar 50 kHz. La exactitud en la medida de corriente y la latencia del control limitan directamente la banda pasante real y la precision final de posicionamiento.

En aplicaciones servo se suele preferir la medida sobre shunt por su ancho de banda y exactitud. Los amplificadores aislados para shunt deben estabilizarse dentro de la ventana de muestreo y, a la vez, rechazar los transitorios de modo comun generados por la PWM. Los requisitos tipicos rondan ±0,5 % de precision, menos de 1 μs de asentamiento y mas de 50 kV/μs de CMTI.

El controlador digital de corriente suele ejecutarse sobre DSP o FPGA con temporizacion determinista. El muestreo del ADC debe sincronizarse con la PWM para capturar valores estables. Si la medida se realiza durante las transiciones de conmutacion, el ruido introducido degrada el rendimiento del control. El layout de PCB para procesamiento de senal debe preservar la calidad analogica a lo largo de toda la cadena de adquisicion y calculo.

Elementos de diseno del lazo de corriente

- Seleccion del shunt: Los shunts de baja inductancia, por debajo de 5 nH, reducen el ringing en medidas durante transitorios de corriente.

- Ubicacion de amplificadores: Los amplificadores aislados deben colocarse cerca del shunt, mientras que sus salidas deben alejarse de la conmutacion de potencia.

- Sincronizacion de muestreo: Los disparos por hardware deben alinear el muestreo ADC con la PWM para asegurar medidas coherentes.

- Anti-aliasing: Los filtros RC por debajo de Nyquist evitan que el ruido plegado afecte al control.

- Estabilidad de referencia: La referencia de voltaje del ADC debe permanecer estable dentro del presupuesto de precision de corriente.

- Latencia digital: La latencia total desde el evento de corriente hasta la respuesta del control debe repartirse entre sensado, procesado y actualizacion PWM.

Etapa de potencia para aplicaciones servo

La etapa de potencia de un servo drive debe admitir flujo bidireccional de corriente y cambios de sentido muy rapidos durante aceleraciones y frenadas. El layout del PCB debe minimizar la inductancia para que la conmutacion siga siendo limpia y, al mismo tiempo, ofrecer caminos de corriente adecuados para un funcionamiento en cuatro cuadrantes con frenado regenerativo.

Durante la deceleracion, la energia regenerativa vuelve al bus DC y eleva su tension. Por eso, la etapa de potencia y los condensadores del bus deben soportar tanto el modo motor como el regenerativo. Los circuitos de brake chopper se activan cuando la tension del bus supera el limite seguro y disipan la energia en resistencias. Esta parte del circuito tambien necesita un layout cuidado para cargas pulsadas de alta corriente.

Los requisitos dinamicos de una aplicacion servo suelen superar a los de un VFD convencional. No es raro encontrar pendientes de corriente de 100 A/μs en sistemas muy reactivos, lo que provoca caidas de tension importantes en las inductancias parasitas. El stackup multicapa del PCB debe minimizar la inductancia del lazo de potencia y, a la vez, aportar suficiente cobre para la corriente continua.

Diseno de la etapa de potencia servo

- Operacion en cuatro cuadrantes: La etapa debe soportar funcionamiento motor y regenerativo en ambos sentidos sin zonas muertas.

- Seleccion de condensadores de bus: Se necesitan condensadores de bajo ESR para soportar tanto el ripple de PWM como el retorno de energia regenerativa.

- Layout del brake chopper: Las conexiones entre IGBT de frenado y resistencia deben ser poco inductivas y capaces de soportar disipacion pulsada elevada.

- Frecuencia de conmutacion: Una PWM mas alta, entre 10 y 20 kHz, mejora la banda pasante del lazo de corriente, pero aumenta las perdidas de conmutacion.

- Optimizacion del dead-time: El tiempo muerto debe reducirse al minimo compatible con el comportamiento seguro del IGBT.

- Proteccion por sobrecorriente: Es imprescindible una proteccion por hardware con respuesta inferior a 2 μs frente a cortocircuitos.

Integridad de la senal de control de posicion

Las consignas de posicion llegan mediante buses de campo como EtherCAT, PROFINET IRT o SERCOS, o mediante entradas analogicas como ±10 V y senales paso-direccion. La interfaz PCB debe conservar la fidelidad de esas consignas y, al mismo tiempo, sincronizarse con la estructura interna de control que ejecuta los perfiles de movimiento.

Las redes industriales de movimiento trabajan con ciclos sincronizados y precision inferior al microsegundo. EtherCAT, por ejemplo, logra sincronizacion de reloj distribuido por debajo de 1 μs mediante sellado temporal por hardware en el ESC. El PCB de interfaces de comunicacion industrial debe sostener esas exigencias de temporizacion determinista.

Las interfaces de mando analogico, como referencia de velocidad ±10 V o comandos por pulsos paso-direccion, siguen siendo habituales en retrofits y sistemas independientes. Exigen conversion ADC de alta resolucion junto con proteccion y filtrado adecuados. Las interfaces de pulsos, ademas, requieren captura hardware con capacidad suficiente para posicionamiento a alta velocidad.

Diseno de la interfaz de posicion

- Sincronizacion de red: La precision del reloj distribuido EtherCAT obliga a cuidar la seleccion del PHY y la calidad del reloj de referencia.

- Resolucion analogica: Una resolucion ADC de 14 a 16 bits es habitual para conseguir una entrada analogica con buena precision de posicion.

- Proteccion de entrada: Todas las interfaces externas deben incluir proteccion ESD y frente a sobretension.

- Requisitos de aislamiento: Dependiendo de la arquitectura, las redes de movimiento pueden necesitar interfaces aisladas.

- Latencia de actualizacion: La especificacion entre comando y accion marca los requisitos tanto de interfaz como de procesado.

- Especificacion de jitter: El jitter en la actualizacion de posicion afecta directamente a la suavidad de trayectorias multieje.

Diseno termico para cargas dinamicas

Las cargas servo cambian dinamicamente a medida que la maquina ejecuta perfiles de movimiento. Las corrientes pico durante aceleracion pueden ser de tres a cinco veces el valor continuo, seguidas por fases de mantenimiento o regeneracion. El diseno termico debe manejar tanto la disipacion en estado estable como el calentamiento transitorio sin superar los limites de temperatura de los componentes.

La temperatura de union de los semiconductores de potencia varia con la carga. Los ciclos termicos repetidos acaban generando fatiga en uniones de soldadura y degradacion de bond wires. La interfaz termica entre PCB, dispositivos y disipador afecta tanto la temperatura estable como la impedancia termica transitoria. Cuanto menor sea esa impedancia, menor sera la oscilacion termica en un ciclo dado.

El diseno de PCB para gestion termica en servo drives debe considerar la naturaleza intermitente de estas cargas. Componentes dimensionados solo para disipacion continua pueden sobrecalentarse durante aceleraciones prolongadas, mientras que elementos elegidos solo por pico pueden resultar innecesariamente costosos en ciclos bajos.

Diseno termico para cargas de movimiento

- Presupuesto de temperatura de union: Hay que disenar para el perfil de movimiento mas exigente, no solo para la condicion continua o de pico.

- Interfaz termica: El montaje entre semiconductor de potencia y disipador debe buscar una resistencia termica inferior a 0,3 °C/W.

- Peso de cobre: El cobre pesado de 3 a 6 oz en zonas de potencia mejora la respuesta termica transitoria.

- Sensado de temperatura: Varios sensores NTC a lo largo del camino termico ayudan a vigilar mejor el comportamiento real.

- Proteccion termica: La proteccion I²t limita la acumulacion de calor durante sobrecargas repetitivas.

- Dependencia del flujo de aire: El diseno termico debe documentar el flujo de aire requerido y el derating en condiciones de ventilacion reducida.

Integracion de seguridad y seguridad funcional

Los sistemas de movimiento incorporan funciones de seguridad funcional que requieren implementaciones PCB especificas. Safe Torque Off, Safe Stop 1 y otras funciones deben cumplir requisitos SIL2 o SIL3 conforme a IEC 61800-5-2 y a los marcos de seguridad de maquina aplicables.

La implementacion de STO exige una monitorizacion redundante de las rutas de deshabilitacion del gate drive, con cobertura diagnostica para detectar fallos que conduzcan a un estado peligroso. La PCB debe ofrecer entradas seguras e aisladas junto con circuitos adecuados de temporizacion y diagnostico. Los enclavamientos hardware deben garantizar que la etapa de potencia se inhibe realmente, con independencia del estado del software.

Las funciones de velocidad segura y direccion segura necesitan procesamiento redundante del encoder con circuitos comparadores capaces de detectar desacuerdo entre sensores. Estas funciones requieren un PCB industrial robusto que preserve la integridad de la seguridad frente a condiciones ambientales y envejecimiento de componentes.

Requisitos de integracion de seguridad

- Aislamiento de entradas STO: Las entradas deben estar aisladas y admitir pruebas por pulsos para la cobertura diagnostica.

- Monitorizacion redundante: Los parametros criticos deben vigilarse por doble canal con verificacion cruzada.

- Cobertura diagnostica: El hardware debe detectar fallos que puedan comprometer la funcion de seguridad.

- Respuesta a fallos: La electronica debe imponer un estado seguro independientemente del software o del estado de comunicacion.

- Encoder seguro: Para funciones basadas en posicion se requieren canales de encoder redundantes o encoders absolutos con certificacion de seguridad.

- Documentacion: La documentacion de PCB debe servir como evidencia para la certificacion de funciones de seguridad.

Resumen

El diseno de PCB para servo drive integra interfaces de realimentacion de gran ancho de banda, lazos de corriente muy rapidos, gestion dinamica de potencia y seguridad funcional en sistemas que alcanzan precision de movimiento a nivel de microsegundos. La mezcla de retos de electronica de potencia con exigencias analogicas de alta precision crea restricciones que obligan a una ingenieria coordinada entre integridad de senal, termica, EMC y seguridad. El resultado depende de comprender como interactuan todos esos requisitos y como afectan al rendimiento y a la fiabilidad del movimiento.