Los decodificadores y los dispositivos de medios de transmisión representan una de las categorías de electrónica de consumo de mayor volumen, con decenas de millones de unidades enviadas anualmente por los principales fabricantes. El desafío del diseño de PCB se centra en lograr un rendimiento adecuado para la transmisión de video 4K y los juegos, al tiempo que se cumplen objetivos de costos agresivos: los precios minoristas típicos por debajo de $50 requieren la optimización de BOM en todos los niveles.

Esta guía examina los requisitos de diseño de PCB del decodificador: implementación de SoC de transmisión con funcionalidad integrada, optimización de la calidad de la señal de salida HDMI, integración de conectividad WiFi y Bluetooth, logro de objetivos térmicos dentro de gabinetes compactos sin ventilador y estrategias de fabricación que equilibran la calidad con la optimización de costos de volumen.

En esta guía

- Implementación de SoC de transmisión e interfaz de memoria

- Diseño de salida HDMI para calidad de video 4K

- Integración de antena WiFi y Bluetooth

- Gestión térmica en gabinetes sin ventilador

- Optimización de fabricación de alto volumen

- Pruebas y garantía de calidad para la producción en volumen

Implementación de SoC de transmisión e interfaz de memoria

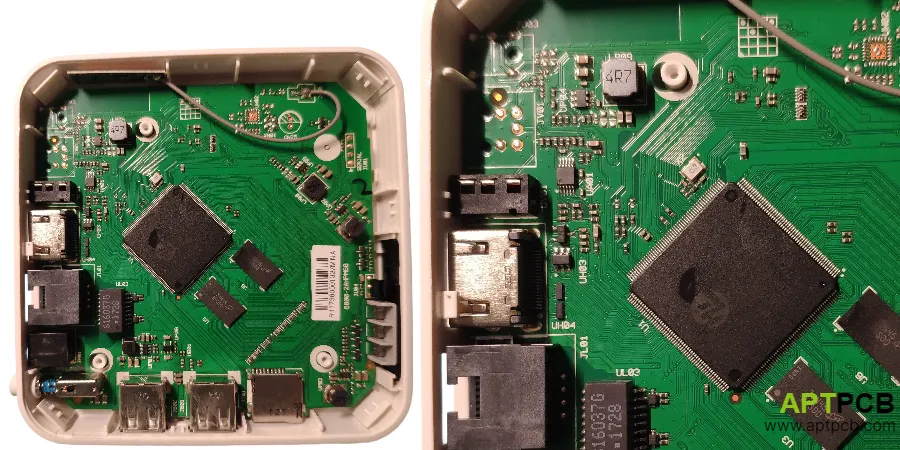

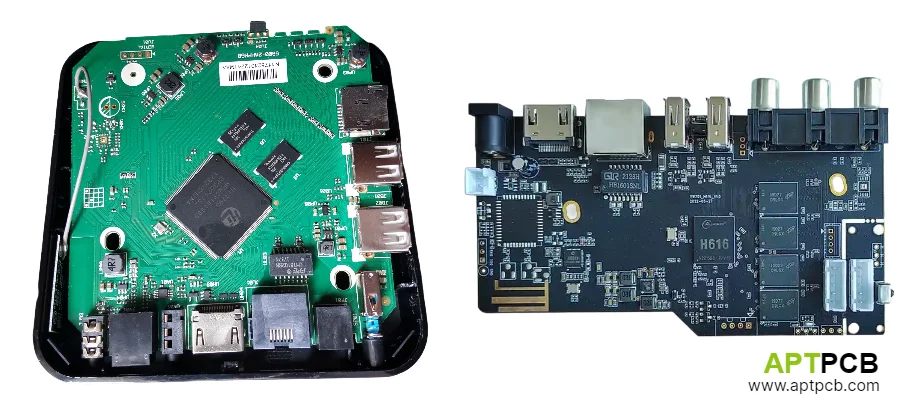

Los SoC de decodificadores modernos integran núcleos de CPU, GPU, decodificador de video, transmisor HDMI, USB y, a menudo, WiFi/Bluetooth en soluciones de un solo chip de proveedores como Amlogic, Realtek y Rockchip. Estos dispositivos altamente integrados simplifican el diseño de la placa, pero requieren una atención cuidadosa al enrutamiento de la interfaz de memoria y la entrega de energía para lograr una operación confiable a través de la variación de producción.

Las configuraciones de memoria suelen oscilar entre 1-4 GB DDR3/DDR4 en diseños sensibles a los costos y LPDDR4 en dispositivos premium. La interfaz de memoria a menudo determina los requisitos de recuento de capas de PCB: DDR4 a velocidades superiores a 2400 MT/s requiere una disciplina de enrutamiento que puede exceder la capacidad de 4 capas, mientras que las configuraciones DDR3 de menor velocidad pueden lograr un rendimiento adecuado con acumulaciones más simples.

Implementación de SoC y memoria

- Consideraciones del paquete: Los SoC de decodificadores suelen utilizar BGA de paso de 0.65-0.8 mm con 300-600 pines; el abanico estándar de vía en almohadilla o hueso de perro logra el enrutamiento sin HDI.

- Topología de memoria: La mayoría de los SoC utilizan una configuración de memoria de rango único; la topología de punto a punto desde el SoC hasta un solo IC de memoria simplifica el enrutamiento en comparación con los diseños de rango múltiple.

- Selección de velocidad: DDR4-2133 o DDR4-2400 proporciona un ancho de banda adecuado para la transmisión de 4K a un costo moderado; las velocidades más altas agregan costos sin un beneficio de rendimiento perceptible para casos de uso típicos.

- Coincidencia de longitud: La interfaz DDR requiere un enrutamiento coincidente: señales DQ dentro del carril de bytes ± 5 mm; DQS a DQ ± 2 mm; dirección/comando al reloj ± 25 mm según la especificación del SoC.

- Requisitos de impedancia: Objetivos de impedancia típicos de DDR4: 40 Ω para datos/dirección de un solo extremo, 80 Ω diferencial para reloj; tolerancia de ± 10% alcanzable con procesos estándar.

- Terminación: La terminación en matriz (ODT) maneja la mayoría de los requisitos de terminación; la terminación externa rara vez es necesaria para configuraciones de rango único.

Las interfaces de memoria simples a menudo tienen éxito con la construcción de PCB multicapa utilizando acumulaciones estándar de 4-6 capas sin requisitos avanzados de HDI.

Diseño de salida HDMI para calidad de video 4K

La calidad de salida HDMI afecta directamente la percepción del usuario sobre la calidad del dispositivo: los artefactos visibles, las bandas de color o las interrupciones de audio sugieren una calidad de dispositivo inferior, independientemente del rendimiento real de la transmisión. Los decodificadores suelen emitir HDMI 2.0 (18 Gbps, compatible con 4K60 HDR) desde el transmisor integrado en el SoC, lo que requiere un enrutamiento de PCB que mantenga la integridad de la señal desde el silicio hasta el conector.

La presión de optimización de costos en el diseño del decodificador crea la tentación de minimizar la inversión en enrutamiento HDMI: trazas cortas, materiales estándar, tolerancias de impedancia relajadas. Dentro de los límites, estas simplificaciones funcionan; si se presiona demasiado, resultan en un rendimiento HDMI marginal que causa problemas intermitentes con ciertos televisores o longitudes de cable.

Enrutamiento de salida HDMI

- Longitud de traza: Mantenga las trazas HDMI por debajo de 75 mm desde el SoC hasta el conector; las trazas más cortas toleran mejor la variación del proceso y reducen la pérdida de alta frecuencia.

- Objetivo de impedancia: Impedancia diferencial de 100 Ω ± 15% suficiente para HDMI 2.0 en longitudes de traza moderadas; tolerancia más estricta para trazas más largas o HDMI 2.1.

- Selección de capa: Enrutamiento de microcinta en la capa externa aceptable para trazas cortas con referencia de tierra adecuada; la línea de banda proporciona una mejor contención de EMI.

- Calidad del conector: La selección del conector HDMI afecta tanto la integridad de la señal como la confiabilidad mecánica; la optimización de costos no debe sacrificar la calidad del conector: las fallas de campo debido a conectores deficientes superan los ahorros.

- Protección ESD: Los diodos TVS en el conector HDMI protegen contra descargas estáticas; seleccione dispositivos de baja capacitancia (<0.5pF) para minimizar la degradación de la señal.

- Acoplamiento de CA: La especificación HDMI requiere acoplamiento de CA en carriles de datos; condensadores de 100 nF en tamaño 0402 colocados cerca de los pines de salida del SoC.

El enrutamiento HDMI para HDMI 2.0 estándar generalmente tiene éxito con una disciplina de diseño básica sin requerir técnicas especializadas de alta velocidad, pero la verificación con el cumplimiento de las especificaciones garantiza un funcionamiento confiable.

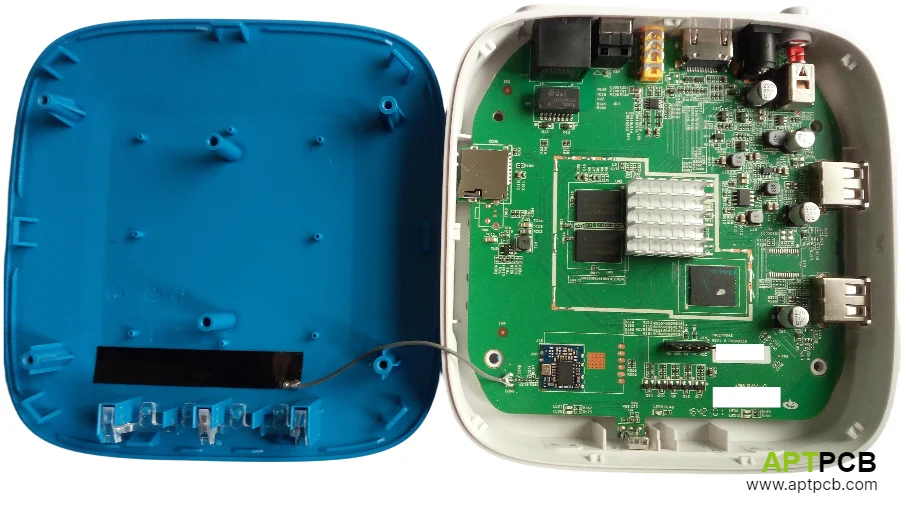

Integración de antena WiFi y Bluetooth

La conectividad WiFi es esencial para los dispositivos de transmisión: el rendimiento afecta directamente la experiencia del usuario a través del almacenamiento en búfer, la adaptación de la calidad y la confiabilidad de la conexión. La mayoría de los diseños de decodificadores utilizan módulos WiFi integrados (SoC con conexión inalámbrica incorporada o SoC WiFi separado) con antenas integradas, lo que requiere un diseño de RF cuidadoso y la colocación de la antena dentro de gabinetes compactos.

El rendimiento de la antena en gabinetes pequeños depende en gran medida del diseño del plano de tierra, las regiones de exclusión y las propiedades del material del gabinete. Los gabinetes de metal (comunes en diseños premium) requieren antenas externas o aperturas cuidadosamente diseñadas para la radiación de la antena, mientras que los gabinetes de plástico permiten antenas internas con un diseño de espacio libre adecuado.

Consideraciones de integración inalámbrica

- Selección de módulo: El WiFi integrado (SoC con radio incorporada) minimiza el costo pero limita la flexibilidad; los módulos WiFi discretos ofrecen un rendimiento certificado y múltiples opciones de proveedores.

- Tipos de antena: Las antenas impresas en PCB minimizan el costo pero requieren optimización del plano de tierra; las antenas de chip proporcionan un rendimiento constante en un área más pequeña; antenas externas para gabinetes de metal.

- 2.4 GHz vs. 5 GHz: Los diseños de doble banda requieren una antena de doble banda o antenas separadas; la banda única de 5 GHz proporciona un mejor rendimiento de transmisión en entornos congestionados.

- Espacio libre del plano de tierra: Las antenas de PCB requieren una región libre de tierra que se extienda desde el elemento de la antena; las dimensiones dependen de la frecuencia y el tipo de antena, generalmente de 10 a 15 mm para antenas de chip.

- Enrutamiento de traza de RF: Microcinta de 50 Ω desde IC inalámbrico a antena; mantenga las trazas cortas y evite las vías en la ruta de RF; impedancia controlada esencial para la adaptación de la antena.

- Efectos del gabinete: Los materiales del gabinete de plástico afectan la sintonización de la antena; prototipo con material del gabinete de producción para una evaluación precisa del rendimiento.

La optimización del rendimiento inalámbrico se beneficia de la experiencia en diseño de PCB de antena y la capacidad de medición de RF para sintonización y verificación.

Gestión térmica en gabinetes sin ventilador

La preferencia del consumidor por un funcionamiento silencioso impulsa los diseños de decodificadores sin ventilador, lo que requiere que la PCB y el gabinete disipen la potencia del SoC (generalmente 3-8 W durante la reproducción 4K) a través de la conducción y la convección natural. Los gabinetes compactos (a menudo de menos de 150 mm × 100 mm × 25 mm) limitan el área de dispersión de calor, por lo que el diseño térmico es crítico para un rendimiento sostenido sin estrangulamiento.

La PCB sirve como el principal disipador de calor en la mayoría de los diseños térmicos de decodificadores. El calor se conduce desde el SoC a través de vías térmicas hacia las capas de cobre, se extiende lateralmente a través de la placa y se transfiere al gabinete a través de almohadillas térmicas o contacto directo. El área de superficie del gabinete luego disipa el calor a través de la convección y la radiación.

Estrategias de diseño térmico

- Matriz de vías térmicas: Matriz de vías densa (taladro de 0.3 mm, paso de 0.5 mm) debajo del paquete SoC conduce el calor a las capas internas y la superficie inferior; se prefieren las vías llenas para evitar la absorción de soldadura.

- Cobertura de cobre: Maximice el vertido de cobre en todas las capas debajo y alrededor del SoC; los planos de tierra cumplen una doble función para el retorno eléctrico y la dispersión térmica.

- Disipador de calor superior: Los esparcidores de aluminio o disipadores de calor conectados a la superficie superior del SoC proporcionan una ruta térmica adicional; el material de interfaz térmica cierra la brecha entre el componente y el esparcidor.

- Ruta térmica inferior: Transferencia de calor al fondo del gabinete a través de almohadillas térmicas o contacto directo con la placa; requiere un área de cobre plana sin vías ni intrusión de componentes.

- Colocación de componentes: Mantenga los componentes generadores de calor (reguladores, circuitos integrados inalámbricos) lejos del SoC para evitar la interacción térmica; distribuya las fuentes de calor en el área de la placa.

- Diseño del gabinete: La conductividad del material del gabinete afecta el rendimiento térmico del sistema; los gabinetes de aluminio proporcionan una excelente dispersión del calor; los gabinetes de plástico dependen más de la convección.

La simulación térmica durante la fase de diseño identifica puntos calientes y valida la idoneidad de la solución térmica antes de la creación de prototipos físicos, ahorrando tiempo de desarrollo y ciclos de iteración.

Optimización de fabricación de alto volumen

Los volúmenes de decodificadores, a menudo de cientos de miles a millones de unidades al año, justifican inversiones en optimización de fabricación que los productos de menor volumen no pueden soportar. Las decisiones de diseño de PCB afectan directamente el costo de fabricación a través de la utilización del panel, el recuento de capas, la selección de materiales y la cobertura de prueba. Cada centavo ahorrado en el costo de PCB multiplicado por el volumen se vuelve significativo.

La optimización de costos requiere equilibrar múltiples factores: la reducción del recuento de capas ahorra costos de material pero puede requerir un enrutamiento más complejo o un tamaño de placa más grande; los materiales estándar cuestan menos pero pueden limitar el rendimiento; las placas más pequeñas mejoran la utilización del panel pero limitan la colocación de componentes y la dispersión térmica.

Factores de costo de fabricación

- Recuento de capas: Diseños de 4 capas significativamente más baratos que los de 6 capas; 2 capas posibles para los diseños más simples: cada par de capas agrega ~ 20-30% al costo de la placa.

- Selección de materiales: FR-4 estándar (Tg 130-150 °C) se adapta a la mayoría de las aplicaciones; materiales con mayor Tg solo si los perfiles de reflujo de ensamblaje lo requieren; de lo contrario, no hay beneficio de rendimiento.

- Optimización del tamaño de la placa: Las placas más pequeñas mejoran la utilización del panel; estandarice las dimensiones en las variantes del producto para compartir la optimización del diseño del panel.

- Estructura de vías: Vías de orificio pasante solamente (sin ciegas / enterradas) para diseños sensibles a los costos; HDI agrega un costo significativo: reserve para enrutamiento de paso fino inevitable.

- Acabado de superficie: HASL de menor costo para ensamblaje estándar; ENIG / OSP para requisitos de paso fino: especifique adecuadamente en lugar de especificar en exceso.

- Diseño de panel: Trabaje con el fabricante en el diseño óptimo del panel; los rieles de borde, la puntuación frente al enrutamiento y la colocación del cupón de prueba afectan la utilización y el manejo.

Las asociaciones de fabricación por volumen a través de servicios de producción masiva de PCB permiten economías de escala que reducen los costos por unidad mientras mantienen los estándares de calidad.

Pruebas y garantía de calidad para la producción en volumen

La producción de decodificadores de alto volumen requiere estrategias de prueba eficientes que detecten defectos sin convertirse en cuellos de botella de costos o rendimiento. El enfoque de prueba debe equilibrar la detección de defectos con el costo de la prueba: las pruebas exhaustivas que detectan todos los defectos posibles pero agregan un costo significativo por unidad pueden no optimizar el costo total (producción más garantía).

Las estrategias de prueba efectivas combinan pruebas en circuito (ICT) o sonda volante para verificación eléctrica, pruebas funcionales para verificación operativa e inspección óptica automatizada (AOI) para detección de defectos de ensamblaje. Los principios de diseño para prueba (DFT) incorporados durante el diseño de PCB permiten una implementación de prueba eficiente.

Componentes de la estrategia de prueba

- Prueba en circuito (ICT): Las pruebas basadas en accesorios proporcionan una verificación eléctrica rápida y completa; requiere acceso a la almohadilla de prueba: diseñe puntos de prueba en ubicaciones apropiadas.

- Sonda volante: Alternativa sin accesorios para volúmenes más bajos o variantes de placa; más lento que ICT pero elimina el costo de los accesorios y el tiempo de entrega.

- Prueba funcional: La prueba de encendido verifica el funcionamiento; prueba de salida HDMI, prueba de conexión WiFi, verificación de reproducción de video confirman la funcionalidad del sistema.

- Inspección óptica automatizada: AOI verifica la calidad de la unión de soldadura, la presencia/orientación de los componentes; detecta defectos de ensamblaje que las pruebas eléctricas podrían pasar por alto.

- Compensaciones de cobertura de prueba: Cobertura de nodo del 100% a menudo poco práctica; priorice las redes de alto riesgo (potencia, señales críticas) y acepte una cobertura reducida en áreas de bajo riesgo.

- Seguimiento de defectos: El análisis estadístico de fallas de prueba identifica problemas de proceso; la retroalimentación de bucle cerrado mejora tanto los procesos de ensamblaje como de prueba.

Los sistemas integrales de prueba y calidad garantizan la calidad de la producción al tiempo que optimizan la eficiencia de la prueba para la economía de fabricación de alto volumen.

Resumen técnico

El diseño de PCB de decodificador ejemplifica el desafío de lograr un rendimiento adecuado dentro de restricciones de costos agresivas: los volúmenes se miden en millones de unidades, pero los precios minoristas inferiores a $50 requieren optimización en todos los niveles. El éxito requiere hacer las compensaciones apropiadas: simplificado donde los márgenes de rendimiento lo permiten, diseño disciplinado donde es crítico (salida HDMI, rendimiento inalámbrico, gestión térmica).

Las decisiones clave en el desarrollo de decodificadores incluyen el recuento de capas (4 capas frente a 6 capas según la complejidad del enrutamiento), la selección de materiales (estándar frente a FR-4 mejorado según los requisitos térmicos y de rendimiento), el enfoque de integración inalámbrica (integrado frente a módulo, tipo de antena) y la solución térmica (papel del diseño de la placa en la gestión térmica del sistema).

La selección de socios de fabricación debe enfatizar las capacidades de alto volumen, la competitividad de costos y los sistemas de calidad: los volúmenes de decodificadores justifican la optimización de proveedores, pero los costos de garantía por problemas de calidad eliminan rápidamente los ahorros de fabricación. La participación temprana permite la optimización del diseño para la fabricación que beneficia tanto a la calidad como al costo.