Las placas principales de Smart TV integran procesamiento de aplicaciones, escalado y procesamiento de video, multiples interfaces de alta velocidad como HDMI, USB y Ethernet, conectividad inalambrica y sistemas de audio en tarjetas que deben cumplir objetivos de costo muy agresivos sin sacrificar una experiencia de visionado premium. Los retos de diseno de PCB van desde interfaces HDMI 2.1 de velocidad extremadamente alta, con 48 Gbps agregados, hasta interfaces para paneles grandes y la integracion de la alimentacion.

Esta guia aborda los puntos especificamente ligados al PCB en un Smart TV: la particion entre placa principal y T-CON, los requisitos de enrutamiento del SoC de video, la integridad de senal de HDMI 2.1, el diseno de la interfaz del panel, la arquitectura de alimentacion y el equilibrio entre calidad y optimizacion de costos en fabricacion que resulta esencial para los productos de television.

Design Checklist (Fast Pass)

- Particionar pronto: definir placa principal vs. T-CON vs. placa de fuente y fijar temprano la interconexion y los conectores.

- Colocar HDMI cerca: mantener cortas las rutas HDMI 2.1 FRL; prever desde el inicio huellas para ESD, CMC y retimer.

- Tratar DDR como un sistema: stackup, impedancia, igualacion de longitudes, planos de referencia y caminos de retorno deben resolverse en conjunto.

- Disenar PDN y termica a la vez: cobre, arreglos de vias y difusion termica hacia el chasis forman parte real del diseno de potencia.

- Aplicar DFM para costo: evitar HDI donde no haga falta; optimizar utilizacion de panel y acceso a prueba.

In This Guide

- Arquitectura de la placa de TV: particion entre placa principal y T-CON

- Requisitos de enrutamiento del SoC de procesamiento de video

- Implementacion de la interfaz de alta velocidad HDMI 2.1

- Diseno de la interfaz de temporizacion del panel

- Integracion de la fuente de alimentacion y consideraciones termicas

- Fabricacion optimizada en costo para productos de television

TV Board Architecture: Main Board and T-CON Partitioning

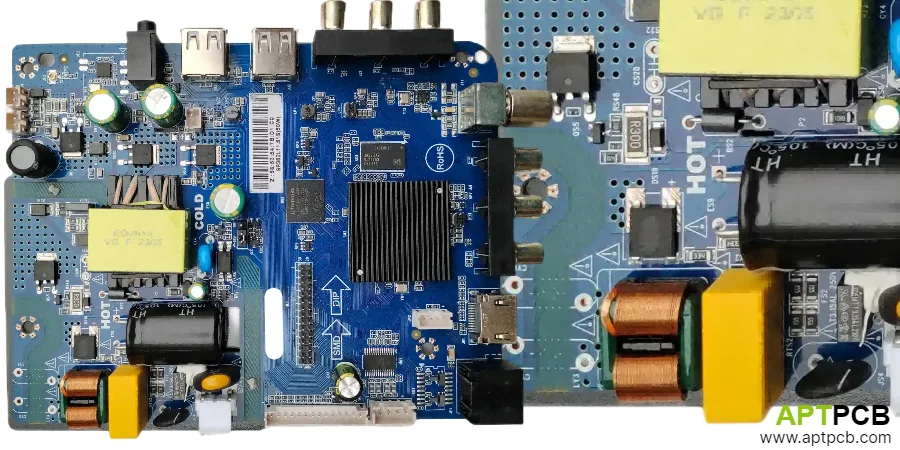

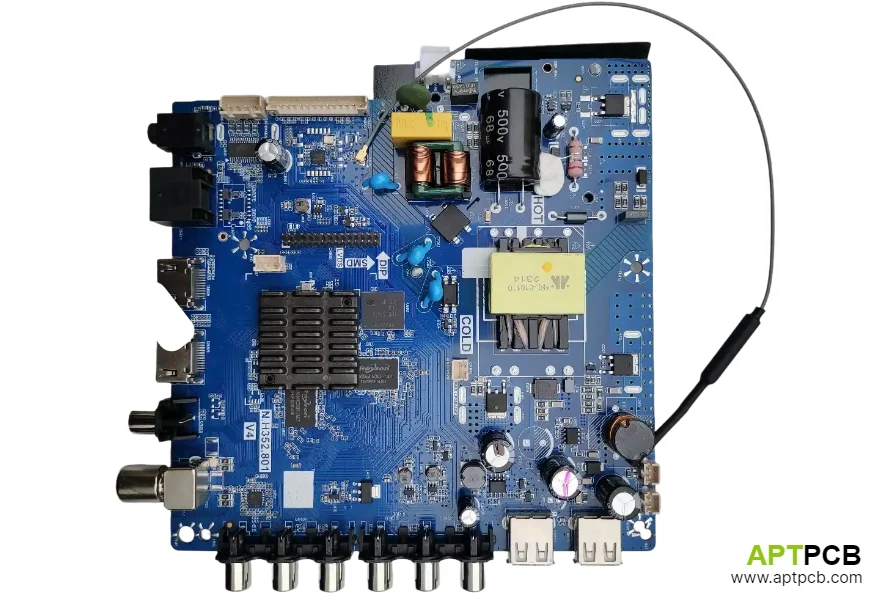

La electronica de un Smart TV suele dividirse entre varios PCB: la placa principal se encarga del procesamiento de aplicaciones, la conectividad y la entrada y procesamiento de video; la placa T-CON, timing controller, gestiona el manejo del panel y la optimizacion de imagen; y la placa de alimentacion suministra varios rieles de voltaje. Esta particion responde tanto a requisitos funcionales como a consideraciones de cadena de suministro, porque distintos paneles usan distintos T-CON, mientras que las placas principales suelen estandarizarse entre varias familias de producto.

La interfaz entre la placa principal y la T-CON transporta video ya completamente procesado a resoluciones de hasta 8K. Eso obliga a usar interfaces paralelas de ancho de banda extremadamente alto, con LVDS requiriendo decenas de pares, o protocolos serializados como V-by-One o eDP, que reducen el numero de conductores pero exigen integridad de senal de varios gigabits. Esta interfaz entre placas suele marcar el techo de rendimiento de video del sistema.

Board Partitioning Considerations

- Alcance de la placa principal: SoC, memoria, receptores HDMI, interfaces USB y Ethernet, modulos WiFi y Bluetooth, procesamiento de audio y conexiones hacia T-CON y placas de potencia.

- Nivel de integracion de T-CON: Algunos paneles integran el T-CON dentro del propio panel y otros utilizan una placa T-CON separada; eso modifica de forma directa los requisitos de interfaz del mainboard.

- Seleccion de interfaz: La especificacion del panel dicta la decision. Muchos disenos 4K60 usan V-by-One HS con unas 8 lanes en el rango de 3 a 4 Gbps por lane; 8K suele requerir mas lanes, tasas mas altas u otra interfaz.

- Tipos de conectores: Las interfaces de alta velocidad dependen de conectores especializados que mantengan la adaptacion de impedancia; los cables planos limitan el ancho de banda y exigen mucho cuidado de diseno.

- Distribucion de potencia: La placa principal puede alimentar la T-CON, aumentando la exigencia de corriente sobre el propio mainboard, o la T-CON puede recibir energia directamente desde la fuente.

- Disposicion fisica: La placa principal se monta normalmente en la zona inferior trasera de la pantalla; las restricciones termicas exigen separacion respecto al panel y caminos razonables de ventilacion.

Comprender la arquitectura del sistema permite tomar decisiones de particion PCB que afectan de forma directa tanto al rendimiento electrico como a la eficiencia de fabricacion.

Video Processing SoC Routing Requirements

Los SoC de Smart TV integran mucha complejidad: procesadores de aplicaciones quad-core u octa-core, decodificadores de video dedicados para multiples codecs en 4K u 8K, motores de display con escalado y mejora de imagen, y numerosas interfaces. Estos dispositivos altamente integrados suelen venir en encapsulados BGA grandes, muchas veces de 500 a mas de 1000 pines, con paso fino de 0,4 a 0,65 mm. Por eso el enrutamiento debe equilibrar rendimiento y fabricabilidad.

Las interfaces de memoria plantean retos especialmente delicados. DDR4 o LPDDR4/5 operan a velocidades que requieren igualacion de longitudes e impedancia controlada con mucho rigor. A diferencia de los smartphones, donde la memoria puede ir en package-on-package, en televisores el SoC suele usar memoria discreta, de modo que el problema completo de integridad de senal se resuelve a nivel de placa.

SoC Routing Guidelines

- Estrategia de fanout BGA: Los BGA de paso fino requieren via-in-pad o fanout tipo dog-bone; las vias pasantes limitan los canales de enrutamiento, por lo que las blind vias pueden ser razonables en paquetes densos.

- Enrutamiento de memoria: DDR4 a 2666-3200 MT/s exige igualacion dentro de cada byte lane de ±5 mm, ajuste DQS a DQ de ±10 mm y una impedancia consistente.

- Requisitos de planos de referencia: Las senales de memoria y de alta velocidad necesitan planos de referencia continuos; hay que evitar pistas de potencia o vias en zonas de plano bajo senales criticas.

- Estrategia de desacoplo: Los pines de alimentacion del SoC necesitan desacoplo local, por ejemplo 100 nF por cada grupo de pines, mas capacitancia bulk de 10 a 100 uF cerca. Los capacitores deben quedar tan proximos a los pines como el enrutamiento lo permita.

- Acceso JTAG y depuracion: Las interfaces de debug como JTAG o UART deben seguir accesibles tanto para desarrollo como para prueba de produccion; los puntos de prueba o headers deben ubicarse en consecuencia.

- Diseno termico: La disipacion del SoC, normalmente entre 5 y 15 W, exige vias termicas bajo el encapsulado y suficiente expansion de cobre hacia puntos de montaje del disipador o del chasis.

El enrutamiento del SoC de video se beneficia de tecnicas de PCB de alta velocidad para que las interfaces de memoria y display alcancen las margenes de rendimiento necesarias.

HDMI 2.1 High-Speed Interface Implementation

HDMI 2.1 es una de las especificaciones de interfaz de consumo mas exigentes. Con 12 Gbps por lane en cuatro lanes de datos, es decir 48 Gbps agregados, permite 8K a 60 Hz o 4K a 120 Hz con HDR. El enrutamiento entre el receptor HDMI y el conector debe preservar la integridad de senal a frecuencias donde la longitud de onda ya se aproxima a la longitud fisica de las pistas, por lo que el diseno como linea de transmision deja de ser opcional.

Las versiones anteriores, HDMI 1.4 y 2.0, con hasta 18 Gbps agregados, usaban senalizacion diferencial con terminacion en origen y tolerancias de impedancia mas moderadas. HDMI 2.1 FRL, Fixed Rate Link, eleva mucho la exigencia: 100 ohmios diferenciales (±10%), emparejamiento estrecho de longitudes dentro de cada par diferencial y control de insertion loss y return loss a lo largo de todo el canal, es decir conector, PCB y cable.

HDMI 2.1 Routing Requirements

- Control de impedancia: 100 ohmios diferenciales ±10%; los pares diferenciales fuertemente acoplados reducen EMI y mantienen el rechazo de modo comun.

- Perdida de canal: A 12 Gbps por lane, el margen de perdida se consume muy rapido. Conviene mantener pistas cortas; si no es posible, evaluar laminados de baja perdida y/o un redriver o retimer.

- Restricciones de longitud: Mantener las pistas HDMI tan cortas como sea practico; por debajo de 50 mm se minimizan perdida y skew acumulado, por eso importa colocar el conector cerca del receptor.

- Seleccion de capa: Enrutar HDMI en capas adyacentes a planos de tierra solidos; el microstrip en capas externas es valido si el EMI esta controlado; la stripline ofrece mejor apantallamiento.

- Transiciones por via: Evitarlas siempre que se pueda. Cuando sean inevitables, minimizar stubs, por ejemplo con backdrill donde tenga sentido, y mantener continuidad en los planos de referencia.

- Proteccion ESD: Los puertos HDMI requieren proteccion ESD. La posicion del dispositivo afecta de forma directa a la integridad de senal, por lo que deben usarse TVS de baja capacitancia, por debajo de 0,3 pF, ubicados junto al conector.

La implementacion de HDMI 2.1 puede requerir simulacion de integridad de senal para confirmar que el enrutamiento mantiene los margenes de cumplimiento, sobre todo cuando las trazas son largas o se trabaja con FR-4 estandar.

Panel Timing Interface Design

La interfaz entre la placa principal, o la T-CON, y el panel LCD u OLED transporta datos de video a velocidades dictadas por el pixel clock y la profundidad de color. Un panel 4K a 60 Hz con color de 10 bits requiere aproximadamente 17 Gbps de datos de video, entregados a traves de LVDS, V-by-One o interfaces propietarias segun el fabricante del panel y la resolucion.

V-by-One HS domina las implementaciones actuales de TV 4K. Usa menos lanes que LVDS, normalmente 8 pares frente a 16-32 pares, pero a velocidades mas altas, tipicamente de 3,6 a 4,0 Gbps por lane. La reduccion de lanes simplifica el enrutamiento, pero aumenta la exigencia de integridad de senal por cada lane. Las conexiones flex hacia el panel introducen discontinuidades de impedancia que deben gestionarse con el conector adecuado y un diseno de terminacion bien resuelto en el PCB.

Panel Interface Implementation

- Seleccion de protocolo: La especificacion del panel define la interfaz. V-by-One HS es habitual en la mayoria de paneles 4K; LVDS sigue siendo comun en resoluciones menores; algunos paneles 8K emplean interfaces propietarias de alta velocidad.

- Configuracion de lanes: V-by-One HS suele utilizar 8 lanes para 4K 60 Hz a 10 bits; el numero escala con resolucion, tasa de refresco y profundidad de color.

- Interfaz del conector: Los conectores del panel deben mantener la adaptacion de impedancia; el flex entre placa y panel introduce perdida y skew que afectan la tasa de bits maxima alcanzable.

- Reloj de referencia: Las interfaces de panel requieren referencias de reloj estables; la seleccion de cristal u oscilador, el filtrado de la alimentacion y el aislamiento del enrutamiento afectan el jitter.

- Diseno de terminacion: La terminacion on-chip es lo normal en receptores V-by-One; aun asi, hay que verificar la terminacion requerida por la entrada del panel y ajustar la impedancia de salida de la fuente.

- Consideraciones EMI: Las senales del panel pueden radiarse desde los cables flex; una buena puesta a tierra del conector, blindaje del cable y separacion respecto de circuitos sensibles reducen el impacto EMI.

El diseno de la interfaz del panel requiere coordinacion estrecha con el proveedor del panel para confirmar timing, niveles de tension y compatibilidad de conectores.

Power Supply Integration and Thermal Considerations

Las placas principales de Smart TV suelen recibir 5 V o 12 V desde la fuente y generar localmente los rieles necesarios para el SoC, por lo general 0,9 a 1,1 V para el nucleo y otras tensiones de I/O, para la memoria, en torno a 1,2 V en DDR4 o LPDDR4, y para otros subsistemas. La red de distribucion de potencia debe soportar los transitorios de corriente del SoC mientras mantiene la regulacion de tension dentro de margenes ajustados, normalmente ±3 % en los rieles de core.

La gestion termica en una placa principal de TV difiere de la de un dispositivo portatil. El area mayor de la tarjeta ayuda a expandir el calor, pero el chasis cerrado y la preferencia por funcionamiento sin ventilador limitan la refrigeracion. Por ello el PCB actua tanto como sustrato mecanico como primer dispersor termico, derivando el calor al chasis metalico mediante thermal interface materials.

Power and Thermal Design

- Eficiencia DC-DC: Los convertidores buck multiphase para el SoC superan el 90 % de eficiencia; la seleccion de inductores y MOSFET influye tanto en la eficiencia como en la temperatura.

- Secuenciacion de voltaje: El SoC exige una secuencia concreta de encendido, normalmente core, luego I/O y despues memoria. Un secuenciador o PMIC integrado asegura el timing correcto.

- Red de desacoplo: El PDN del SoC necesita capacitancia bulk, con MLCC, polimero o electrolitico, ademas de ceramicos de media y alta frecuencia distribuidos por la red.

- Cobertura de cobre: Maximizar los pours de cobre en capas internas bajo el SoC y las etapas de conversion; 1 oz o 2 oz de cobre en capas de potencia mejoran tanto la capacidad de corriente como la difusion termica.

- Arreglos de vias termicas: Las matrices densas de vias bajo el SoC y los MOSFET de potencia conducen calor a capas internas y cara posterior; las vias rellenas evitan el drenaje de soldadura durante el montaje.

- Interfaz con disipador: Las zonas de pad termico del mainboard acoplan al chasis mediante thermal interface materials; un cobre plano proporciona una interfaz termica uniforme y deben evitarse bultos de via en la zona de contacto.

La relacion entre alimentacion y termica exige comprender tanto los principios de electronica de potencia como las estrategias de gestion termica de la electronica de consumo.

Cost-Optimized Manufacturing for Television Products

Los televisores soportan una presion extrema sobre el costo. El mercado espera TV 4K de gran pantalla a precios que obligan a optimizar de forma agresiva cada parte del diseno. El costo del PCB aporta una parte relevante del BOM total, por eso la eleccion de materiales, el numero de capas y la utilizacion del panel son decisiones criticas. La calidad, sin embargo, no puede recortarse, porque los costos de garantia por fallas en campo superan con rapidez cualquier ahorro de fabricacion.

El equilibrio entre costo y calidad requiere decisiones disciplinadas: usar materiales estandar donde el rendimiento lo permita, minimizar capas sin perder funcionalidad, optimizar el contorno de la placa para aprovechar mejor el panel y disenar pensando en rendimiento de fabricacion. Involucrar pronto al fabricante ayuda a detectar oportunidades de ahorro sin deteriorar la calidad.

Cost Optimization Strategies

- Seleccion de materiales: El FR-4 estandar, Tg 140-150 C, es suficiente para la mayoria de aplicaciones de TV; los materiales de alta velocidad solo deben emplearse donde HDMI 2.1 u otra interfaz critica lo exijan.

- Minimizacion de capas: Una construccion de 6 capas funciona bien en muchas placas principales de TV; 4 capas pueden bastar en disenos menos complejos con un enrutamiento muy afinado.

- Utilizacion del panel: Las placas rectangulares con dimensiones estandarizadas aprovechan mejor el panel de fabricacion; las formas especiales reducen el aprovechamiento y elevan el costo unitario.

- Optimizacion de vias: Las vias pasantes cuestan mucho menos que las blind o buried; conviene disenar through-hole donde sea posible y reservar HDI para las zonas de paso fino realmente necesarias.

- Acabado superficial: HASL sigue siendo la opcion de menor costo para componentes through-hole y de paso grueso; ENIG ofrece una superficie plana para paso fino, pero incrementa el costo.

- Cobertura de prueba: Disenar para test con puntos de prueba accesibles reduce el costo de fixtures y mejora la deteccion de defectos; la prueba flying-probe se adapta bien a volumenes moderados.

Las alianzas en fabricacion de PCB para produccion en volumen permiten optimizar costo mediante eficiencia de proceso y precio por volumen, manteniendo a la vez el control de calidad.

Technical Summary

El diseno de PCB para Smart TV debe equilibrar requisitos avanzados de integridad de senal, como HDMI 2.1 y las interfaces rapidas hacia el panel, frente a objetivos de costo muy exigentes propios de la television de consumo. El exito depende de decisiones arquitectonicas solidas, como la particion de tarjetas, la seleccion de interfaces y la especificacion de materiales, que permitan cumplir prestaciones sin disparar el costo total del sistema.

Entre las decisiones tecnicas mas importantes estan la estrategia de implementacion HDMI, con sus implicaciones en longitud de traza, material y gestion EMI, la compatibilidad de la interfaz de panel, incluyendo protocolo y conector, la arquitectura de potencia en terminos de eficiencia y respuesta transitoria, y la solucion termica, donde el propio PCB participa en la refrigeracion del sistema.

La eleccion del fabricante debe valorar tanto la capacidad tecnica, por ejemplo enrutamiento de alta velocidad y calidad multicapa, como la competitividad de costo. Los volumenes tipicos de TV suelen justificar optimizaciones que no son viables en productos de menor escala. Aun con la presion por costo, los sistemas de calidad siguen siendo imprescindibles, porque los gastos de garantia por defectos de fabricacion superan rapidamente el ahorro de produccion.