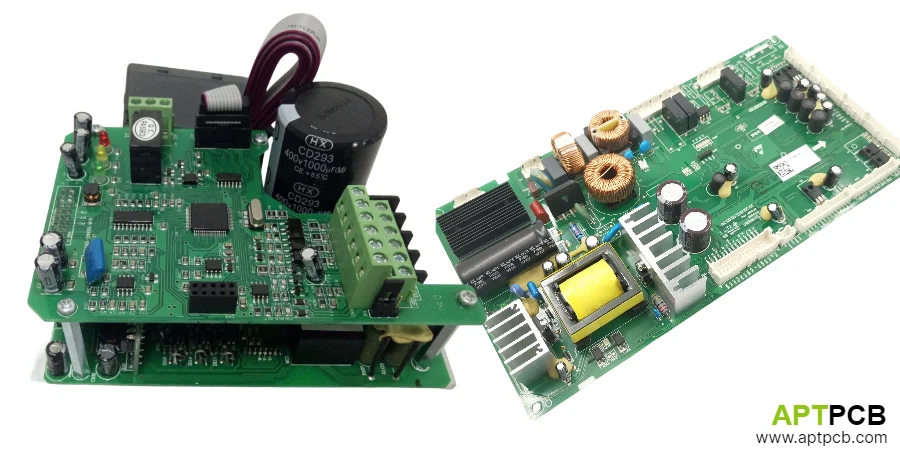

Los variadores de frecuencia convierten una alimentacion CA de frecuencia fija en una salida de frecuencia y voltaje variables para controlar con precision la velocidad del motor. La PCB debe conducir kilovatios a traves de etapas de conmutacion de alto voltaje y, al mismo tiempo, mantener la integridad de señal necesaria para un control exacto. Todo ello debe lograrse dentro de limites EMC que eviten interferencias sobre el equipo cercano.

Esta guia se centra en la ingenieria a nivel de PCB que define la fiabilidad, la eficiencia y la compatibilidad electromagnetica de un VFD en instalaciones industriales.

En esta guia

- Layout de la etapa de potencia y aislamiento

- Diseno del circuito de gate driver

- Sensado de corriente y voltaje

- Arquitectura de filtrado EMC

- Gestion termica para electronica de potencia

- Integracion de la interfaz de control

Layout de la etapa de potencia y aislamiento

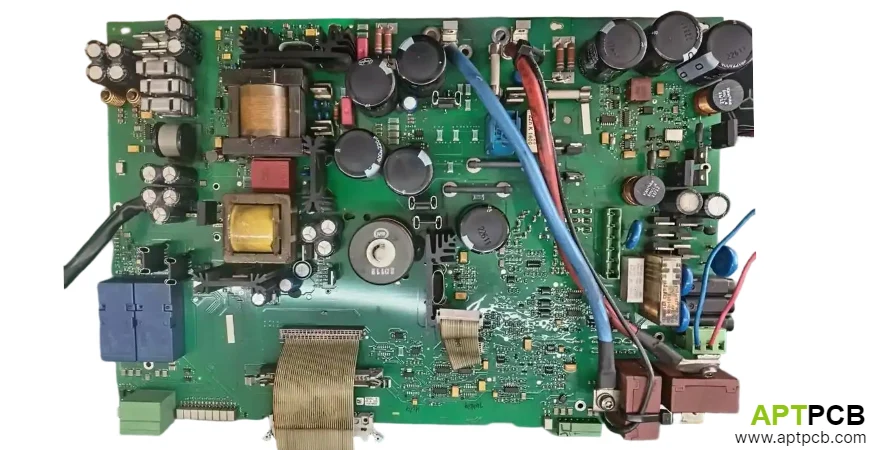

Las etapas de potencia de un VFD conmutan cientos de voltios a frecuencias de kilohercios mediante puentes IGBT o MOSFET. El layout de la PCB afecta de forma directa las perdidas de conmutacion, el estres de voltaje y la generacion de perturbaciones. Un layout deficiente puede elevar las perdidas en un 20 % o mas y provocar fallos EMC que obliguen a redisenar.

La inductancia del lazo de potencia es uno de los parametros mas criticos. Cada nanohenrio de inductancia genera picos de tension durante la conmutacion de corriente segun V = L × di/dt. Si un IGBT conmuta a 5-10 kA/μs, incluso 50 nH de inductancia parasita pueden producir sobretensiones de 250-500 V, con mayor estres para los dispositivos y peor comportamiento EMC.

La construccion de PCB con cobre pesado necesaria para manejar la potencia tambien condiciona el layout. Un cobre de 3-6 oz modifica el grabado y las dimensiones minimas fabricables. Las reglas de diseno deben incorporar estas restricciones sin perder de vista la reduccion de las areas de lazo.

Principios de layout de la etapa de potencia

- Minimizar los lazos: Los condensadores del bus DC deben colocarse junto a los modulos IGBT con conexiones muy cortas.

- Barras laminadas: Los planos de cobre superpuestos para DC+ y DC- ayudan a reducir la inductancia de distribucion.

- Integracion de snubbers: Los snubbers RC o RCD deben ir en los terminales del modulo IGBT y no lejos sobre la tarjeta.

- Barreras de aislamiento: La etapa de potencia de alto voltaje debe mantenerse separada de los circuitos de control con distancias de fuga adecuadas.

- Expansion termica: Los grandes planos de cobre pesado pueden requerir atencion adicional al desajuste de CTE con el sustrato.

- Reparto de corriente: Las etapas de salida en paralelo necesitan trayectorias de impedancia equilibradas para compartir corriente.

Diseno del circuito de gate driver

Los gate drivers convierten las senales de control en pulsos de alta corriente capaces de conmutar rapidamente los IGBT. El circuito debe proporcionar una excitacion de compuerta rapida y limpia manteniendo el aislamiento entre la tierra de control y la etapa de potencia de alto voltaje.

Las exigencias de aislamiento dependen de la topologia de potencia. En inversores trifasicos, los drivers high-side referencian nodos de fase que recorren todo el voltaje del bus DC. El aislamiento debe soportar de forma continua esa tension y tambien los transitorios generados en cada conmutacion. En disenos modernos de alta velocidad esto suele exigir aisladores con CMTI superior a 50 kV/μs.

El stackup de PCB tambien influye de forma directa. Las senales de compuerta contienen flancos rapidos que pueden acoplarse capacitivamente a traves de las barreras de aislamiento. Un buen layout reduce ese acoplamiento parasitario y, al mismo tiempo, cumple las separaciones de seguridad.

Requisitos de layout del gate driver

- Clamp Miller: Un sesgo negativo de compuerta o un clamp Miller ayuda a evitar encendidos espurios causados por acoplamiento dV/dt.

- Conexion Kelvin de fuente: Un retorno de compuerta separado del camino de potencia reduce el efecto de la inductancia parasita sobre el gate drive.

- Alimentacion bootstrap: El condensador bootstrap y el diodo deben dimensionarse para asegurar carga de compuerta incluso en la peor condicion.

- Coincidencia de propagacion: Los retardos entre drivers high-side y low-side deben mantenerse muy proximos para evitar shoot-through.

- Espaciado de aislamiento: Las distancias de fuga y separacion deben cumplir IEC 60664-1 segun tension de trabajo y sobretensiones transitorias.

- Ubicacion de resistencias de compuerta: Las resistencias de gate deben situarse lo mas cerca posible del modulo IGBT para amortiguar con eficacia.

Sensado de corriente y voltaje

Las mediciones precisas de corriente y voltaje permiten algoritmos de control vectorial que mejoran la eficiencia y la respuesta dinamica del motor. La PCB debe transportar esas senales analogicas sensibles por un entorno electrico muy hostil sin degradar la exactitud de medida.

El sensado de corriente suele basarse en sensores Hall o en shunts con amplificadores aislados. Los shunts suelen ofrecer mejor precision y ancho de banda, pero exigen amplificadores capaces de soportar la tension de modo comun del bus DC y sus transitorios. Los sensores Hall aportan aislamiento inherente, aunque introducen errores de ganancia y offset.

El sensado de la tension del bus DC se implementa normalmente con divisores resistivos y realimentacion aislada o con sensores aislados especificos. El circuito debe rechazar el contenido de alta frecuencia procedente de la PWM y seguir con fidelidad las variaciones del bus durante frenado regenerativo o transitorios de carga. Un buen acondicionamiento analogico exige atencion al filtrado y al retorno de tierra.

Reglas de diseno para sensado

- Ubicacion de shunts: Los shunts suelen colocarse en la rama DC- para una medida simple; tres shunts permiten reconstruir las tres fases.

- Filtrado de ruido: Los filtros RC en las senales de medida atenúan el ruido de conmutacion sin recortar en exceso el ancho de banda del control. Son habituales frecuencias de corte entre 1 y 10 kHz.

- Ruteo diferencial: Las senales de sensado deben rutearse como pares diferenciales con planos de referencia para rechazar ruido en modo comun.

- Referencia ADC: Una referencia de tension estable y de bajo ruido es esencial para mantener la precision de conversion.

- Momento de muestreo: El ADC debe muestrear sincronizado con la PWM, durante zonas estables y no en plena transicion de conmutacion.

- Provision para calibracion: Puntos de prueba y coeficientes de calibracion facilitan el ajuste de ganancia y offset en produccion.

Arquitectura de filtrado EMC

Un VFD genera emisiones conducidas y radiadas importantes debido a la PWM de potencia. El filtrado EMC debe atenuarlas hasta cumplir los limites normativos y, al mismo tiempo, soportar las tensiones y corrientes del circuito de potencia. Los componentes del filtro conducen la corriente completa de carga y tambien deben sobrevivir a condiciones de fallo.

El filtrado de entrada reduce las emisiones conducidas sobre la red CA. Los choques de modo comun junto con condensadores X e Y atenúan perturbaciones en la banda de 150 kHz a 30 MHz exigida por la normativa industrial. La frecuencia de corte debe ser lo bastante baja para filtrar con eficacia, pero no tanto como para crear resonancias no deseadas con la impedancia de entrada.

El filtrado de salida, mediante filtros dV/dt o senoidales, protege el aislamiento del motor y reduce corrientes en rodamientos. Estos filtros conducen toda la corriente del motor a frecuencia PWM y disipan una potencia apreciable. El diseno termico del PCB debe contemplar esas perdidas.

Implementacion del filtro EMC

- Dimensionado del choque de modo comun: La inductancia y la corriente de saturacion deben ajustarse a los objetivos de emision conducida.

- Tension nominal de los condensadores: Los condensadores X e Y deben elegirse para los transitorios esperados y con las homologaciones de seguridad necesarias.

- Amortiguacion de resonancias: Resistencias de amortiguacion evitan que el filtro amplifique frecuencias concretas.

- Terminacion de blindajes: Los blindajes de los cables de entrada deben terminar en el chasis o carcasa del filtro, no en el plano de tierra de la PCB.

- Control de dV/dt de salida: Los choques de salida o filtros dV/dt deben limitar la pendiente de tension en bornes del motor a menos de 500 V/μs para cables de mas de 10 m.

- Arquitectura de puesta a tierra: Los circuitos de control necesitan una referencia de tierra en un solo punto, separada de los retornos de potencia de alta corriente.

Gestion termica para electronica de potencia

Las etapas de potencia del VFD disipan una cantidad importante de calor debida a perdidas de conmutacion y conduccion. Un accionamiento de 10 kW con 97 % de eficiencia sigue disipando 300 W internamente. Esa potencia se concentra en semiconductores de potencia que deben mantenerse por debajo de sus limites de temperatura de union para garantizar fiabilidad.

Los semiconductores de potencia suelen montarse sobre disipadores o placas frias mediante materiales de interfaz termica. El diseno termico de la PCB debe conducir el calor desde los encapsulados hasta esas superficies con la menor resistencia posible. Los sustratos PCB de nucleo metalico permiten montaje directo de encapsulados optimizados con resistencias termicas inferiores a 0,5 °C/W.

Los circuitos de gate driver tambien requieren atencion termica. La potencia que disipan sus integrados depende de la carga de compuerta y de la frecuencia de conmutacion. Un driver trabajando a 10 kHz puede disipar 1-2 W, y ese calor debe evacuarse a traves del PCB o por caminos termicos dedicados.

Enfoques de diseno termico

- Montaje de semiconductores: La fijacion directa al disipador mediante material de interfaz termica suele ser la mejor opcion, dejando al PCB como soporte de senal.

- Matrices de vias termicas: Cuando la tarjeta participa en la evacuacion de calor, las matrices de vias bajo los dispositivos reducen la resistencia termica hacia planos internos.

- Seleccion del espesor de cobre: En secciones de potencia suelen ser utiles 3-6 oz de cobre tanto por capacidad de corriente como por reparto termico.

- Coordinacion con el flujo de aire: La posicion de los componentes debe considerar el patron real del aire si se usa refrigeracion forzada.

- Monitorizacion de temperatura: Sensores NTC en disipador y semiconductores ayudan a implementar proteccion termica.

- Criterios de derating: El diseno termico debe verificarse a la temperatura ambiente maxima con margen suficiente para envejecimiento.

Integracion de la interfaz de control

El sistema de control de un VFD debe comunicarse con redes de automatizacion, interfaces de operador y funciones de seguridad. La PCB debe soportar esas interfaces manteniendo el aislamiento respecto a la etapa de potencia de alto voltaje y una buena inmunidad frente al ruido generado por la conmutacion.

Protocolos industriales como PROFINET, EtherCAT o Modbus TCP requieren interfaces Ethernet aisladas con transceptores de grado industrial. Los protocolos mas antiguos suelen necesitar transceptores RS-485 con proteccion industrial contra sobretensiones. Las buenas practicas de PCB para control industrial son clave para mantener comunicaciones fiables en planta.

Las E/S digitales para marcha, paro, referencia de velocidad y estado suelen requerir compatibilidad con 24 VDC y aislamiento respecto a la logica interna. Las entradas analogicas aceptan a menudo 0-10 V o 4-20 mA para consigna de velocidad. Estas senales de bajo nivel son especialmente vulnerables al ruido acoplado desde circuitos de potencia cercanos.

Diseno de la interfaz de control

- Aislamiento Ethernet: Se requiere al menos 1500 Vrms de aislamiento, con ubicacion correcta de transformadores y separaciones de tierra segun el PHY.

- Proteccion de entradas analogicas: Las entradas analogicas deben incluir proteccion ESD, proteccion frente a sobretension y filtrado contra ruido.

- Aislamiento de E/S digitales: Las senales de campo deben llegar a la logica interna a traves de optoacopladores o aisladores digitales.

- Safe Torque Off: La funcion STO debe disponer de entradas de seguridad dedicadas con aislamiento y supervision adecuados.

- Interfaz de encoder: Entradas diferenciales de encoder con terminacion y filtrado mejoran la inmunidad al ruido.

- Puesta a tierra de comunicaciones: La tierra de red debe referenciarse al chasis y no al plano de tierra de la tarjeta de control.

Resumen

El diseno de PCB para VFD combina electronica de potencia, tecnologia de gate drivers, medicion de precision y gestion EMC en un sistema que debe operar con fiabilidad en entornos industriales severos. Las altas tensiones, los flancos de conmutacion rapidos y la fuerte disipacion de potencia crean retos que solo se resuelven con una atencion coordinada entre lo electrico, lo termico y lo mecanico. El resultado depende de entender bien la relacion entre layout de potencia, integridad del gate drive, exactitud de medida y comportamiento EMC.