AI-Native PCB : définition, portée et public visé par ce guide

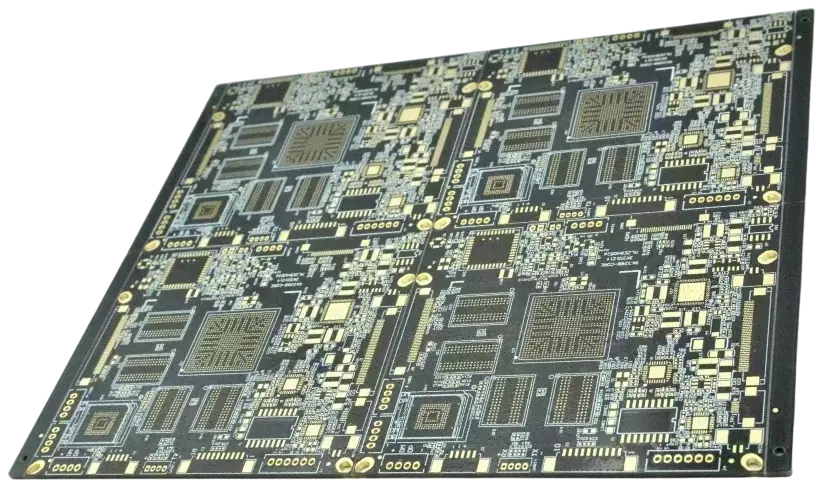

Le terme AI-Native PCB fait référence aux cartes de circuits imprimés haute performance spécifiquement conçues pour prendre en charge les écosystèmes matériels d'Intelligence Artificielle, y compris les serveurs d'entraînement, les accélérateurs d'inférence et les nœuds de calcul en périphérie. Contrairement à l'électronique standard, ces cartes doivent gérer simultanément un débit de données massif, des charges thermiques extrêmes et une latence de signal ultra-faible. À mesure que l'infrastructure d'IA converge avec les télécommunications, les exigences pour ces cartes chevauchent souvent celles des infrastructures haute fréquence comme les modules 5G AAU PCB (Unité d'Antenne Active) et 5G ADC PCB (Convertisseur Analogique-Numérique), créant un défi de fabrication complexe qui exige une précision au-delà des standards IPC Class 2.

Ce guide est conçu pour les ingénieurs hardware, les responsables NPI et les responsables des achats qui passent de l'électronique numérique standard au matériel de calcul haute performance (HPC). Il dépasse le bruit marketing pour se concentrer sur les réalités physiques de la fabrication : sélection des matériaux, intégrité de l'empilement et les étapes de validation spécifiques requises pour prévenir les défaillances sur le terrain dans les clusters d'IA coûteux. Chez APTPCB (APTPCB PCB Factory), nous avons observé que la cause principale des retards de projet dans ce secteur n'est pas la capacité de conception, mais un décalage entre l'intention de conception et la réalité de la fabrication. Ce guide sert de cadre de décision pour combler cet écart, garantissant que vos spécifications se traduisent par du matériel fiable.

Quand utiliser un PCB natif IA (et quand une approche standard est préférable)

Comprendre la portée définie ci-dessus nous permet de déterminer exactement quand le coût et la complexité d'un PCB natif IA sont justifiés par rapport à quand une conception standard à haute vitesse suffit.

Utilisez une approche native IA lorsque :

- Les vitesses de signal dépassent 56 Gbit/s PAM4 : Le FR4 standard ne peut pas supporter l'intégrité du signal requise pour les interconnexions IA modernes sans une atténuation massive.

- Le nombre de couches dépasse 18 couches : Les accélérateurs IA nécessitent souvent un routage haute densité et de vastes plans d'alimentation que les presses de laminage standard ne peuvent pas aligner avec précision sans outillage spécialisé.

- La densité thermique est critique : Si votre GPU ou TPU génère de la chaleur nécessitant une compatibilité avec le refroidissement liquide ou par immersion, les matériaux de masque de soudure et de substrat standard peuvent se dégrader.

- Intégration avec l'infrastructure 5G : Les conceptions intégrant la technologie 5G AAU PCB pour l'IA en périphérie nécessitent des capacités de signaux mixtes (RF + Numérique) qui exigent des empilements hybrides.

Restez sur un PCB haute vitesse standard lorsque :

- Appareils IoT Edge : L'inférence simple sur des microcontrôleurs (par exemple, la reconnaissance vocale) nécessite rarement des matériaux exotiques ; le FR4 standard avec impédance contrôlée est généralement suffisant.

- Interfaces héritées : Si la carte gère principalement PCIe Gen 3 ou inférieur, le surcoût des matériaux à très faible perte de qualité IA est inutile.

- Prototypage logique uniquement : Si vous validez la logique à basse vitesse avant de passer à pleine vitesse, les matériaux standard peuvent permettre d'économiser des coûts significatifs lors des premières révisions.

Spécifications de PCB natifs pour l'IA (matériaux, empilement, tolérances)

Une fois que vous avez déterminé que votre projet nécessite un PCB natif pour l'IA, l'étape suivante consiste à définir les spécifications rigides qui régiront le processus de fabrication.

- Matériaux de base (stratifiés) :

- Exigence : Les matériaux à très faible perte sont non négociables.

- Cible : Df (Facteur de Dissipation) < 0,002 à 10 GHz ; Dk (Constante Diélectrique) < 3,6.

- Exemples : Panasonic Megtron 7/8, Isola Tachyon 100G ou série Rogers RO3000 pour les sections RF hybrides.

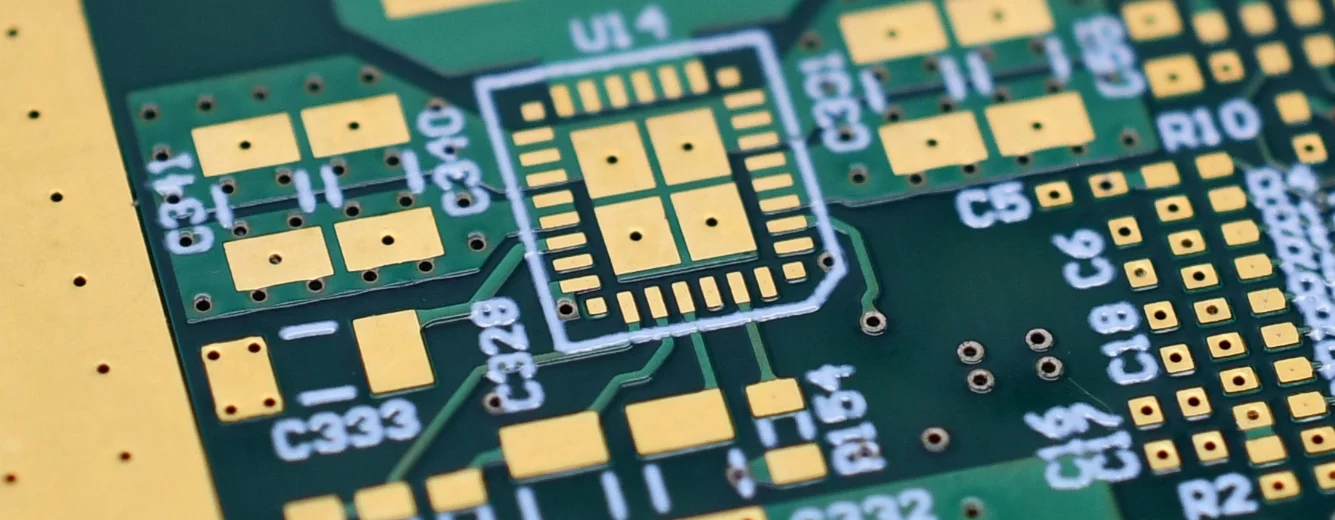

- Rugosité de la feuille de cuivre :

- Exigence : Cuivre HVLP (Hyper Very Low Profile) ou HVLP2.

- Cible : Rugosité de surface (Rz) < 1,5 µm pour minimiser les pertes par effet de peau aux hautes fréquences.

- Nombre de couches et empilement :

- Gamme : Généralement 20 à 40+ couches pour les cartes de qualité serveur.

- Structure : Cycles de laminage multiples (3+) ; nécessite souvent des interconnexions haute densité (HDI) "tout-couche" ou des interconnexions sur chaque couche (ELIC).

- Perçage et Vias :

- Contre-perçage : Obligatoire pour les couches de signaux à haute vitesse afin d'éliminer les talons de via.

- Tolérance : La tolérance de profondeur du contre-perçage doit être contrôlée entre ±0,05 mm et ±0,10 mm pour préserver l'intégrité du signal sans couper les couches internes.

- Rapport d'aspect : Une capacité de placage à rapport d'aspect élevé (15:1 à 20:1) est requise pour les cartes épaisses (3,0 mm+).

- Contrôle d'impédance :

- Tolérance : Contrôle strict de ±5% ou ±7% (la norme est ±10%) sur les paires asymétriques et différentielles.

- Test : Test TDR (réflectométrie dans le domaine temporel) à 100% sur les coupons et les cartes de production.

- Finition de surface :

- Préféré : ENIG (Or par immersion sur nickel chimique) ou ENEPIG pour le support de liaison filaire.

- Alternative : Argent par immersion pour une perte d'insertion plus faible, bien que la durée de conservation soit plus courte.

- Fiabilité thermique :

- Tg (Température de transition vitreuse) : > 180°C (Tg élevée).

- Td (Température de décomposition) : > 350°C pour résister à plusieurs cycles de refusion lors de l'assemblage de grands composants BGA.

- Précision d'enregistrement :

- Cible : Enregistrement couche à couche de ±2-3 mils (50-75µm) pour assurer l'alignement des pastilles avec les vias dans les empilements multicouches.

- Propreté :

- Contamination ionique : < 0,65µg/cm² équivalent NaCl, critique pour prévenir la migration électrochimique dans les environnements de centres de données haute tension.

Risques de fabrication des PCB natifs de l'IA (causes profondes et prévention)

Une fois les spécifications définies, l'accent est mis sur l'atténuation des modes de défaillance spécifiques associés à la fabrication de conceptions de PCB natifs de l'IA haute performance.

- Croissance de filaments anodiques conducteurs (CAF)

- Cause profonde : Biais de haute tension entre des vias étroitement espacés combiné à l'absorption d'humidité dans le système de résine.

- Détection : Tests CAF (plus de 1000 heures à haute température/humidité).

- Prévention : Utiliser des matériaux résistants au CAF (tissage de verre étalé) et maximiser l'espacement via-à-via lorsque cela est possible.

- Cratérisation des plots

- Cause profonde : Les matériaux stratifiés cassants (courants dans les matériaux haute vitesse) se fracturent sous la contrainte mécanique de la dilatation thermique des grands BGA.

- Détection : Microscopie acoustique ou tests de teinture et de levage pendant la validation.

- Prévention : Utiliser des stratifiés renforcés de résine et le collage d'angle/sous-remplissage sur les grands BGA.

- Perte d'intégrité du signal due à la variation de gravure

- Cause profonde : La sur-gravure ou la sous-gravure des traces trapézoïdales modifie le profil d'impédance.

- Détection : Analyse en coupe transversale et tests TDR.

- Prévention : Spécifier des facteurs de "compensation de gravure" dans l'ingénierie CAM et utiliser des équipements de gravure sous vide.

- Délaminage pendant le refusion

- Cause première: L'humidité piégée dans les cartes épaisses se vaporise lors des températures de refusion sans plomb (260°C).

- Détection: SAM (Microscopie Acoustique à Balayage) après simulation de refusion.

- Prévention: Protocoles de cuisson stricts (4-8 heures) avant l'assemblage et emballage barrière contre l'humidité (MBB).

- Résidus de talon de contre-perçage

- Cause première: L'usure du foret ou une erreur de calcul de profondeur laisse un petit talon conducteur.

- Détection: Inspection aux rayons X ou analyse TDR spécifique recherchant des anomalies de réflexion.

- Prévention: Vérifications optiques automatisées des forets et vérification aux rayons X du premier article.

- Déformation / Cambrure et Torsion

- Cause première: Distribution asymétrique du cuivre ou empilement déséquilibré dans les cartes grand format.

- Détection: Mesure par Moiré d'ombre.

- Prévention: répartition du cuivre strictement équilibrée sur toutes les couches ; utilisation de matériaux à faible CTE.

- Vides de placage dans les vias à rapport d'aspect élevé

- Cause première: La solution de placage ne circule pas efficacement dans les trous profonds et étroits (par exemple, carte de 3 mm d'épaisseur avec des vias de 0,2 mm).

- Détection: Coupe transversale et test de choc thermique.

- Prévention: Technologie de placage par impulsions et limites de conception du rapport d'aspect (maintenir en dessous de 15:1 si possible).

- Discontinuité d'impédance aux transitions de couche

- Cause première: Désalignement entre le pad de via et le dégagement du plan de référence.

- Détection: Test VNA (Analyseur de Réseau Vectoriel).

- Prévention: Imagerie directe par laser (LDI) pour les couches internes afin d'assurer un alignement précis.

Validation et acceptation des PCB natifs IA (tests et critères de réussite)

Pour s'assurer que les risques ci-dessus sont gérés, un plan de validation robuste doit être exécuté avant la production de masse de tout PCB natif IA.

- Test de stress d'interconnexion (IST):

- Objectif: Vérifier la fiabilité des vias sous cyclage thermique.

- Méthode: Soumettre les coupons à des cycles répétés de température ambiante à 150°C (ou plus).

- Acceptation: Aucune augmentation de résistance > 10% après 500 cycles.

- Vérification de l'intégrité du signal (paramètres S):

- Objectif: Confirmer que la perte d'insertion et la perte de retour correspondent aux modèles de simulation.

- Méthode: Mesure VNA jusqu'à 28GHz ou 56GHz.

- Acceptation: Déviation de la perte d'insertion < 1dB/pouce par rapport à la simulation; Perte de retour < -15dB.

- Test Hipot (haut potentiel):

- Objectif: Assurer l'isolation entre les rails d'alimentation haute tension (courant dans l'alimentation des serveurs IA).

- Méthode: Appliquer une haute tension (par exemple, 500V-1000V) entre les réseaux.

- Acceptation: Courant de fuite < 1mA; pas de claquage.

- Test de choc thermique:

- Objectif: Tester la force de liaison du matériau et l'intégrité du placage des vias.

- Méthode: Transfert liquide-liquide de -55°C à +125°C.

- Acceptation: Pas de délaminage, de cloques ou de circuits ouverts après 100 cycles.

- Test de soudabilité:

- Objectif: S'assurer que la finition de surface accepte correctement la soudure.

- Méthode : IPC J-STD-003 (Dip and Look ou Équilibre de mouillage).

- Acceptation : > 95% de couverture ; temps de mouillage < 2 secondes.

- Test de contamination ionique (ROSE) :

- Objectif : Vérifier la propreté de la carte.

- Méthode : IPC-TM-650 2.3.25.

- Acceptation : < 1,56 µg/cm² équivalent NaCl (souvent plus strict pour l'IA : < 0,65).

- Résistance au pelage du cuivre :

- Objectif : Vérifier l'adhérence du cuivre au diélectrique.

- Méthode : Test de pelage mécanique.

- Acceptation : > 0,8 N/mm (ou selon la spécification de la fiche technique du matériau).

- Stabilité dimensionnelle :

- Objectif : S'assurer que la carte s'adapte au châssis et s'aligne avec les prises.

- Méthode : MMT (Machine à Mesurer Tridimensionnelle).

- Acceptation : Tolérances de ±0,1 mm pour le contour ; Déformation < 0,75%.

Liste de contrôle de qualification des fournisseurs de PCB natifs pour l'IA (RFQ, audit, traçabilité)

Lors de la sélection d'un partenaire comme APTPCB, utilisez cette liste de contrôle pour vous assurer que l'usine est réellement capable de gérer les exigences des PCB natifs pour l'IA plutôt que de se limiter à la production standard.

Groupe 1 : Entrées RFQ (Ce que vous devez fournir)

- Fichiers Gerber X2 ou ODB++ complets (préférés pour les données complexes).

- Netlist IPC-356 pour la vérification des tests électriques.

- Dessin d'empilement détaillé spécifiant les types de matériaux (marque/série) et l'épaisseur diélectrique.

- Tableau d'impédance référençant les couches spécifiques et les largeurs de trace.

- Plan de perçage distinguant les trous traversants, les vias borgnes/enterrés et les backdrills.

- Plan de fabrication avec des notes sur les exigences de Classe 3 (le cas échéant).

- Exigences de panelisation (si l'assemblage nécessite des rails/fiducials spécifiques).

- Fichier Readme mettant en évidence les nets critiques (par exemple, "Ne pas modifier le routage sur le Net X").

Groupe 2 : Preuve de Capacité (Ce que le fournisseur doit montrer)

- Liste d'équipements : Machines d'imagerie directe laser (LDI) pour les couches internes.

- Liste d'équipements : Lignes de gravure sous vide (pour les lignes fines < 3 mil).

- Liste d'équipements : Machines de backdrilling automatisées avec détection de contrôle de profondeur.

- Expérience : Études de cas ou échantillons anonymisés de cartes à 20+ couches.

- Stock de matériaux : Preuve d'inventaire ou chaîne d'approvisionnement directe pour les matériaux Megtron/Rogers.

- Capacité HDI : Capacité démontrée pour les microvias empilés (par exemple, 3+N+3).

Groupe 3 : Système Qualité & Traçabilité

- Certifications : ISO 9001 (Général), IATF 16949 (si IA automobile), UL 94V-0.

- Traçabilité : Peuvent-ils tracer une carte spécifique jusqu'au lot de matière première et au cycle de presse de lamination ?

- IQC (Contrôle Qualité Entrant) : Procédure de vérification des propriétés des matériaux pré-imprégnés et du cœur.

- AOI (Inspection Optique Automatisée) : L'AOI est-elle effectuée sur chaque couche interne ?

- Coupe transversale : Fréquence de l'analyse par micro-section par lot de production.

Groupe 4 : Contrôle des Changements & Livraison

- Politique PCN (Product Change Notification) : Engagement à notifier avant de changer de matériaux ou de sous-fournisseurs.

- Processus EQ (Engineering Question) : Comment ils gèrent les divergences DFM (rapport formel vs. e-mail).

- Emballage : Sacs barrière contre l'humidité (MBB) avec cartes indicatrices d'humidité (HIC) et déshydratant.

- Logistique : Expérience dans l'expédition internationale de cargaisons lourdes en cuivre/de poids important.

Comment choisir une carte PCB native IA (compromis et règles de décision)

Chaque décision d'ingénierie implique un compromis. Voici comment gérer les conflits les plus courants lors de la spécification d'architectures de PCB natives IA.

- Coût des matériaux vs. Intégrité du signal

- Règle : Si la longueur totale de votre trace est courte (< 5 pouces) et que la vitesse est < 25 Gbit/s, vous pouvez utiliser un matériau "Mid-Loss" (par exemple, Isola FR408HR).

- Règle : Si la longueur de la trace est longue ou que la vitesse est > 25 Gbit/s, vous devez choisir un matériau "Ultra-Low Loss" (par exemple, Megtron 7). Le coût d'atténuation du signal du FR4 nécessitera des refontes coûteuses.

- HDI vs. Trous traversants

- Règle : Si vous avez des composants BGA avec un pas < 0,65 mm, vous devez utiliser le HDI (Microvias).

- Règle : Si le pas BGA est > 0,8 mm, optez pour les trous traversants ou de simples vias borgnes pour réduire le coût de la carte de 30 à 50 %.

- Backdrilling vs. Vias borgnes

- Règle : Si vous devez supprimer des stubs sur une carte épaisse (3 mm+), le backdrilling est généralement plus rentable que la lamination séquentielle (vias borgnes) pour une simple suppression de stub.

- Règle : Si vous avez besoin d'espace de routage sur les couches externes au-dessus du via, utilisez des vias borgnes (Blind Vias).

- Finition de surface : ENIG vs. OSP

- Règle : Si la fiabilité et la durée de conservation sont primordiales (Serveur/Centre de données), choisissez ENIG.

- Règle : Si l'intégrité du signal à des fréquences extrêmement élevées (> 50 GHz) est la seule priorité, l'OSP (Organic Solderability Preservative) n'a pas de couche de nickel susceptible de provoquer des pertes magnétiques, mais l'assemblage doit avoir lieu immédiatement.

- Épaisseur de la carte vs. Rapport d'aspect

- Règle : Si la carte doit être épaisse (pour la rigidité/les couches), vous devez augmenter le diamètre du via pour maintenir un rapport d'aspect de placage < 15:1.

- Règle : Si la taille du via est fixe (petite), vous devez réduire l'épaisseur de la carte ou accepter une perte de rendement/coût plus élevée.

Questions fréquentes (FAQ) sur les PCB natifs de l'IA (coût, délai, fichiers DFM, matériaux, tests)

Q : Comment le coût des PCB natifs de l'IA se compare-t-il à celui des PCB standard ? R : Attendez-vous à des coûts 3 à 10 fois plus élevés que ceux des cartes FR4 standard. Cela est dû aux matières premières coûteuses (Megtron/Rogers peuvent coûter 5 fois le prix du FR4), aux processus à faible rendement (HDI, défonçage arrière) et aux exigences de test étendues.

Q : Quel est le délai typique pour les prototypes de PCB natifs de l'IA ? R : Le délai standard est de 15 à 20 jours ouvrables en raison des cycles de laminage séquentiels.

- Accéléré : Peut être réduit à 10-12 jours avec des frais supplémentaires.

- Retard de matériel : Vérifiez toujours le stock pour les matériaux exotiques ; la commande de matériaux peut ajouter 2 à 4 semaines s'ils ne sont pas en stock. Q: Quels fichiers DFM spécifiques sont nécessaires pour la modélisation d'impédance de PCB natifs IA? R: Vous devez fournir un fichier d'empilement qui indique explicitement la constante diélectrique (Dk) et le facteur de dissipation (Df) à la fréquence de fonctionnement (par exemple, 10 GHz), et non seulement la valeur à 1 MHz trouvée dans les fiches techniques génériques.

Q: Pouvons-nous mélanger des matériaux (empilement hybride) pour réduire les coûts? R: Oui, c'est courant dans les conceptions de PCB AAU 5G.

- Méthode: Utiliser un matériau haute fréquence coûteux pour les couches de signal et du FR4 moins cher pour les couches d'alimentation/masse/mécaniques.

- Risque: Un désalignement du CTE entre les matériaux peut provoquer un gauchissement; cela nécessite une validation technique minutieuse.

Q: Quels sont les critères d'acceptation pour la profondeur de défonçage? R: La norme industrielle est généralement "Ne doit pas couper le cuivre de la couche cible" et "Longueur de stub restante < 10 mils (0,25 mm)". Des tolérances plus strictes (par exemple, < 6 mils) augmentent les coûts et le risque de circuits ouverts.

Q: Comment testez-vous la fiabilité dans les sections de PCB ADC 5G? R: Au-delà du test E standard, nous recommandons des tests spécifiques de plancher de bruit et des tests d'intermodulation passive (PIM) si l'ADC est intégré à des lignes de transmission RF.

Q: Pourquoi l'équilibrage du cuivre ("thieving") est-il critique pour ces cartes? R: Les cartes IA sont souvent grandes. Une distribution inégale du cuivre entraîne un "gauchissement et une torsion" pendant la refusion, ce qui provoque des défaillances des joints de soudure BGA. L'équilibrage automatique du cuivre est ajouté aux zones vides pour équilibrer les contraintes.

Q: Dois-je spécifier la classe IPC 3 pour le matériel IA? R: Bien que la classe IPC 2 soit standard, la plupart des propriétaires d'infrastructures d'IA spécifient « IPC Classe 2 avec les exigences de placage de la Classe 3 » (c'est-à-dire du cuivre plus épais dans les vias) pour assurer une fiabilité à long terme sans le coût/la charge d'inspection complets de la Classe 3.

Ressources pour les PCB natifs de l'IA (pages et outils connexes)

- Fabrication de PCB haute vitesse: Plongez en profondeur dans les techniques de fabrication spécifiques pour une intégrité du signal > 25 Gbit/s.

- PCB pour serveurs et centres de données: Comprenez les normes de fiabilité spécifiques requises pour les environnements d'exploitation 24h/24 et 7j/7.

- Capacités de PCB HDI: Découvrez les structures de microvias et la stratification séquentielle nécessaires pour les puces d'IA haute densité.

- Calculateur d'impédance: Un outil pour estimer la largeur et l'espacement des pistes avant de soumettre votre empilement final.

- Matériaux de PCB Panasonic Megtron: Spécifications pour le matériau à faible perte le plus courant utilisé dans les accélérateurs d'IA.

- Directives DFM: Règles de conception essentielles pour garantir que votre carte IA est fabricable à grande échelle.

Demander un devis pour un PCB natif de l'IA (examen DFM + prix)

Prêt à passer de la conception à la validation ? Chez APTPCB, nous fournissons une revue DFM complète avec votre devis pour identifier les risques potentiels d'intégrité du signal ou d'empilement avant le début de la production.

Pour obtenir un devis précis et une DFM, veuillez préparer :

- Fichiers Gerber/ODB++ : Jeu de données complet.

- Empilement et Impédance : Nombre de couches souhaité et impédance cible.

- Spécifications Matérielles : Exigences spécifiques du stratifié (par exemple, "Megtron 7 ou équivalent").

- Volume : Quantité de prototype vs. Objectifs de production de masse.

Cliquez ici pour demander un devis et une revue DFM

Conclusion finale : Prochaines étapes pour les PCB AI-Native

Le déploiement réussi d'un PCB AI-Native nécessite un changement de mentalité, passant de la "connexion de composants" à la "conception d'un système de ligne de transmission". En définissant strictement vos spécifications matérielles, en comprenant les risques de la construction multicouche et en validant la capacité de votre fournisseur à gérer le backdrilling et le HDI, vous pouvez sécuriser la fondation matérielle sur laquelle vos algorithmes d'IA s'appuient. Que vous construisiez un PCB 5G AAU ou un cluster d'entraînement massif, la physique de la fabrication reste le gardien ultime de la performance.